i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления нагрузкой коммутационной среды мультипроцессорной системы | 1989 |

|

SU1730634A1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| Пакетная сеть для мультипроцессорных систем и способ коммутации с использованием такой сети | 2018 |

|

RU2703231C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| Модуль входов и выходов на сдвиговом регистре | 2024 |

|

RU2832405C1 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении коммутационных сетей мультипроцессорных вычислительных систем. Целью изобретения является повышение производительности. Устройство содержит группу блоков 1 коммутации. Блок 1 коммутации имеет информационные вход и выход 2, аналоговые выходы 3, 4, объединенные при помощи резисторов 5, выход 6 и вход 7 процессорного модуля, вход 8 запроса, выход 9 подтверждения. 3 ил.

о о ел

CJ 00 СА

Изобретение относится к вычислительной технике и может быть использовано при построении коммутационных сетей мультипроцессорных вычислительных систем.

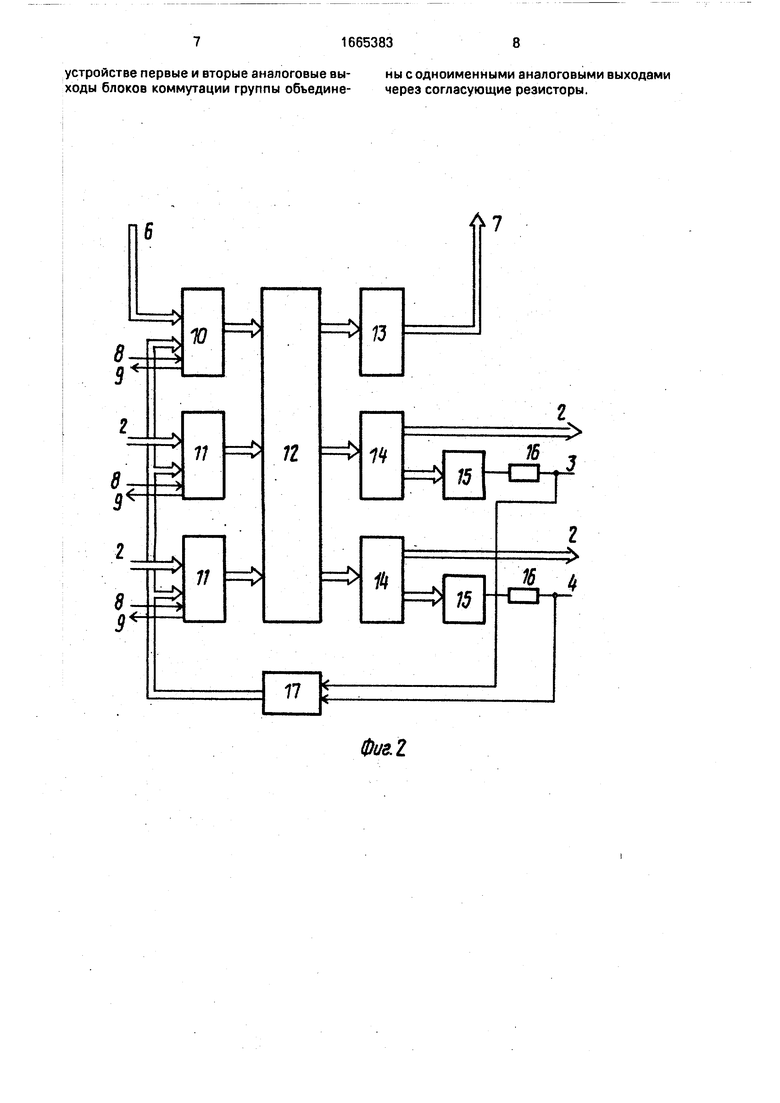

Целью изобретения является повышение быстродействия коммутационной сети. На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема узлов коммутации; на фиг.З - пример выполнения входных интерфейсов и переключат эля.

Устройство (фиг.1) содержит группу блоков 1 коммутации, соединенных между собой информационными входами-выходами 2, каждый блок 1 коммутации содержит первый и второй аналоговые выходы 3 и 4, при этом первые аналоговые выходы 3 блоков коммутации объединяюся при помощи резисторов 5 между собой по горизонтали, а вторые аналоговые выходы 4 - по вертикали.

Блок 1 коммутации имеет выход 6 и вход 7 процессорного модуля, а также вход 8 запроса и выход 9 подтверждения.

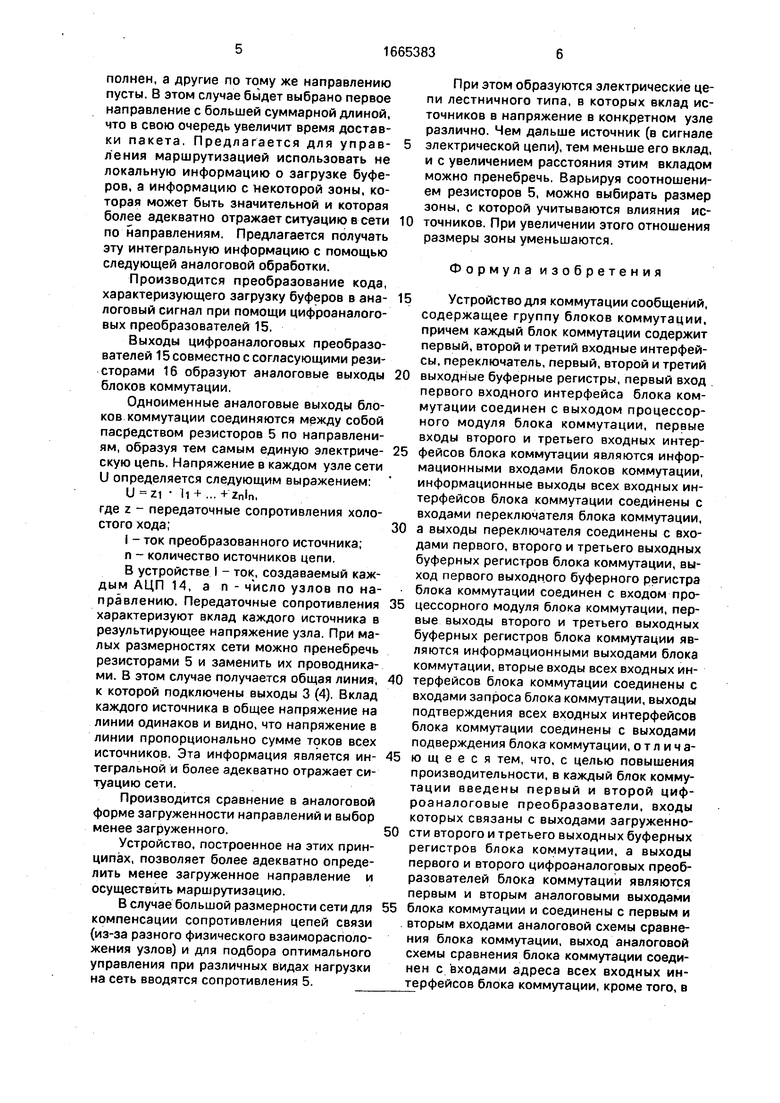

Каждый блок 1 коммутации (фиг.2) содержит первый 10, второй и третий 11 входные интерфейсы, переключатель 12, первый 13, второй и третий 14 выходные буферные регистры, первый и второй цифроаналоговые преобразователи 15, выходы которых через согласующие резисторы 16 соединены с входами аналоговой схемы 17 сравнения.

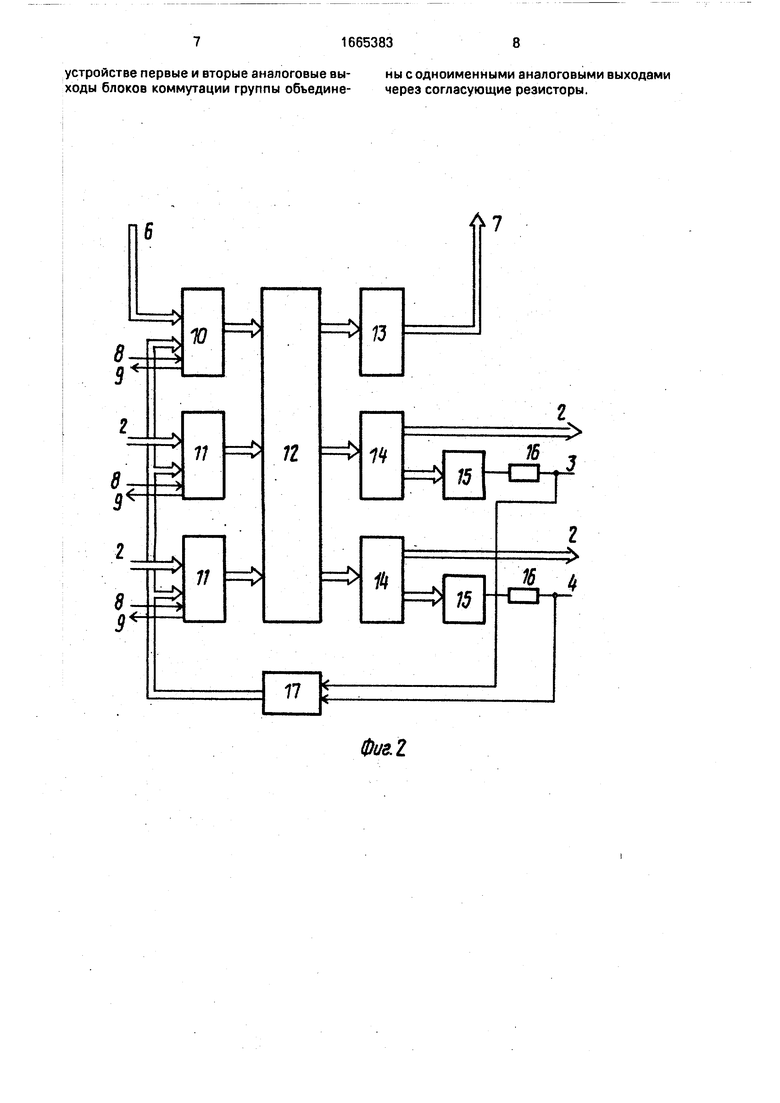

Каждый входной интерфейс 10, 11 (фиг.З) содержит блок 18 управления, дешифратор 19 адреса и входной регистр 20. Переключатель 12 содержит два арбитра 21 выходных каналов, четыре ключа 22, два элемента ИЛИ 23.

Устройство работает следующим образом.

Для описания работы устройства вводятся следующие обозначения: PQin - запрос источника на вывод информации (вход 8); AQin - подтверждение приемника о получении информации (выход 9); PQa - запрос к арбитру (от блока 18); А0а - подтверждение арбитра (от блока 21); PQout - запрос на запись в выходной регистр.

Обмен данных между процессорными модулями, связанными с каждым узлом коммутации, происходит при использовании пакетов, перемещающихся по двум направлениям: вертикальном и горизонтальном. Пакет состоит из двух частей: адресной и операционной. Адресная часть представляет собой код ПМ, кому адресован пакет, а операционная - собственно информацию. Пакет с выхода буферного регистра 14 смежного узла поступает во вход

ной интерфейс, при этом активизируется линия PQin и выход 9. Блок 18 управления согласно диаграмме переходов производит запись во входной регис гр 20. Далее производится дешифрация адреса и формируется запрос к одному из арбитров 21 выходного канала (вертикального, горизонтального или канала ПМ). Если адресная часть пакета совпадает с кодом текущего блока 1, то фор0 мируется запрос к арбитру канала ПМ. Каждый выходной канал имеет свой арбитр 21. Арбитр 21 воспринимает запросы от входных интерфейсов и в зависимости от приоритета запросов (приоритет запросов

5 записям в ПЗУ, на котором выполняется арбитр) выдает подтверждение соответствующему входному интерфейсу, при этом открывается соответствующий ключ 22 и информация с выхода регистра 20 канала, ко0 торому дано подтверждение, поступает на вход выходного регистра 14 (13), Блок 18 управления выставляет сигнал PQout, который через элемент ИЛИ 23 производит запись пакета в соответствующий выходной

5 регистр 14. Элемент ИЛИ 23 объединяет запросы PQout от входных интерфейсов 11 (10). Адрес ПМ однозначно определяет положение ПМ в матрице, т.е. номер по вертикали (строка) и номер по горизонтали

0 (столбец). Если адресная часть пакета не совпадает с адресом узла, где обрабатывается пакет по одной координате (т.е. по строке или столбцу), то запрашивается выходной канал, по которому не происходит

5 совпадения. Например, если не совпадает столбец, то запрашивается горизонтальный выходной канал и пакет движется вдоль строки, до совпадения по столбцу. Если нет совпадения ни по столбцу, ни по строке, то

0 выбирается канал в зависимости от выходных сигналов схемы 17 сравнения. Схема 17 сравнения сравнивает загруженность направлений по вертикали и горизонтали и, следовательно, маршрут будет выбираться

5 по направлению с меньшей загрузкой. Такое построение коммутационного узла является известным и оно реализовано в известном устройстве, в котором также реализован алгоритм выбора канала на ос0 новании загруженности соседних буферов. Такое управление маршрутизацией является локальным. Оно требует малых аппаратных затрат, но реализуется на основе информации о загрузке соседних узлов, ко5 торая не отражает ситуацию во всей сети (т.е. по всему направлению). При этом возможна такая ситуадия, когда по одному направлению буфер ближайшего узла пуст, а другие буферы заполнены, в то же время ближайший буфер другого направления заполней, а другие по тому же направлению пусты, В этом случае быдет выбрано первое направление с большей суммарной длиной, что в свою очередь увеличит время доставки пакета. Предлагается для управления маршрутизацией использовать не локальную информацию о загрузке буферов, а информацию с некоторой зоны, которая может быть значительной и которая более адекватно отражает ситуацию в сети по направлениям. Предлагается получать эту интегральную информацию с помощью следующей аналоговой обработки.

Производится преобразование кода, характеризующего загрузку буферов в аналоговый сигнал при помощи цифроаналого- вых преобразователей 15.

Выходы цифроаналоговых преобразователей 15 совместно с согласующими резисторами 16 образуют аналоговые выходы блоков коммутации.

Одноименные аналоговые выходы блоков коммутации соединяются между собой пасредством резисторов 5 по направлениям, образуя тем самым единую электрическую цепь. Напряжение в каждом узле сети U определяется следующим выражением:

U Z1 И + ...+Znin,

где z - передаточные сопротивления холостого хода;

I - ток преобразованного источника;

п - количество источников цепи.

В устройстве I - ток, создаваемый каждым АЦП 14, an- число узлов по направлению. Передаточные сопротивления характеризуют вклад каждого источника в результирующее напряжение узла. При малых размерностях сети можно пренебречь резисторами 5 и заменить их проводниками. В этом случае получается общая линия, к которой подключены выходы 3 (4). Вклад каждого источника в общее напряжение на линии одинаков и видно, что напряжение в линии пропорционально сумме токов всех источников. Эта информация является интегральной и более адекватно отражает ситуацию сети.

Производится сравнение в аналоговой форме загруженности направлений и выбор менее загруженного.

Устройство, построенное на этих принципах, позволяет более адекватно определить менее загруженное направление и осуществить маршрутизацию.

В случае большой размерности сети для компенсации сопротивления цепей связи (из-за разного физического взаиморасположения узлов) и для подбора оптимального управления при различных видах нагрузки на сеть вводятся сопротивления 5.

При этом образуются электрические цепи лестничного типа, в которых вклад источников в напряжение в конкретном узле различно. Чем дальше источник (в сигнале

5 электрической цепи), тем меньше его вклад, и с увеличением расстояния этим вкладом можно пренебречь. Варьируя соотношением резисторов 5, можно выбирать размер зоны, с которой учитываются влияния ис10 точников. При увеличении этого отношения размеры зоны уменьшаются.

Формула изобретения

15 Устройство для коммутации сообщений, содержащее группу блоков коммутации, причем каждый блок коммутации содержит первый, второй и третий входные интерфейсы, переключатель, первый, второй и третий

0 выходные буферные регистры, первый вход первого входного интерфейса блока коммутации соединен с выходом процессорного модуля блока коммутации, первые входы второго и третьего входных интер5 фейсов блока коммутации являются информационными входами блоков коммутации, информационные выходы всех входных интерфейсов блока коммутации соединены с входами переключателя блока коммутации,

0 а выходы переключателя соединены с входами первого, второго и третьего выходных буферных регистров блока коммутации, выход первого выходного буферного регистра блока коммутации соединен с входом про5 цессорного модуля блока коммутации, первые выходы второго и третьего выходных буферных регистров блока коммутации являются информационными выходами блока коммутации, вторые входы всех входных ин0 терфейсов блока коммутации соединены с входами запроса блока коммутации, выходы подтверждения всех входных интерфейсов блока коммутации соединены с выходами подверждения блока коммутации, о т л и ч а5 ю щ е е с я тем, что, с целью повышения производительности, в каждый блок коммутации введены первый и второй циф- роаналоговые преобразователи, входы которых связаны с выходами загруженно0 сти второго и третьего выходных буферных регистров блока коммутации, а выходы первого и второго цифроаналоговых преобразователей блока коммутации являются первым и вторым аналоговыми выходами

5 блока коммутации и соединены с первым и вторым входами аналоговой схемы сравнения блока коммутации, выход аналоговой схемы сравнения блока коммутации соединен с входами адреса всех входных интерфейсов блока коммутации, кроме того, в

устройстве первые и вторые аналоговые вы- ны с одноименными аналоговыми выходами ходы блоков коммутации группы объедине- через согласующие резисторы.

Фиг. 2

Фиа.З

| Богуславский Л.Б | |||

| Управление потоками данных в сетях ЭВМ | |||

| - М,: Энергоиэдат, 1984,с.111 | |||

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1991-07-23—Публикация

1989-06-27—Подача