СО

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коммутации сообщений | 1989 |

|

SU1665383A1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Пакетная сеть для мультипроцессорных систем и способ коммутации с использованием такой сети | 2018 |

|

RU2703231C1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| УСТАНОВЛЕНИЕ ТРАКТОВ ВЫЗОВОВ СЕТЕЙ СВЯЗИ В ШИРОКОПОЛОСНЫХ СЕТЯХ СВЯЗИ | 1993 |

|

RU2117403C1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

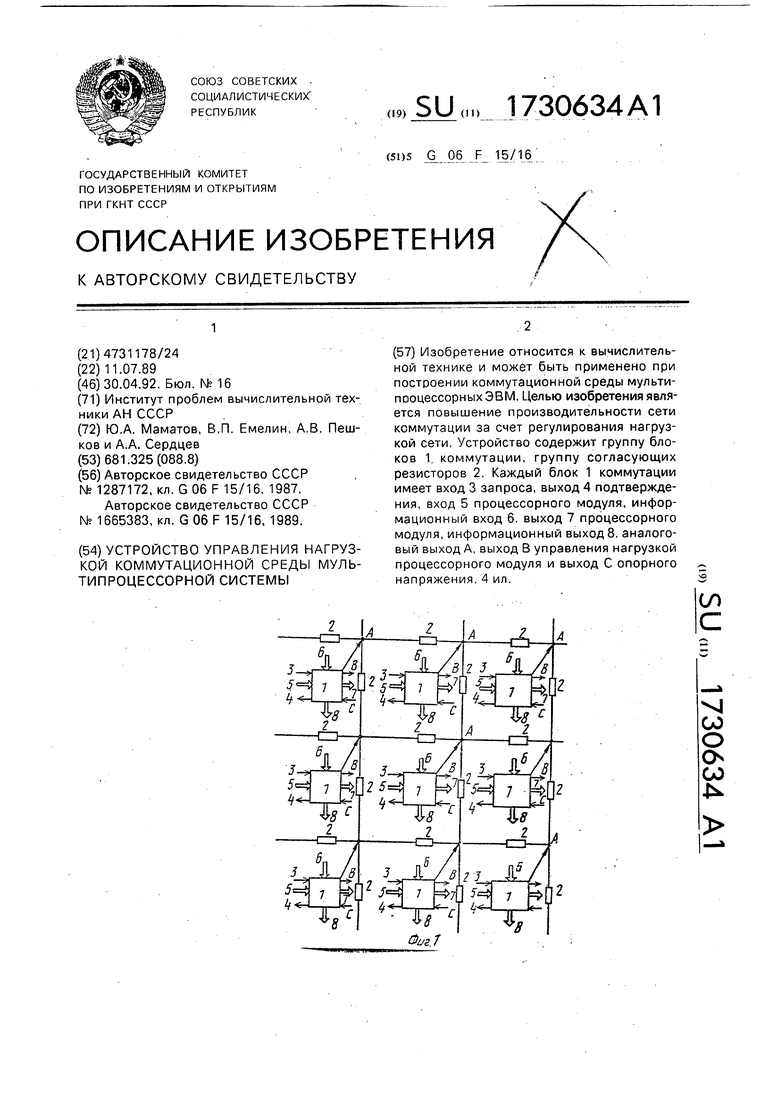

Изобретение относится к вычислительной технике и может быть применено при построении коммутационной среды мульти- пооцессорныхЭВМ. Целью изобретения является повышение производительности сети коммутации за счет регулирования нагрузкой сети. Устройство содержит группу блоков 1 коммутации, группу согласующих резисторов 2. Каждый блок 1 коммутации имеет вход 3 запроса, выход 4 подтверждения, вход 5 процессорного модуля, информационный вход 6. выход 7 процессорного модуля, информационный выход 8, аналоговый выходА, выход В управления нагрузкой процессорного модуля и выход С опорного напряжения. 4 ил.

V4

CJ О

СО

N

Изобретение относится к вычислительной технике и может быть применено при построении коммутационной среды мультипроцессорных ЭВМ.

Цель изобретения - повышение производительности сети коммутации за счет регулирования нагрузкой сети.

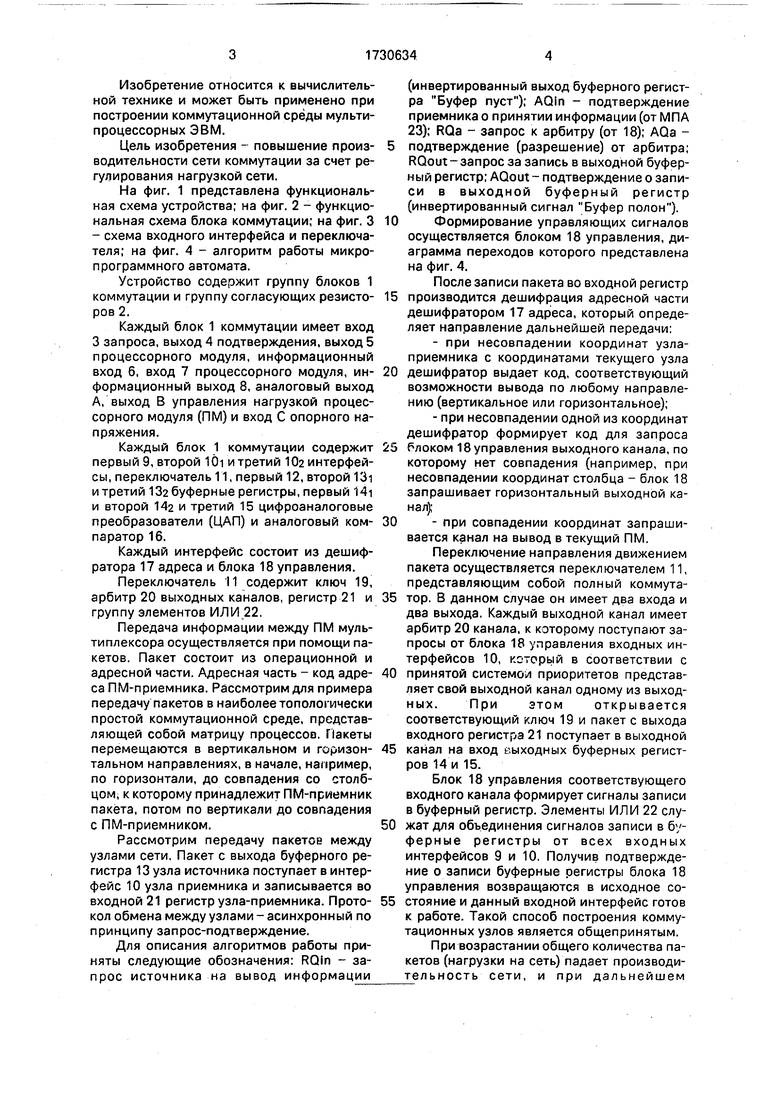

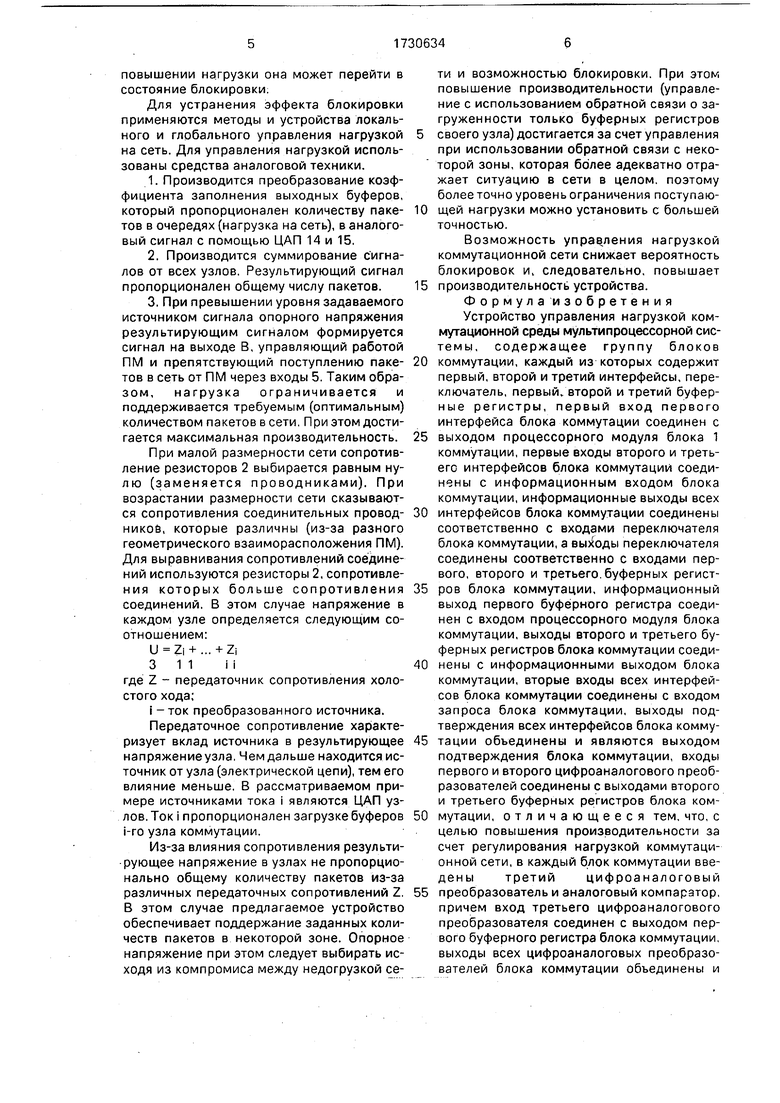

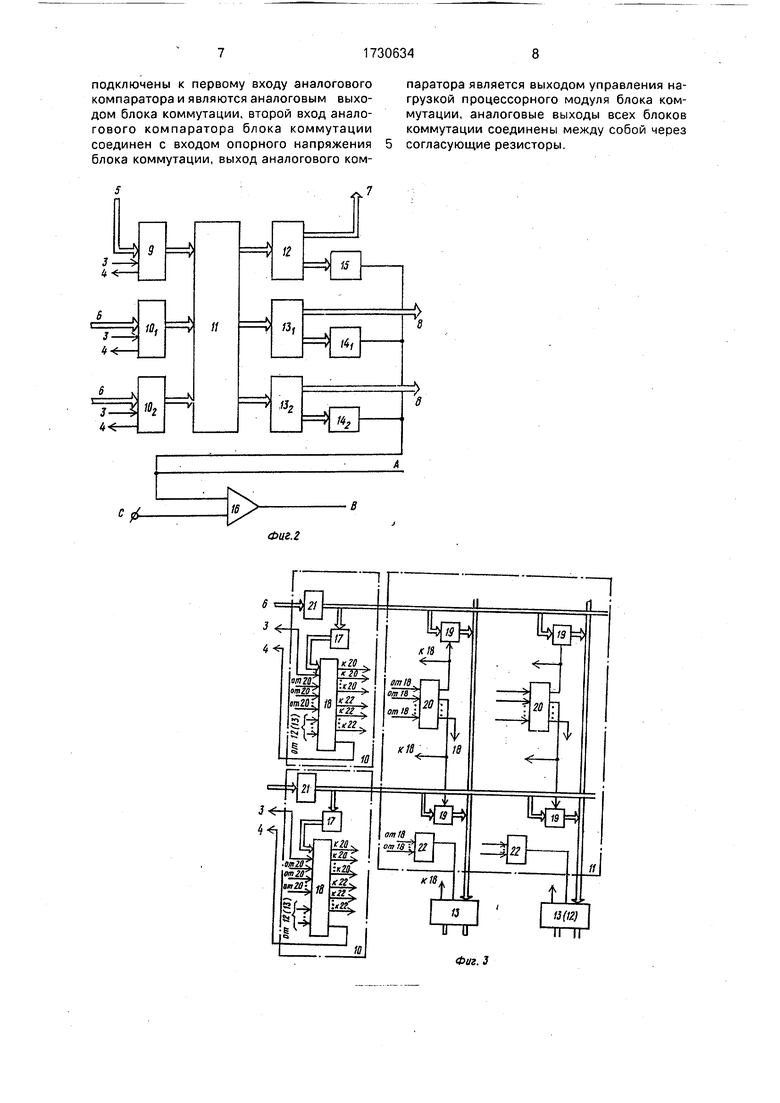

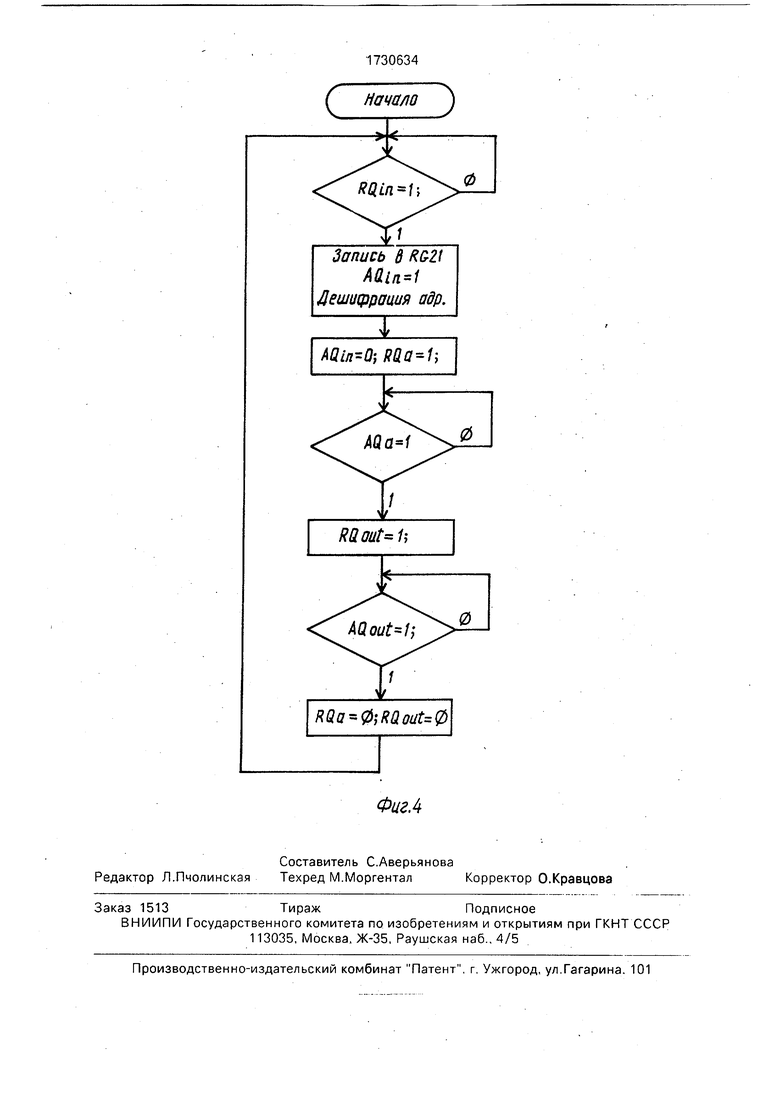

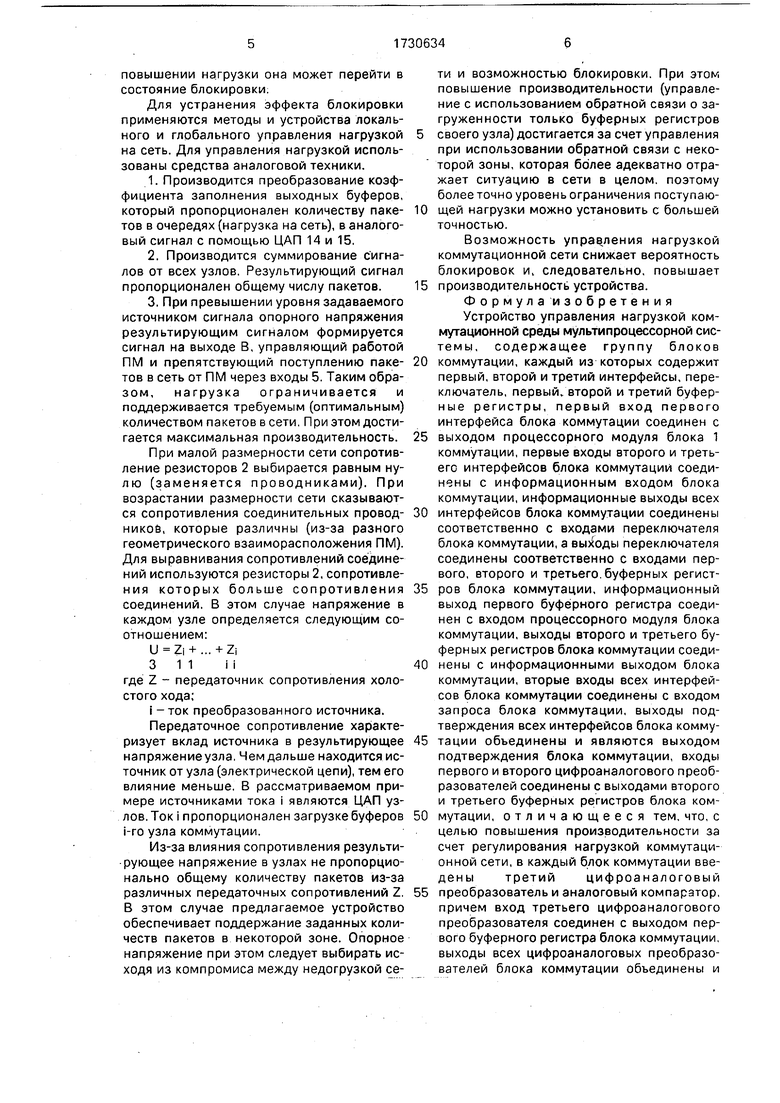

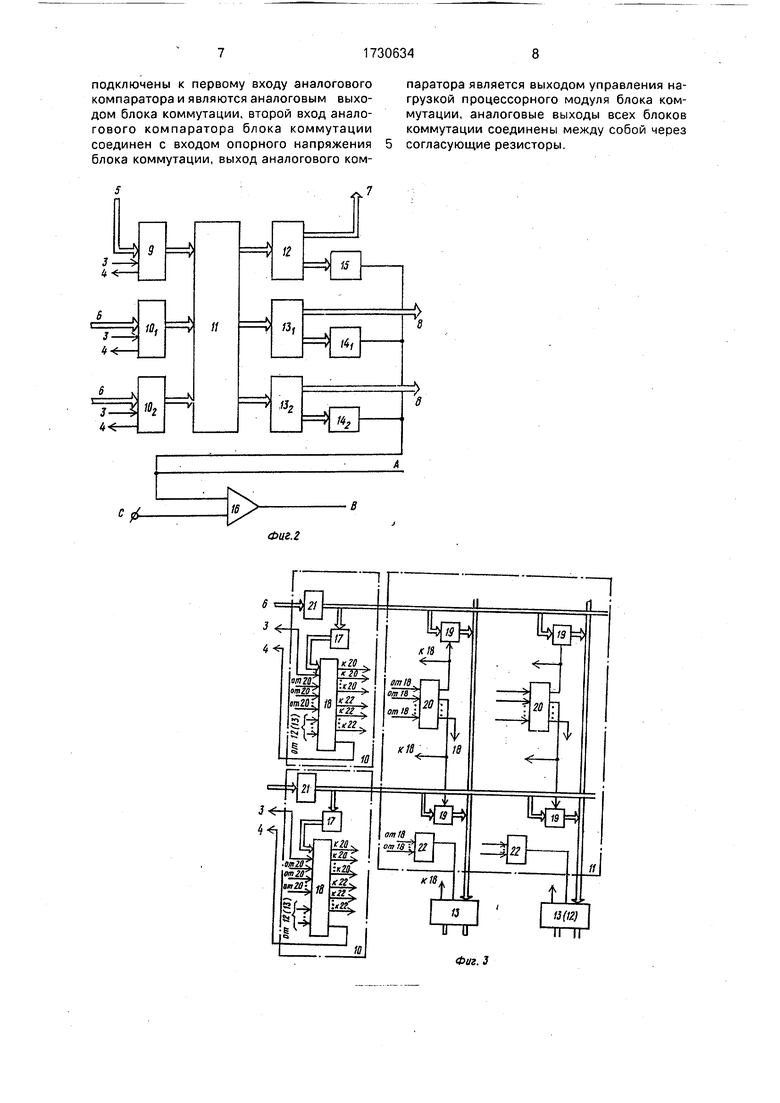

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема блока коммутации; на фиг. 3 - схема входного интерфейса и переключателя; на фиг. 4 - алгоритм работы микропрограммного автомата.

Устройство содержит группу блоков 1 коммутации и группу согласующих резисторов 2.

Каждый блок 1 коммутации имеет вход 3 запроса, выход 4 подтверждения, выход 5 процессорного модуля, информационный вход 6, вход 7 процессорного модуля, информационный выход 8, аналоговый выход А, выход В управления нагрузкой процессорного модуля (ПМ) и вход С опорного напряжения.

Каждый блок 1 коммутации содержит первый 9, второй 10i и третий 102 интерфейсы, переключатель 11, первый 12, второй 13i и третий 132 буферные регистры, первый 141 и второй 142 и третий 15 цифроаналоговые преобразователи (ЦАП) и аналоговый компаратор 16.

Каждый интерфейс состоит из дешифратора 17 адреса и блока 18 управления.

Переключатель 11 содержит ключ 19, арбитр 20 выходных каналов, регистр 21 и группу элементов ИЛИ 22,

Передача информации между ПМ мультиплексора осуществляется при помощи пакетов. Пакет состоит из операционной и адресной части. Адресная часть - код адреса ПМ-приемника. Рассмотрим для примера передачу пакетов в наиболее топологически простой коммутационной среде, представляющей собой матрицу процессов. Пакеты перемещаются в вертикальном и горизонтальном направлениях, в начале, например, по горизонтали, до совпадения со столбцом, к которому принадлежит ПМ-приемник пакета, потом по вертикали до совпадения с ПМ-приемником.

Рассмотрим передачу пакетов между узлами сети. Пакет с выхода буферного регистра 13 узла источника поступает в интерфейс 10 узла приемника и записывается во входной 21 регистр узла-приемника. Протокол обмена между узлами - асинхронный по принципу запрос-подтверждение.

Для описания алгоритмов работы приняты следующие обозначения: RQin - запрос источника на вывод информации

(инвертированный выход буферного регистра Буфер пуст); AQin - подтверждение приемника о принятии информации (от МПА 23); RQa - запрос к арбитру (от 18); Ada подтверждение (разрешение) от арбитра; RQout-запрос за запись в выходной буферный регистр; AQout- подтверждение о записи в выходной буферный регистр (инвертированный сигнал Буфер полон).

0 Формирование управляющих сигналов осуществляется блоком 18 управления, диаграмма переходов которого представлена на фиг. 4.

После записи пакета во входной регистр

5 производится дешифрация адресной части дешифратором 17 адреса, который определяет направление дальнейшей передачи:

-при несовпадении координат узла- приемника с координатами текущего узла

0 дешифратор выдает код, соответствующий возможности вывода по любому направлению (вертикальное или горизонтальное);

-при несовпадении одной из координат дешифратор формирует код для запроса

5 блоком 18 управления выходного канала, по которому нет совпадения (например, при несовпадении координат столбца - блок 18 запрашивает горизонтальный выходной канал);

0 - при совпадении координат запрашивается канал на вывод в текущий ПМ.

Переключение направления движением пакета осуществляется переключателем 11, представляющим собой полный коммута5 тор. В данном случае он имеет два входа и два выхода. Каждый выходной канал имеет арбитр 20 канала, к которому поступают запросы от блока 18 управления входных интерфейсов 10, который в соответствии с

0 принятой системой приоритетов представляет свой выходной канал одному из выход- ных. При этом открывается соответствующий ключ 19 и пакет с выхода входного регистра 21 поступает в выходной

5 канал на вход выходных буферных регистров 14 и 15.

Блок 18 управления соответствующего входного канала формирует сигналы записи в буферный регистр. Элементы ИЛИ 22 слу0 жат для объединения сигналов записи в буферные регистры от всех входных интерфейсов 9 и 10. Получив подтверждение о записи буферные регистры блока 18 управления возвращаются в исходное со5 стояние и данный входной интерфейс готов к работе. Такой способ построения коммутационных узлов является общепринятым.

При возрастании общего количества пакетов (нагрузки на сеть) падает производительность сети, и при дальнейшем

повышении нагрузки она может перейти в состояние блокировки.

Для устранения эффекта блокировки применяются методы и устройства локального и глобального управления нагрузкой на сеть. Для управления нагрузкой использованы средства аналоговой техники.

При малой размерности сети сопротивление резисторов 2 выбирается равным ну- лю (заменяется проводниками). При возрастании размерности сети сказываются сопротивления соединительных проводников, которые различны (из-за разного геометрического взаиморасположения ПМ). Для выравнивания сопротивлений соединений используются резисторы 2, сопротивления которых больше сопротивления соединений. В этом случае напряжение в каждом узле определяется следующим соотношением:

U Z| + ... + Zi

311 i i

где Z - передаточник сопротивления холостого хода;

i - ток преобразованного источника.

Передаточное сопротивление характеризует вклад источника в результирующее напряжение узла, Чем дальше находится источник от узла (электрической цепи), тем его влияние меньше. В рассматриваемом примере источниками тока i являются ЦАП узлов. Ток i пропорционален загрузке буферов i-ro узла коммутации.

Из-за влияния сопротивления результирующее напряжение в узлах не пропорционально общему количеству пакетов из-за различных передаточных сопротивлений Z. В этом случае предлагаемое устройство обеспечивает поддержание заданных количеств пакетов в некоторой зоне. Опорное напряжение при этом следует выбирать исходя из компромиса между недогрузкой сети и возможностью блокировки. При этом повышение производительности (управление с использованием обратной связи о загруженности только буферных регистров

своего узла) достигается за счет управления при использовании обратной связи с некоторой зоны, которая более адекватно отражает ситуацию в сети в целом, поэтому более точно уровень ограничения поступаю0 щей нагрузки можно установить с большей точностью.

Возможность управления нагрузкой коммутационной сети снижает вероятность блокировок и, следовательно, повышает

5 производительность устройства.

Формула изобретения Устройство управления нагрузкой коммутационной среды мультипроцессорной сис- темы, содержащее группу блоков

0 коммутации, каждый из которых содержит первый, второй и третий интерфейсы, переключатель, первый второй и третий буферные регистры, первый вход первого интерфейса блока коммутации соединен с

5 выходом процессорного модуля блока 1 коммутации, первые входы второго и третьего интерфейсов блока коммутации соединены с информационным входом блока коммутации, информационные выходы всех

0 интерфейсов блока коммутации соединены соответственно с входами переключателя блока коммутации, а выходы переключателя соединены соответственно с входами первого, второго и третьего, буферных регист5 ров блока коммутации, информационный выход первого буферного регистра соединен с входом процессорного модуля блока коммутации, выходы второго и третьего буферных регистров блока коммутации соеди0 йены с информационными выходом блока коммутации, вторые входы всех интерфейсов блока коммутации соединены с входом запроса блока коммутации, выходы подтверждения всех интерфейсов блока комму5 тации объединены и являются выходом подтверждения блока коммутации, входы первого и второго цифроаналогового преобразователей соединены с выходами второго и третьего буферных регистров блока ком0 мутации, отличающееся тем, что, с целью повышения производительности за счет регулирования нагрузкой коммутационной сети, в каждый блок коммутации введены третий цифроаналоговый

5 преобразователь и аналоговый компаратор, причем вход третьего цифроаналогового преобразователя соединен с выходом первого буферного регистра блока коммутации, выходы всех цифроаналоговых преобразователей блока коммутации объединены и

подключены к первому входу аналогового компаратора и являются аналоговым выходом блока коммутации, второй вход аналогового компаратора блока коммутации соединен с входом опорного напряжения блока коммутации, выход аналогового комLb {

12

ю,

п

13,

10,

13,

паратора является выходом управления нагрузкой процессорного модуля блока коммутации, аналоговые выходы всех блоков коммутации соединены между собой через согласующие резисторы.

fe

СНачалоj

Запись 8 K&Zt

Дешифрация йдр.

AQln-0;

RQct-0;RQoitt 0

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для коммутации сообщений | 1989 |

|

SU1665383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-07-11—Подача