2 /

83

Q

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор-умножитель по модулю три | 1987 |

|

SU1441395A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2021630C1 |

| Сумматор-умножитель | 1983 |

|

SU1173409A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ | 1992 |

|

RU2090924C1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для сложения и вычитания чисел по модулю | 1990 |

|

SU1755275A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения комплексных чисел | 1987 |

|

SU1418707A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах и устройствах, функционирующих в системе остаточных классов. Цель изобретения - сокращение аппаратурных затрат. Сумматор-умножитель по модулю три содержит элементы ИЛИ 3, 5, 6, 10, 22, 23, И 13 - 17, 20, 21 и ИСКЛЮЧАЮЩЕЕ ИЛИ 4, 7, 18, 19 с соответствующими связями. 1 ил.

//

-5

Ё

ON О XI О СЛ

Изобретение относится к области вычислительной техники и может быть использовано в системе и устройствах, функционирующих в системах остаточных классов (СОК).

Цель изобретения - сокращение аппаратурных затрат.

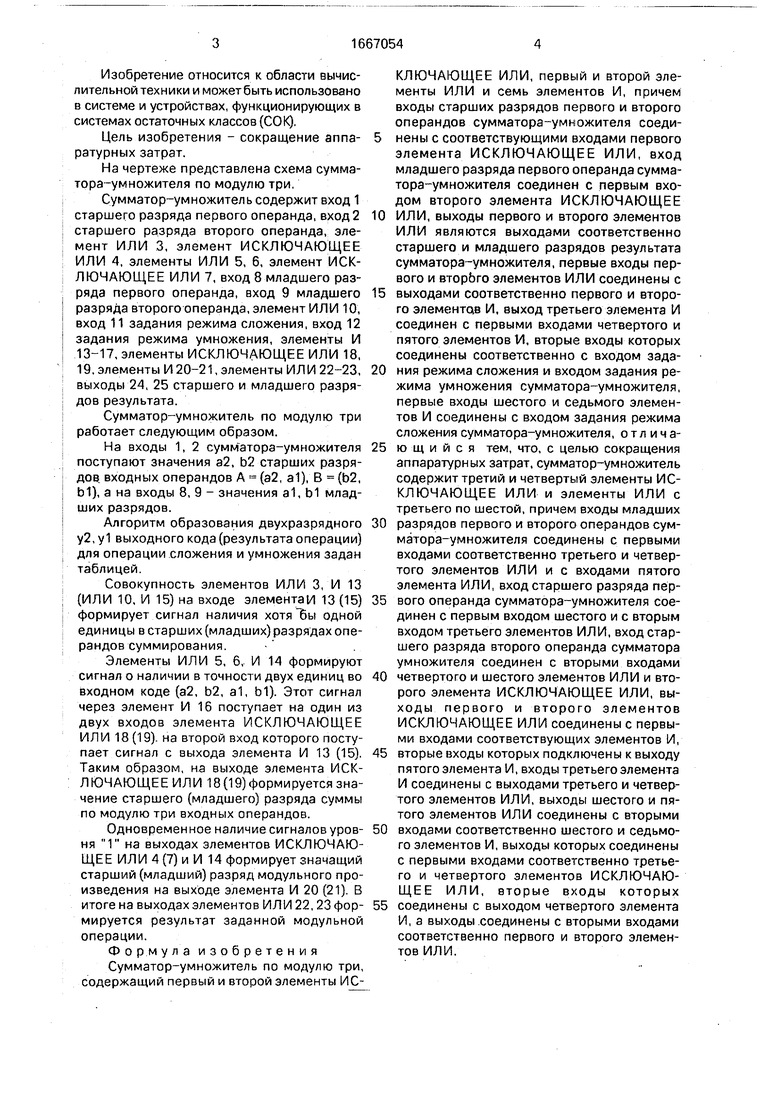

На чертеже представлена схема сумматора-умножителя по модулю три.

Сумматор-умножитель содержит вход 1 старшего разряда первого операнда, вход 2 старшего разряда второго операнда, элемент ИЛИ 3. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элементы ИЛИ 5, 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, вход 8 младшего разряда первого операнда, вход 9 младшего разряда второго операнда, элемент ИЛИ 10, вход 11 задания режима сложения, вход 12 задания режима умножения, элементы И 13-17, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 18, 19, элементы И 20-21, элементы ИЛИ 22-23, выходы 24, 25 старшего и младшего разрядов результата.

Сумматор-умножитель по модулю три работает следующим образом.

На входы 1, 2 сумматора-умножителя поступают значения а2, Ь2 старших разрядов входных операндов А (а2, а1), В (Ь2, Ы), а на входы 8, 9 - значения а1, Ы младших разрядов.

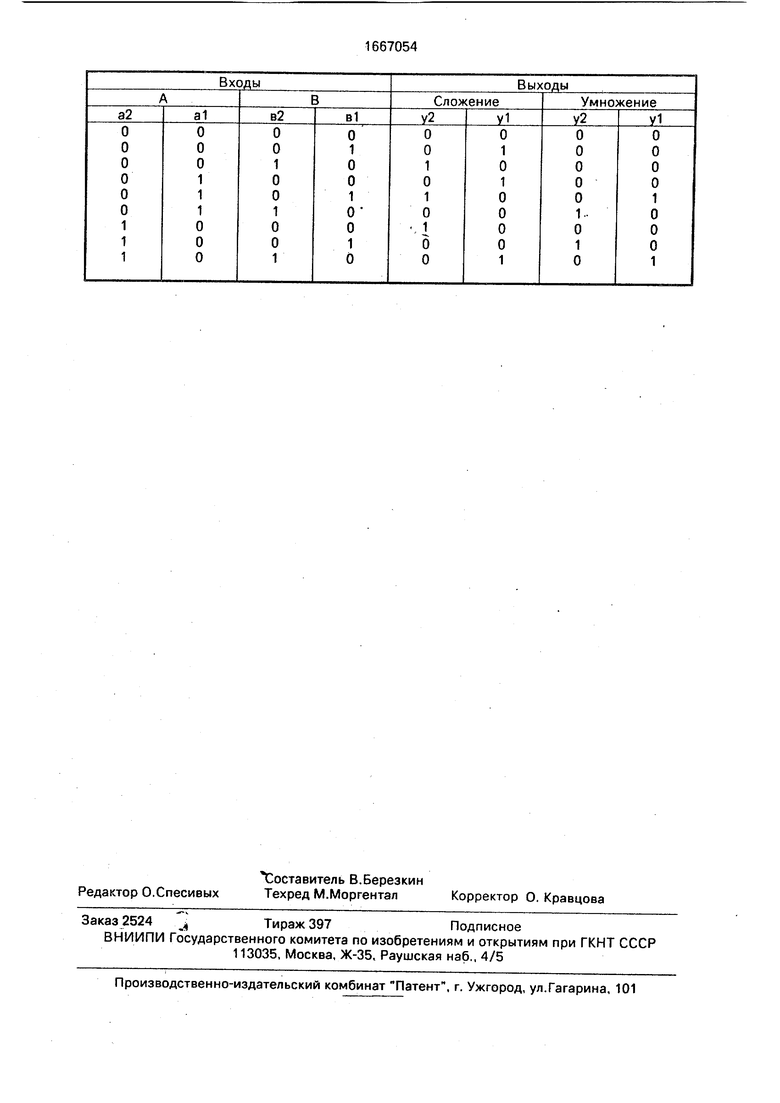

Алгоритм образования двухразрядного у2, у1 выходного кода (результата операции) для операции сложения и умножения задан таблицей.

Совокупность элементов ИЛИ 3, И 13 (ИЛИ 10, И 15) на входе элемента И 13 (15) формирует сигнал наличия хотя1)ы одной единицы в старших (младших) разрядах операндов суммирования.

Элементы ИЛИ 5, 6, И 14 формируют сигнал о наличии в точности двух единиц во входном коде (а2, Ь2, а1, Ы). Этот сигнал через элемент И 16 поступает на один из двух входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 (19) на второй вход которого поступает сигнал с выхода элемента И 13 (15). Таким образом, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 (19) формируется значение старшего (младшего) разряда суммы по модулю три входных операндов.

Одновременное наличие сигналов уровня 1 на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4 (7) и И 14 формирует значащий старший (младший) разряд модульного произведения на выходе элемента И 20 (21) В итоге на выходах элементов ИЛИ 22,23 формируется результат заданной модульной операции.

Формула изобретения Сумматор-умножитель по модулю три, содержащий первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы ИЛИ и семь элементов И, причем входы старших разрядов первого и второго операндов сумматора-умножителя соединены с соответствующими входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход младшего разряда первого операнда сумматора-умножителя соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, выходы первого и второго элементов ИЛИ являются выходами соответственно старшего и младшего разрядов результата сумматора-умножителя, первые входы первого и второго элементов ИЛИ соединены с

выходами соответственно первого и второго элементов И, выход третьего элемента И соединен с первыми входами четвертого и пятого элементов VI, вторые входы которых соединены соответственно с входом задания режима сложения и входом задания режима умножения сумматора-умножителя, первые входы шестого и седьмого элементов И соединены с входом задания режима сложения сумматора-умножителя, о т л и ч аю щ и и с я тем, что, с целью сокращения аппаратурных затрат, сумматор-умножитель содержит третий и четвертый элементы ИС- КЛЮЧАЮЩЕЕ ИЛИ и элементы ИЛИ с третьего по шестой, причем входы младших

разрядов первого и второго операндов сумматора-умножителя соединены с первыми входами соответственно третьего и четвертого элементов ИЛИ и с входами пятого элемента ИЛИ, вход старшего разряда первого операнда сумматора-умножителя соединен с первым входом шестого и с вторым входом третьего элементов ИЛИ, вход старшего разряда второго операнда сумматора умножителя соединен с вторыми входами

четвертого и шестого элементов ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первыми входами соответствующих элементов И,

вторые входы которых подключены к выходу пятого элемента И, входы третьего элемента И соединены с выходами третьего и четвертого элементов ИЛИ, выходы шестого и пятого элементов ИЛИ соединены с вторыми

0 входами соответственно шестого и седьмого элементов И, выходы которых соединены с первыми входами соответственно третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых

5 соединены с выходом четвертого элемента И, а выходы соединены с вторыми входами соответственно первого и второго элементов ИЛИ.

| Сумматор-умножитель | 1983 |

|

SU1173409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сумматор-умножитель по модулю три | 1987 |

|

SU1441395A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-08-07—Подача