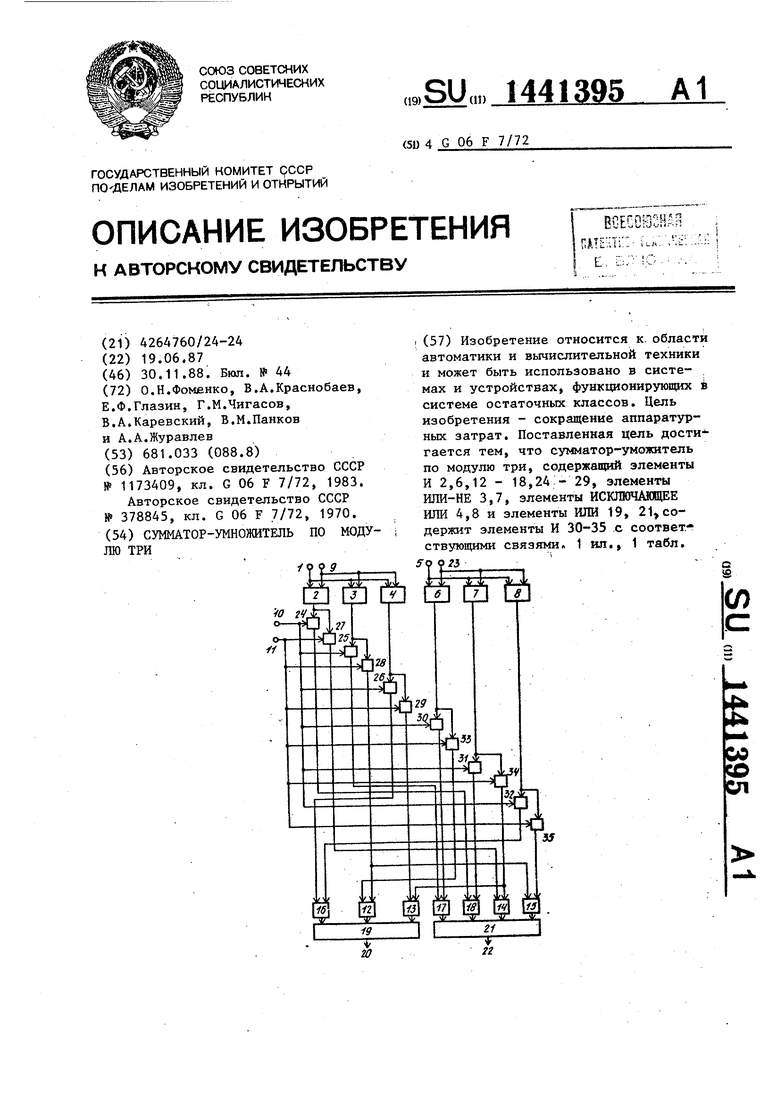

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах и устройствах, функционирующих в система остаточных классов (СОК).

Целью изобретения является сокращение аппаратурных затрат.

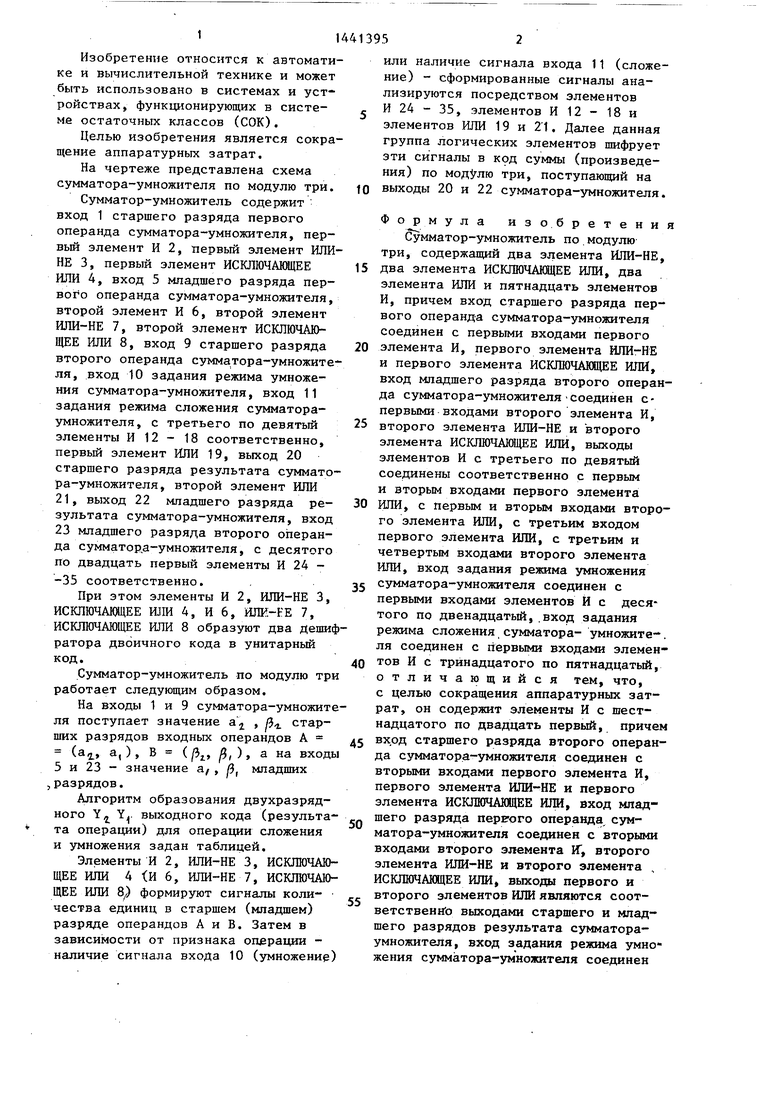

На чертеже представлена схема сумматора-умножителя по модулю три.

Сумматор-умножитель содержит вход 1 старшего разряда первого операнда сумматора-умножителя, первый элемент И 2, первый элемент ИЛИ- НЕ 3, первый элемент ИСКЛЮЧАЩЕЕ ИЛИ 4, вход 5 младшего разряда первого операнда сумматора-умножителя, второй элемент И 6, второй элемент ИЛИ-НЕ 7, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, вход 9 старшего разряда второго операнда сумматора-умножителя, вход 10 задания режима умножения сумматора-умножителя, вход 11 задания режима сложения сумматора- умножителя, с третьего по девятый элементы И 12 - 18 соответственно, первый элемент ИЛИ 19, выход 20 старшего разряда результата сзгммато- ра-умножителя, второй элемент ИЛИ 21, выход 22 младшего разряда результата сумматора-умножителя, вход 23 младшего разряда второго операнда сумматор,а-умножителя, с десятого по двадцать первый элементы И 24 - -35 соответственно.

При этом элементы И 2, ИЛИ-НЕ 3, ИСКЛЮЧАЩЕЕ ИЛИ 4, И 6, ШШ-РЕ 7, ИСКЛЮЧАЮЩЕЕ ИЛИ 8 образуют два дешифратора двоичного кода в унитарный код.

Сумматор-умножитель по модулю три работает следующим образом.

На входы 1 и 9 сумматора-умножитля поступает значение а , старших разрядов входных операндов А (а., а, ), В (/5.,,, , ), а на входы 5 и 23 - значение а,, , младших ,разрядов.

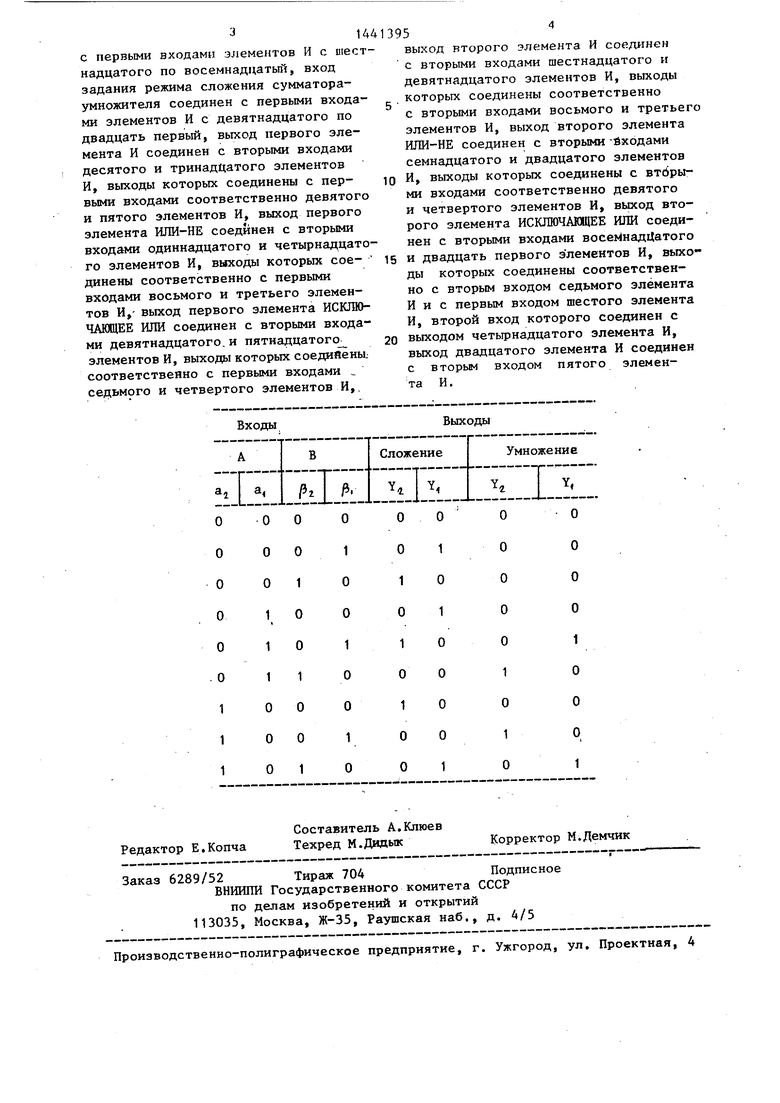

Алгоритм образования двухразрядного Y Y. выходного кода (результата операции) для операции сложения и умножения задан таблицей.

Элементы И 2, ИЛИ-НЕ 3, ИСКЛЮЧАЮЩЕЕ ИЖ 4 И 6, ИЛИ-НЕ 7, ИСКЛЮЧАЮЩЕЕ ИЛИ 8 формируют сигналы коли- чества единиц в старшем (младшем) разряде операндов А и В. Затем в зависимости от признака операции - наличие сигнала входа 10 (умножение

5

0

5

0

5

0

5

0

5

или наличие сигнала входа 11 (сложение) - сформированные сигналы анализируются посредством элементов И 24 - 35, элементов И 12 - 18 и элементов ИЛИ 19 и 21. Далее данная группа логических элементов шифрует эти сигналы в код суммы (произведения) по модулю три, поступающий на выходы 20 и 22 сумматора-умножителя.

Формула изобретения

Сумматор-умножитель по модулю три, содержащий два элемента ЙЛИ-НЕ, два элемента ИСКЛЮЧАВДЕЕ ИЛИ, два элемента ИЛИ и пятнадцать элементов И, причем вход старшего разряда первого операнда сумматора-умножителя соединен с первыми входами первого элемента И, первого элемента ИЛИ-НЕ и первого элемента ИСКЛЮЧАЩЕЕ ИЛИ, вход младшего разряда второго операнда сумматора-умножителя Соединен с- первыми входами второго элемента И, второго элемента ИЛИ-НЕ и второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, выходы элементов И с третьего по девятый соединены соответственно с первым и вторым входами первого элемента ИЛИ, с первым и вторым входами второго элемента ИЛИ, с третьим входом первого элемента ИЛИ, с третьим и четвертым входами второго элемента ИЛИ, вход задания режима умножения сумматора-умножителя соединен с первыми входами элементов И с десятого по двенадцатый,.вход задания режима сложения сумматора- умножите-. ля соединен с первыми входами элементов И с тринадцатого по пятнадцатый, отличающийся тем, что, с целью сокращения аппаратурных затрат, он содержит элементы И с шестнадцатого по двадцать первый, причем вход старшего разряда второго операнда сумматора-умножителя соединен с вторыми входами первого элемента И, первого элемента ШШ-НЕ и первого элемента ИСКШОЧАЩЕЕ ИЛИ, вход младшего разряда пергого операнда сумматора-умножителя соединен с вторыми входами второго элемента IT, второго элемента ШШ-НЕ и второго элемента , ИСКЛЮЧАЩЕЕ ИЛИ, выходы первого и второго элементов ИЛИ являются соответственна выходами старшего и младшего разрядов результата сумматора- умножителя, вход задания режима умножения сумматора-умножителя соединен

с первыми входами элементов И с шестнадцатого по восемнадцать, вход задания режима сложения сумматора- умножителя соединен с первыми входами элементов И с девятнадцатого по двадцать первый, выход первого элемента И соединен с вторыми входами десятого и тринадцатого элементов И, выходы которых соединены с первыми входами соответственно девятого и пятого элементов И, выход первого элемента ИЛИ-НЕ соединен с вторыми входами одиннадцатого и четырнадцатого элементов И, выходы которых сое- динены соответственно с первыми входами восьмого и третьего элементов И,- выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторыми входами девятнадцатого, и пятнадцатого элементов И, выходы которых соедипены: соответственно с первыми входами седьмого и четвертого элементов И,.

выход второго элемента И соединен с вторыми входами шестнадцатого и девятнадцатого элементов И, выходы которых соединены соответственно с вторыми входами восьмого и третьего элементов И, выход второго элемента ИЛИ-НЕ соединен с вторыми -йходами семнадцатого и двадцатого элементов

0 И, выходы которых соединены с втЬры- ми входами соответственно девятого и четвертого элементов И, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторыми входами восе надЦатого

5 и двадцать первого элементов И, выходы которых соединены соответственно с вторым входом седьмого элемента И и с первым входом шестого элемента И, второй вход которого соединен с

0 выходом четырнадцатого элемента И, выход двадцатого элемента И соединен с вторым входом пятого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Сумматор-умножитель по модулю три | 1989 |

|

SU1667054A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Устройство для контроля информации по модулю | 1989 |

|

SU1751763A1 |

Изобретение относится к. области автоматики и вычислительной техники и может быть использовано в системах и устройствах, фун|сционирующих в системе остаточных классов. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель дости- гается тем, что сумматор-уможитель по модулю три, содержапц й элементы И 2,6,12 - 18,24-29, элементы ИЛИ-НЕ 3,7, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4,8 и элементы ИЛИ 19, 21,содержит элементы И 30-35 с соответствующими связями 59 9 « 1 Ш1., 1 табл. с Ш (Л :о ю СП

| Сумматор-умножитель | 1983 |

|

SU1173409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ I | 0 |

|

SU378845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-30—Публикация

1987-06-19—Подача