Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

Изобретение относится к вычислительной технике и может быть использовано в графических дисплеях растрового типа. Целью изобретения является повышение быстродействия устройства в режиме записи. Устройство содержит группу элементов ИЛИ, группу элементов И, первую и вторую группы одновибраторов, группу блоков памяти, мультиплексор и дешифратор. Цель изобретения достигается организацией параллельной работы блоков памяти при произвольном следовании адресов записи за счет автономной фиксации адреса и данных в блоках памяти на все время цикла записи и анализа состояния готовности запрашиваемого блока памяти перед подачей очередного сигнала обращения. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в графических дисплеях растрового типа.

Цель изобретения - повышение быстродействия устройства в режиме записи.

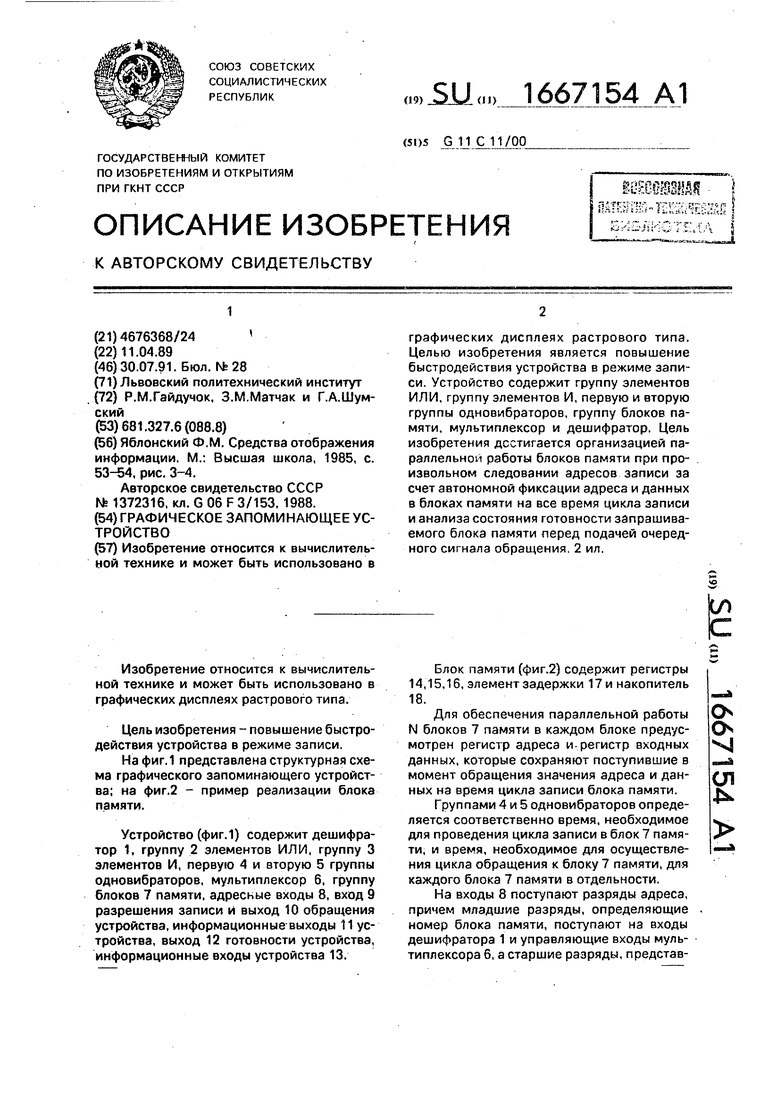

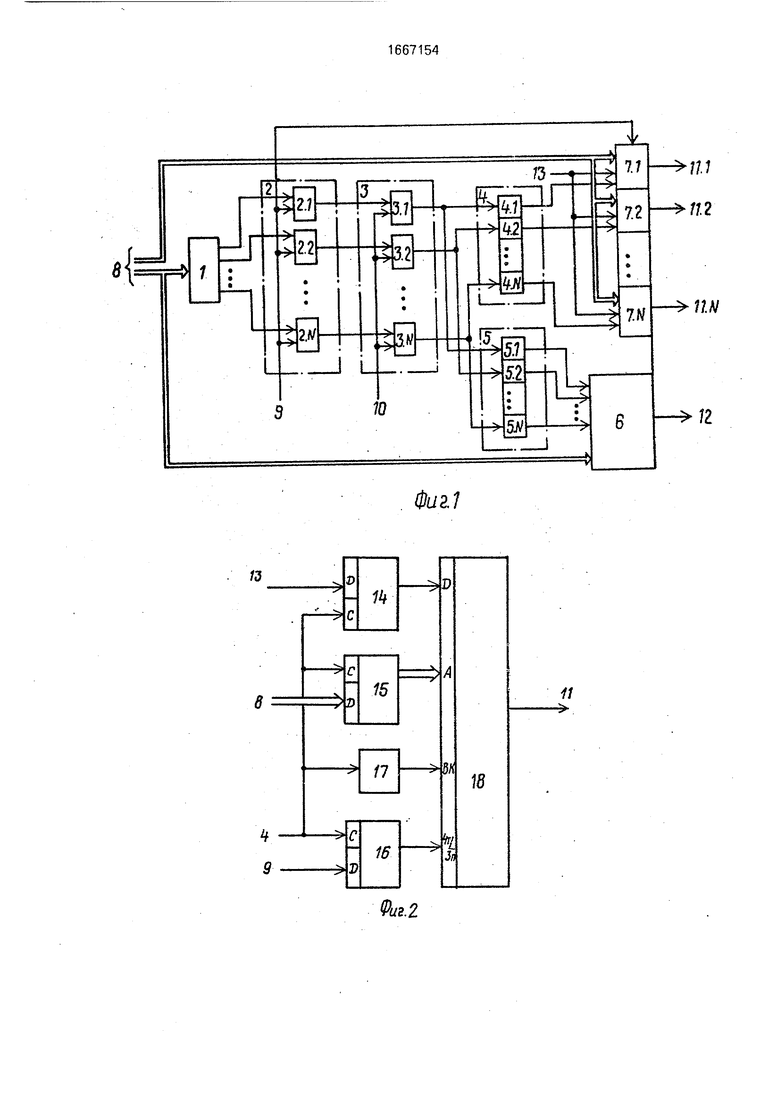

На фиг.1 представлена структурная схема графического запоминающего устройства; на фиг.2 - пример реализации блока памяти.

Устройство (фиг.1) содержит дешифратор 1, группу 2 элементов ИЛИ, группу 3 элементов И, первую 4 и вторую 5 группы одновибраторов, мультиплексор 6, группу блоков 7 памяти, адресные входы 8, вход 9 разрешения записи и выход 10 обращения устройства, информационные выходы 11 устройства, выход 12 готовности устройства, информационные входы устройства 13.

Блок памяти (фиг.2) содержит регистры 14,15,16, элемент задержки 17 и накопитель 18.

Для обеспечения параллельной работы N блоков 7 памяти в каждом блоке предусмотрен регистр адреса и регистр входных данных, которые сохраняют поступившие в момент обращения значения адреса и данных на время цикла записи блока памяти.

Группами 4 и 5 одновибраторов определяется соответственно время, необходимое для проведения цикла записи в блок 7 памяти, и время, необходимое для осуществления цикла обращения к блоку 7 памяти, для каждого блока 7 памяти в отдельности.

На входы 8 поступают разряды адреса, причем младшие разряды, определяющие номер блока памяти, поступают на входы дешифратора 1 и управляющие входы мультиплексора б, а старшие разряды, представС

О

ел

ляющие собой адоес ячейки в блоках 7 памяти - на адресные РХОДЫ блоков 7 памяти.

Запоминающее устройство работает следующим o6pajoM.

В режиме загтиси сигнал разрешения записи на входе 9 соответствует низкому логическому потенциалу, в результате чего сигналы с выхода дешифратора 1, определяющие номер блока памяти, куда должна произвестись запись, передадутся на выходы элементов ИЛИ группы 2, которые подключены к первым элементам И группы 3. на вторых входах которых в момент обращения к устройству установится высокий логический потенциал, что разрешит передачу сигналов с первого входа элементов на их. выходы. Сигнаплмм с. выходов зпеменгое И группы 3 управляются однсвибраторы первой 4 и второй 5 групп. Запуск одновибра- тороо производится высоким логическим потенциалом. Формируемые одновибрато- рами А сигналы поступают на входы зыбор- ки блоков 7 памяти во время цикла записи или считывания информации.

После поступления очередных адреса и данных для записи в запоминающее устройство необходимо определить, находится ли в цикле записи блок 7 памятиt в который произошло обращение, и сформировать сигнал готовности устройства. Состояние блоков 7 памяти определяется сигналами с выходов группы 5 одновибраторов, которые поступают на информационные входы мультиплексора б, к управляющим входам которого подключены входы 8 младших разрядов адреса. В результате на выходе мультиплексора 6 будет присутствовать сигнал, указывающий в каком состоянии находится блок 7 памяти, Б который произошло обращение. Если сигнал на выходе мультиплексора 6 имеет высокий логический уровень, блок находится в активном состоянии. В этом случае работа графического процессора приостанавливается до появлснил на выходе 12 сигнала низкого логического потенциала. Сигнал низкого уровня на выходе мультиплексора б разрешает работу процессора, так как в этом случае блок 7 памяти готов к записи очередных данных. Наличие сигнала логического нуля на выходе мультиплексора 6 разрешает графическому процессору формирование сигнала обращения к устройству на входе 10.

В режиме считывания сигнал разрешения записи на входе 9 соответствует высокому логическому потенциалу, при отом на

выходах элементов ИЛИ группы 2 также установится потенциал, соответствующий логической единице, который будет передаваться на первые входы элементов И

группы 3. В момент обращения к устройству сигнал на входе 10 примет единичное значение, в результате чего сигналы высокого логического уровня, присутствующие на первых входах элементов И группы 3, передадутся на выходы этих элементов, т.е. произойдет запуск одновременно всех одновибраторов групп 4 и 5.

Таким образом, в режиме считывания происходит выборка сразу всех блоков 7

памяти и по установленным на входах -8 старшим разрядам адреса осуществляется параллельное считывание содержимого этих блоков. Формирование сигнала готовности на выходе 12 происходит так же как и

в режиме записи.

Формула изобретения Графическое запоминающее устройство, содержащее дешифратор и группу блоков памяти, адресные и информационные входы которых являются соответственно входами старших разрядов адреса и информационными входами устройства, входы записи и выходы блоков памяти группы

являются соответственно входом разрешения записи и информационными выходами устройства, входы дешифратора являются входами младших разрядов адреса устройства, отличающееся тем, что, с целью

повышения быстродействия устройства в режиме записи, в него введены мультиплексор, первая и вторая группы одновибраторов, группа элементов И и группа элементов ИЛИ, причем выходы дешифратора соединены с первыми входами элементов ИЛИ группы, вторые входы которых подключены к входам разрешения записи устройства, а выходы соединены с первыми входами соответствующих элементов И группы, вторые

входы которых являются входом обращения устройства, а выходы подключены к входам соответствующих одновибраторов первой и второй групп, выходы одновибраторов первой группы соединены с входами выборки

соответствующих блоков памяти группы, выходы одновибраторов второй группы подключены к информационным входам мультиплексора, управляющие входы которого соединены с входами младших разрядов адреса устройства, выход мультиплексора является выходом готовности устройства.

8

t

Ill

Фиг/

| Яблонский Ф.М | |||

| Средства отображения информации | |||

| М.: Высшая школа, 1985, с, 53-54, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Запоминающее устройство для графического дисплея | 1986 |

|

SU1372316A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-04-11—Подача