25

112771

Изобретение относится к вычислиельной технике и может быть испольовано при построении многопроцессорых систем.

Целью изобретения является повыше- ие производительности обработки за чет возможности применения распредеенной операционной системы.

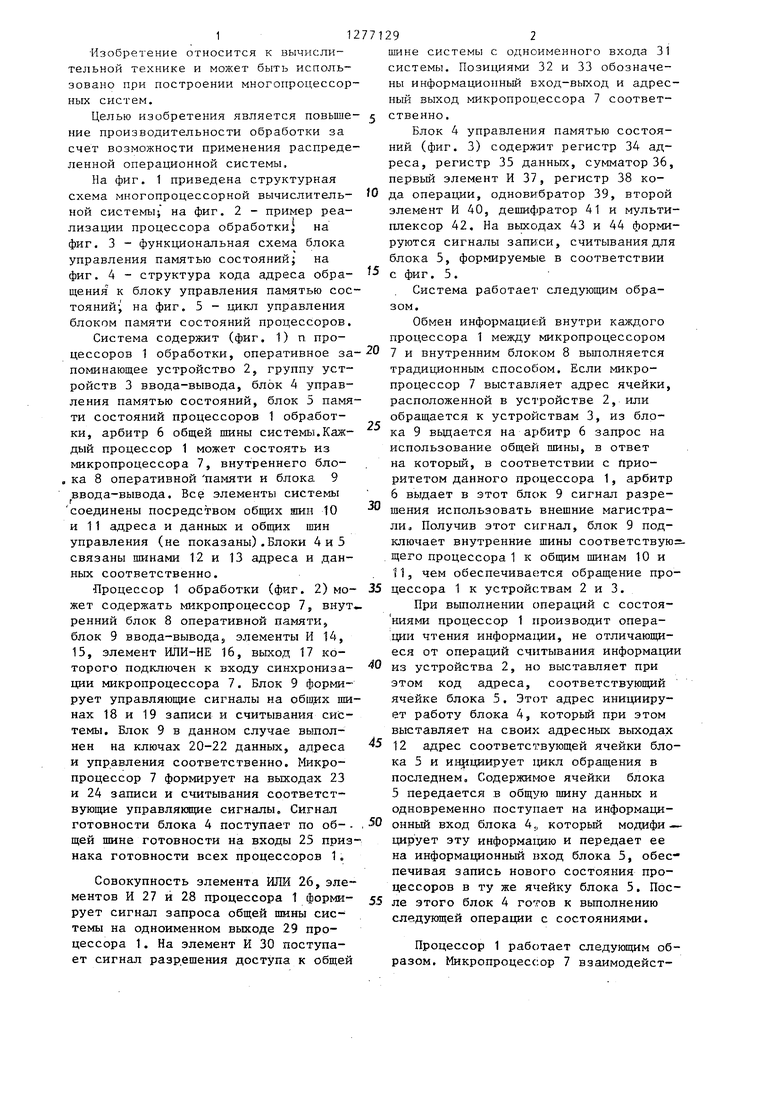

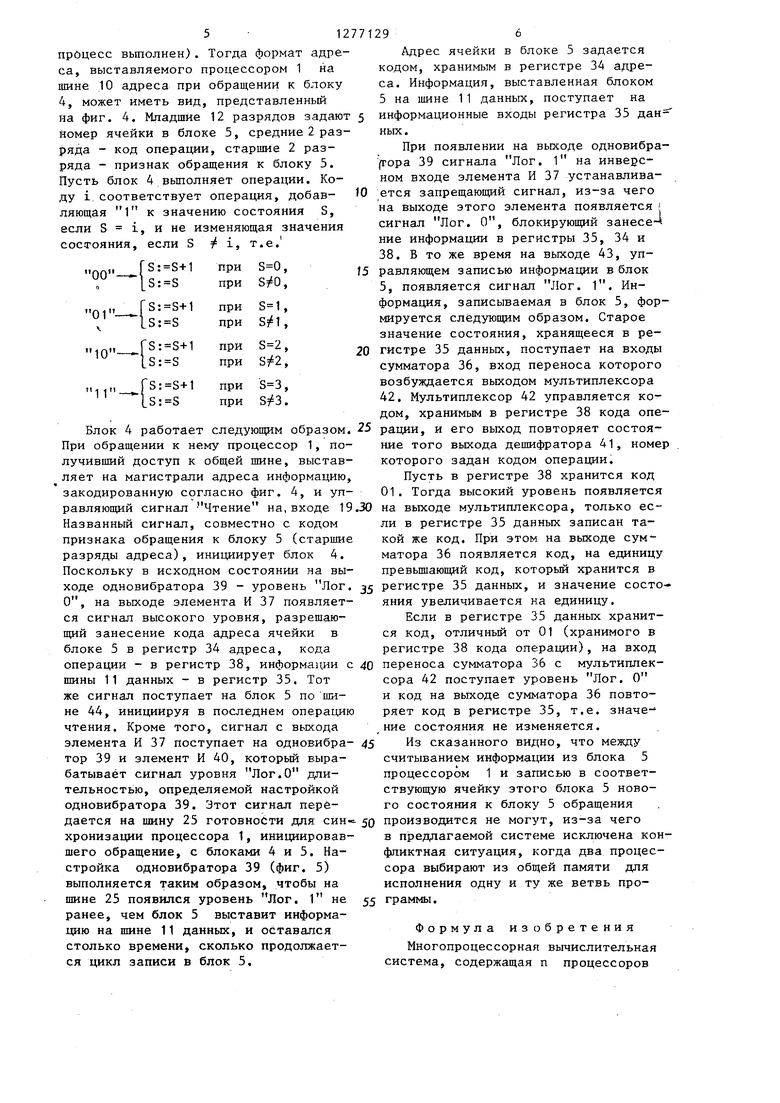

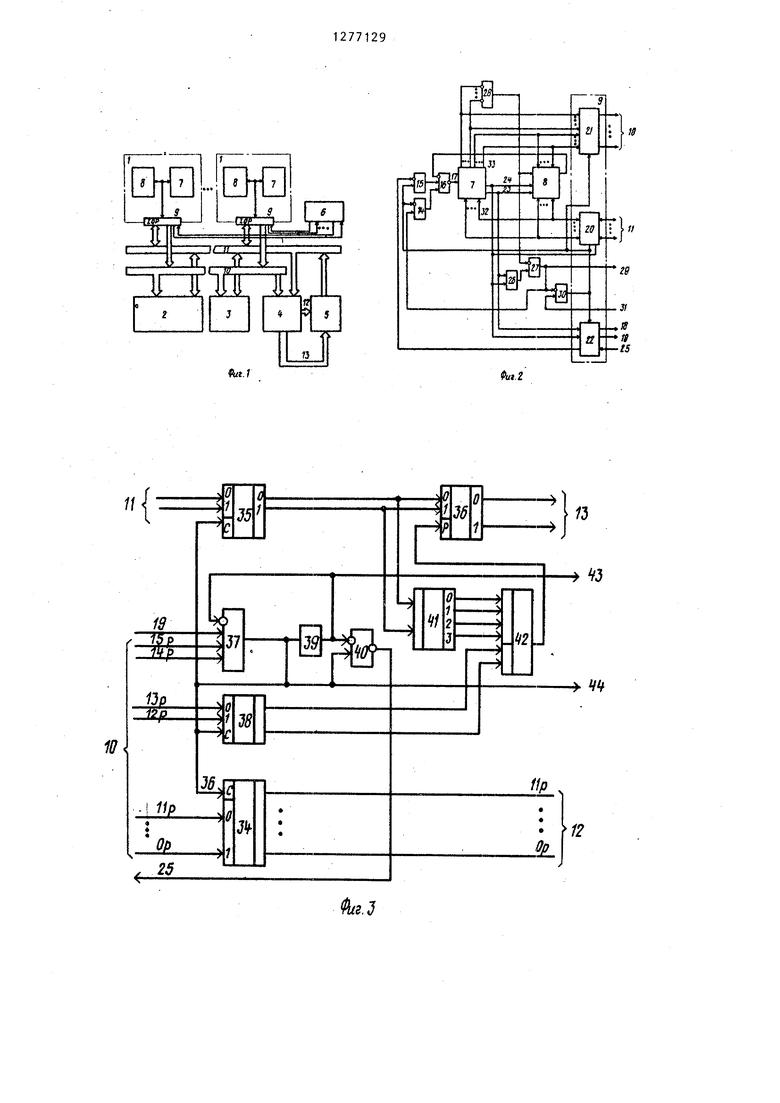

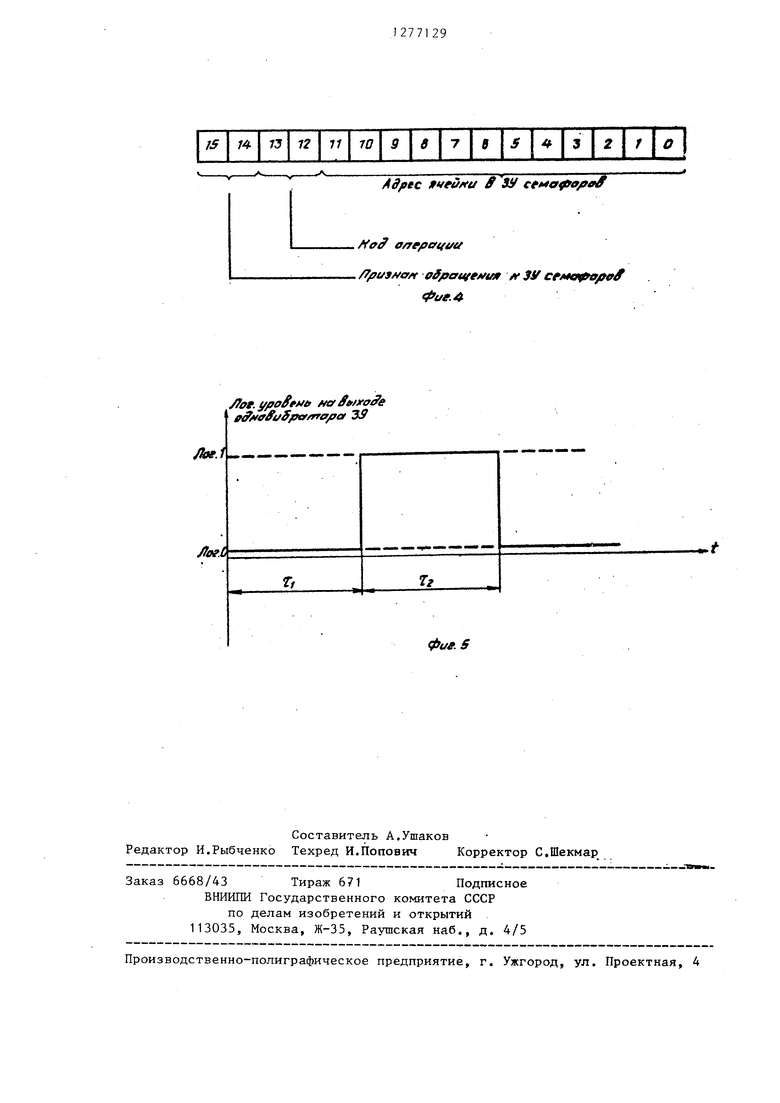

На фиг. 1 приведена структурная хема многопроцессорной вычислитель- О ной системы; на фиг. 2 - пример реаизации процессора обработки; на иг. 3 - функциональная схема блока управления памятью состояний; на фиг. 4 - структура кода адреса обра- щения к блоку управления памятью состояний; на фиг. 5 - цикл управления блоком памяти состояний процессоров.

Система содержит (фиг, 1) п процессоров 1 обработки, оперативное за--20 поминающее устройство 2, группу устройств 3 ввода-вывода, блок 4 управления памятью состояний, блок 5 памяти состояний процессоров 1 обработки, арбитр 6 общей шины сиетемы.Каждый процессор 1 может состоять из микропроцессора 7, внутреннего бло- ка 8 оперативной памяти и блока 9 ввода-вывода. Все элементы системы соединены посредством общих шин 10 и 11 адреса и данных и общих шин управления (не показаны) .Блоки 4и5 связаны шинами 12 и 13 адреса и данных соответственно.

Процессор 1 обработки (фиг. 2) мо- 35 жет содержать микропроцессор 7, внут«. ренний блок 8 оперативной памяти, блок 9 ввода-вывода, элементы И 14, 15, элемент ИЛИ-НЕ 16, выход 17 которого подключен к входу синхроннаа- ции микропроцессора 7. Блок 9 формирует управляющие сигналы на обш$5х шинах 18 и 19 записи и считывания системы. Блок 9 в данном случае выполнен на ключах 20-22 данных, адреса и управления соответственно. Микропроцессор 7 формирует на выходах 23 и 24 записи и считывания соответствующие управлякяцие сигналы. Сигнал готовности блока 4 поступает по об- - , -50 щей шине готовности на входы 25 признака готовности всех процессоров 1.

Совокупность элемента ИЖ 26, элементов И 27 и 28 процессора 1 форми- 55 рует сигнал запроса общей шины системы на одноименном выходе 29 процессора 1. На элемент И 30 поступает сигнал разрешения доступа к общей

30

5

71

О

0

35 -50

55

0

292

шине системы с одноименного входа 31 системы. Позиидями 32 и 33 обозначены информационный вход-выход и адресный выход микропроцессора 7 соответственно .

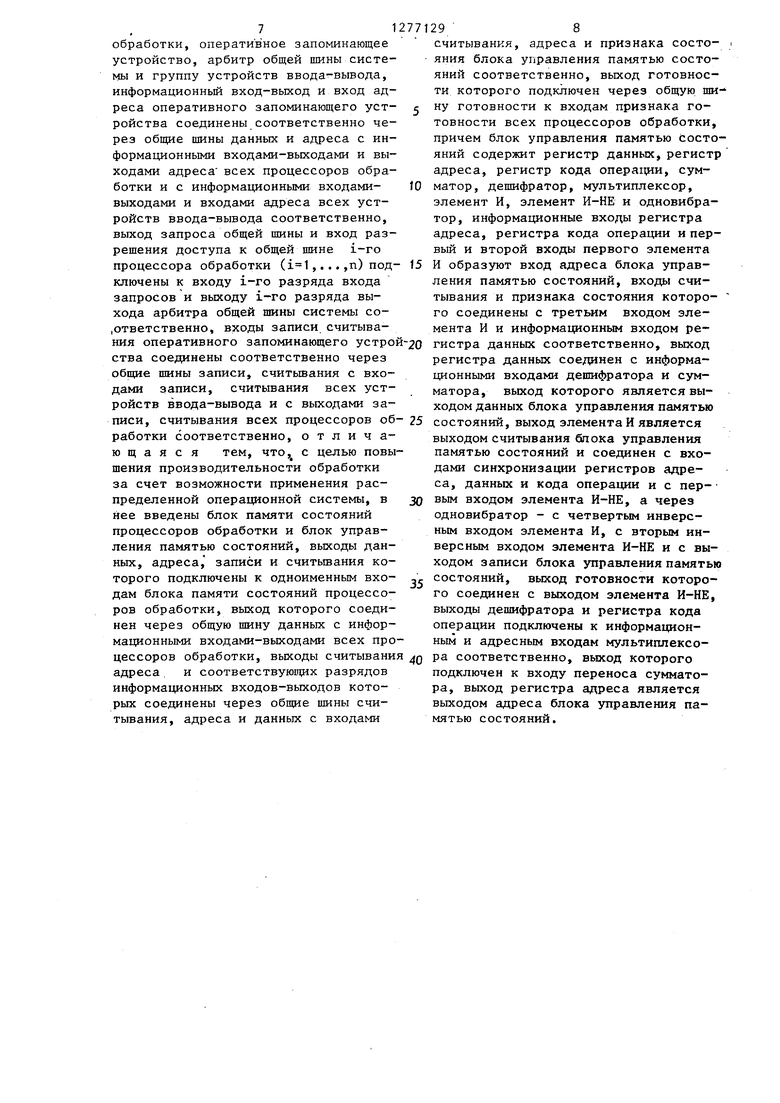

Блок 4 управления памятью состояний (фиг. 3) содержит регистр 34 адреса, регистр 35 данных, сумматор 36, первый элемент И 37, регистр 38 кода операции, одновибратор 39, второй элемент И 40, дешифратор 41 и мультиплексор 42. На вькодах 43 и 44 формируются сигналы запи:си, считывания для блока 5, формируемые в соответствии с фиг. 5.

Система работает спецующкм образом.

Обмен информацией внутри каждого процессора 1 между микропроцессором 7 и внутренним блоком 8 выполняется традиционным способом. Если микропроцессор 7 выставх{яет адрес ячейки, расположенной в устройстве 2, или обращается к устройствам 3, из блока 9 вьщается на арбитр 6 запрос на использование общей шины, в ответ на который, в соответствии с приоритетом даннох- о процессора 1, арбитр 6 выдает в этот блок 9 сигнал разрешения использовать внешние магистрали Получив этот сигнал, блок 9 подключает внутренние шины соответствую - щего процессора 1 к общим шинам 10 и 11, чем обеспечивается обращение процессора 1 к устройствам 2 и 3.

При выполнении операций с состоя- ниями процессор 1 производит опера- ции чтения информации, не отличающиеся от операций считывания информации из устройства 2, но выставляет при этом код адреса, соответствующий ячейке блока 5. Этот адрес инициирует работу блока 4, которьй при этом выставляет на своих адресных выходах 12 адрес соответствующей ячейки блока 5 и ин|1циирует цикл обращения в последнем. Содержимое ячейки блока 5 передается в общую шину данных и одновременно поступает на информационный вход блока 4,, который модифицирует эту информацию и передает ее на информационный вход блока 5, обес печивая запись нового состояния процессоров в ту же ячейку блока 5, После этого блок 4 готов к вьтолнению следующей операции с состояниями.

Процессор 1 работает следующим образом. 1У1икропроцессор 7 взаимодейст31

вуёт с внешними схемами только при обращениях к внутреннему блоку 8, к устройству 2 или к устройствам 3 ввода-вывода. При всяком обращении на адресных выходах 33 микропроцессор выставляет код адреса; при чтении информации из внутреннего блока 8 оперативного запоминающего устройства 2, а также при приеме информации из устройств 3 ввода-вывода на выходе 24 устанавливается сигнал, ини-циирующий операцию чтения в запоминающих устройствах или ввода в устройствах ввода-вывода. При записи микропроцессор 7 выставляет ин- формацию на своих информационных выходах и на выходе 23 устанавливает сигнал, инициируюгщй цикл записи в блоке 8 и устройстве.2 или вывода информации в устройствах 3 ввода- вывода.

В каждом цикле обращения микропроцессора 7 старшие разряды кода, выставленного на его адресных выходах, определяют режим обращения. Если на этих разрядах выставлен код, устанавливающий уровень Лог. 1 на выходе элемента И 28, производится обращение к ячейке внутреннего блока 8 оперативной памяти. В противном случае обращение производится через внешние магистрали.

При обращении к блоку 8 сигнал с

выхода элемента И 28 совместно с сигналом с соответствующего выхода микропроцессора (24 при чтении, 23 при записи) инициирует цикл обращения во внутреннем блоке 8. Адрес ячейки в блоке 8 определяется кодом на млад- ,ших выходах адреса. Информационный обмен между микропроцессором 7 и блоком 8 производится через их информационные входы-выходы. Дпя синхрони- зации микропроцессора 7 и блока 8. последний устанавливает на выходе синхронизации сигнал Лог. О в начале обращения и оставляет его до тех пор, пока не закончит внутренний цикл обращения, после чего устанавливает на вькоде синхронизации сигнал Лог. 1. Сигнал с выхода синхронизации блока 8 через элемент ИЛИ-НЕ 16 воздействует на вход 17 синхро- низации микропроцессора 7, который приостанавливает обращение к блоку 8 до тех пор, пока на его входе синхронизации не появится сигнал Лог. 1.

O 5 0

5 0

5

0 п

294

При обращении микропроцессора 7 к устройствам 2 и 3 сигнал с выхода элемента И 28 блокирует блок 8 и пропускает через элемент И 27 сигнал элемента ИЛИ 26. На входы элемента ИЛИ 26 поступают сигналы чтения и записи с управляюш;их выходов 23 и 24 микропроцессора 7, на выходе элемента ИЛИ 26 формируется обобщенный сигнал обращения, которьш, пройдя через элемент И 27, поступает на вход 29 процессора. Этот же сигнал поступает на вход элемента И 14. До тех пор, пока на вход 31 не поступит уровень Лог. 1, элемент И 30 будет удерживать на выходе уровень Лог. О, и на выходе элемента И 14 будет сигнал Лог. 1, блокирующий через элемент ШШ 16 синхронизирующий вход микропроцессора 7. При поступлении сигнала разреще- ния по входу 31 на выходе элемента И 30 появляется сигнал Лог. 1. Этот сигнал открывает ключи 20, 21 и 22, пропуская сигналы с информационных, адресных и управляющих выходов микропроцессора 7 на соответствующие общие шины. В зависимости от уровня логического сигнала на выходе 24 микропроцессора 7 ключ 20 передает информацию с общей щины 11 на внутреннюю информационную шину 13 или в противоположном направлении. В то же время сигнал с выхода элемента И 27 блокирует элемент И 14 и готовит элемент И 15, на другой вход которого через ключ 22 поступает сигнал готовности с входа 25. В начале обращения адресованные в данном цикле устройства 2 и 3 устанавливают на шине 25 сигнал уровня Лог. О и переводят его в состояние Лог. 1 тогда, когда устройство, к которому производится обращение, оказывается готовым к завершению цикла обмена информацией. До тех пор, пока по шине 25 поступает сигнал Лог. О, на выходе элемента И 15 сохраняется сигнал Лог. 1 и вход синхронизации микропроцессора 7 блокирован. При поступлении по шине 25 сигнала Лог. 1 блокировка входа синхронизации прекращается .

Пусть блок 5 содержит 4к ячеек с разрядностью 2 (соответствует числу состояний процессора: О - процесс не готов к исполнению, 1 - процесс готов к исполнению, но не исполняет- | ся, 2 - процесс исполняется, 3 прбцесс выполнен). Тогда формат адреса, выставляемого процессором 1 на шине 10 адреса при обращении к блоку 4, может иметь вид, представленный на фиг. 4. Младшие 12 разрядов задают номер ячейки в блоке 5, средние 2 разряда - код операции, старшие 2 разряда - признак обращения к блоку 5. Пусть блок 4 вьшолняет операции. Коду i соответствует операция, добав- ляющая 1 к значению состояния S, если S i, и не изменяющая значения состояния, если S ф i, т.е.

™ -11; . Ms;:

11

Блок 4 работает следующим образом. При обращении к нему процессор 1, получивший доступ к общей шине, выставляет на магистрали адреса информацию, закодированную согласно фиг. 4, и управляющий сигнал Чтение на,входе 19 Названный сигнал, совместно с кодом признака обращения к блоку 5 (старшие разряды адреса), инициирует блок 4. Поскольку в исходном состоянии на выходе одновибратора 39 - уровень Лог. О, на выходе элемента И 37 появляется сигнал высокого уровня, разрешающий занесение кода адреса ячейки в блоке 5 в регистр 34 адреса, кода операции - в регистр 38, информации с шины 11 данных - в регистр 35, Тот же сигнал поступает на блок 5 по шине 44, инициируя в последнем операцию чтения. Кроме того, сигнал с выхода элемента И 37 поступает на одновибра- тор 39 и элемент И 40, который вырабатывает сигнал уровня Лог.О длительностью, определяемой настройкой одновибратора 39. Этот сигнал передается на шину 25 готовности для син- хронизации процессора 1, инициировавшего обращение, с блоками 4 и 5. Настройка одновибратора 39 (фиг. 5) выполняется таким образом, чтобы на шине 25 появился уровень Лог. 1 не ранее, чем блок 5 выставит информацию на шине 11 данных, и оставался столько времени, сколько продолжается цикл записи в блок 5,

5 О

f5

0

5 30 35 40 45 50 55

Адрес ячейки в блоке 5 задается кодом, хранимым в регистре 34 адреса. Информация, выставленная блоком 5 на шине 11 данных, поступает на информационные входы регистра 35 ньпх.

При появлении на выходе одновибра- fropa 39 сигнала Лог. 1 на инверсном входе элемента И 37 устанавливается запрещающий сигнал, из-за чего на выходе этого элемента появляется сигнал Лог. О, блокирующий занесе- ние информации в регистры 35, 34 и 38. В то же время на выходе 43, управляющем записью информации в блок 5, появляется сигнал Лог. 1. Информация, записываемая в блок 5, формируется слёдуюпщм образом. Старое значение состояния, хранящееся в регистре 35 данных, поступает на входы сумматора 36, вход переноса которого возбуждается выходом мультиплексора 42. Мультиплексор 42 управляется кодом, хранимым в регистре 38 кода операции, и его выход повторяет состояние того выхода дешифратора 41, номер которого задан кодом операции.

Пусть в регистре 38 хранится код 01. Тогда высокий уровень появляется на выходе мультиплексора, только если в регистре 35 данных записан такой же код. При этом на выходе сумматора 36 появляется код, на единицу превьш1ающий код, которьм хранится в регистре 35 данных, и значение состояния увеличивается на единицу.

Если в регистре 35 данных хранится код, отличный от 01 (хранимого в регистре 38 кода операции), на вход переноса сумматора 36 с мультиппек- сора 42 поступает уровень Лог. О и код на выходе сумматора 36 повторяет код в регистре 35, т.е. значе- ,ние состояния не изменяется.

Из сказанного видно, что между считыванием информации из блока 5 процессором 1 и записью в соответствующую ячейку этого блока 5 нового состояния к блоку 5 обращения производится не могут, из-за чего в предлагаемой системе исключена конфликтная ситуация, когда два процессора выбирают из общей памяти для исполнения одну и ту же ветвь программы .

Формула изобретения

Многопроцессорная вычислительная система, содержащая п процессоров

7

обработки, оперативное запоминающее устройство, арбитр общей шины системы и группу устройств ввода-вывода, информационный вход-выход и вход адреса оперативного запоминающего уст- ройства соединены соответственно через общие шины данных и адреса с информационными входами-выходами и выходами адреса всех процессоров обработки и с информационными входами- выходами и входами адреса всех устройств ввода-вывода соответственно, выход запроса общей шины и вход разрешения доступа к общей шине i-ro процессора обработки (,...,п) под ключены к входу i-ro разряда входа запросов и выходу i-ro разряда выхода арбитра общей шины системы со- ,ответственно, входы записи считывания оперативного запоминающего устро ства соединены соответственно через общие шины записи, считывания с входами записи, считывания всех устройств ввода-вывода и с выходами записи, считывания всех процессоров об работки соответственно, о т л и ч а- ю щ а я с я тем, что, с целью повышения производительности обработки за счет возможности применения распределенной операционной системы, в нее введены блок памяти состояний процессоров обработки и блок управления памятью состояний, выходы данных, адреса, записи и считьшания которого подключены к одноименным вхо- дам блока памяти состояний процессоров обработки, выход которого соединен через общую шину данных с информационными входами-выходами всех процессоров обработки, выходы считывани адреса и соответствующих разрядов информационных входов-выходов которых соединены через общие шины считывания, адреса и данных с входами

29 8

считывания, адреса и признака состояния блока управления памятью состояний соответственно, выход готовности которого подключен через общую ши ну готовности к входам признака готовности всех процессоров обработки, причем блок управления памятью состояний содержит регистр данных, регист адреса, регистр кода операгщи, сумматор, дешифратор, мультиплексор, элемент И, элемент И-НЕ и одновибра- тор, информационные входы регистра адреса, регистра кода операции и первый и второй входы первого элемента И образуют вход адреса блока управления памятью состояний, входы считывания и признака состояния которо- го соединены с третьим входом элемента И и информационным входом регистра данных соответственно, выход регистра данных соединен с информационными входами дешифратора и сумматора, выход которого является выходом данных блока управления памятью состояний, выход элемента И является выходом считывания блока управления памятью состояний и соединен с входами синхронизации регистров адреса, данных и кода операции и с первым входом элемента И-НЕ, а через одновибратор - с четвертым инверсным входом элемента И, с вторым инверсным входом элемента И-НЕ и с выходом записи блока управления памятью состояний, выход готовности которого соединен с выходом элемента И-НЕ, выходы дешифратора и регистра кода операции подключены к информационным и адресным входам мультиплексора соответственно, выход которого подключен к входу переноса сумматора, выход регистра адреса является выходом адреса блока управления памятью состояний.

fut.r

Фиг. г

fff.y/foffMt ffcfS nfa e ff ftffftfSffef/rrp a SS

/fae.L

T,

Составитель А.Ушаков Редактор И.Рыбченко Техред И.Попович Корректор С.Шекмар

Заказ 6668/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раутаская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фие.

t

Тг

Фи.б

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многопроцессорная вычислительная система | 1988 |

|

SU1569843A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| МНОГОМАШИННАЯ СИСТЕМА УПРАВЛЕНИЯ | 2006 |

|

RU2320003C2 |

| Устройство доступа к видеопамяти | 1988 |

|

SU1523058A3 |

Изобретение относится к области вычислительной техники и позволяет предотвратить выборку одной и той же ветви программы из общей памяти при использовании распределенной операционной системы в одноуровневой многопроцессорной системе. Для этого многопроцессорная система включает, наряду с процессорами обработки, оперативным запоминающим устройством, группой устройств ввода-вьшода и арбитром общей шины системы, блок памяти состояний процессоров и блок управления памятью состояний, который содержит регистры данных, адреса, сумматор, дешифратор, мультиплексор, регистр кода операции, одновибратор и два элемента И. 5 ил. S

| Микропрограммная система обработки данных | 1977 |

|

SU943736A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Adams G., Roldnder Т | |||

| Design motivations for multiple processer microcomputer systems | |||

| Computer Design, | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Горный компас | 0 |

|

SU81A1 |

Авторы

Даты

1986-12-15—Публикация

1985-04-24—Подача