Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти при блочной организации считывания информации

Цель изобретения - повышение надежности устройства.

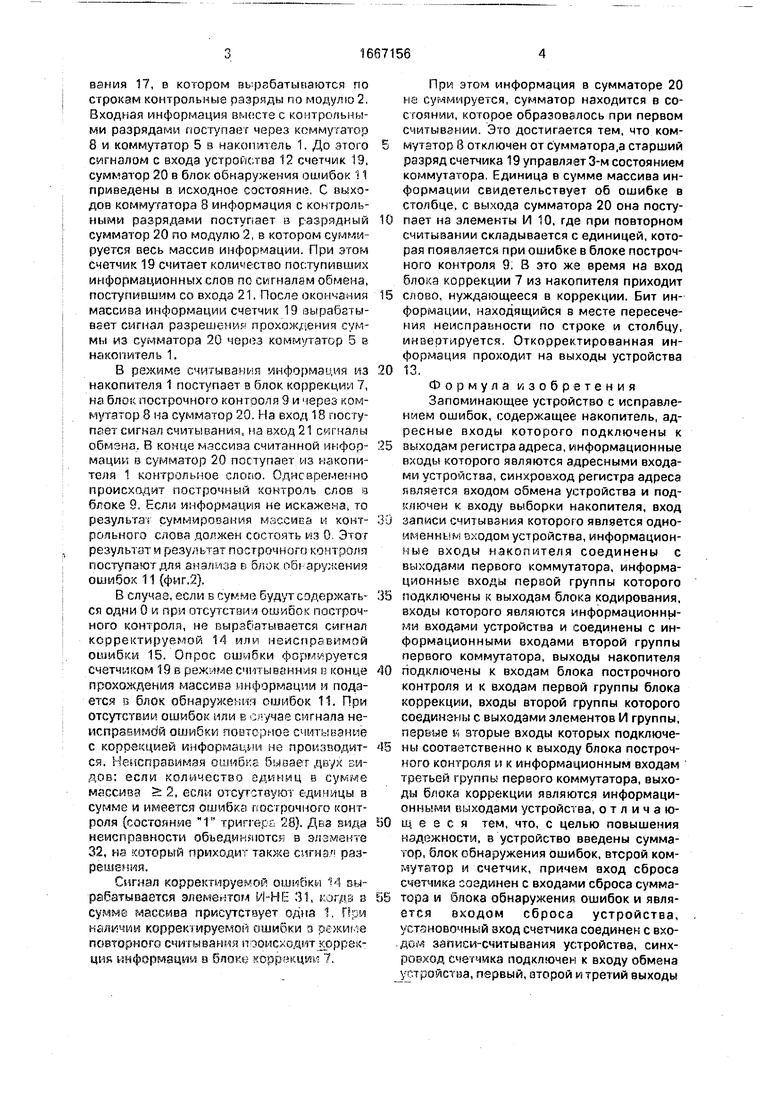

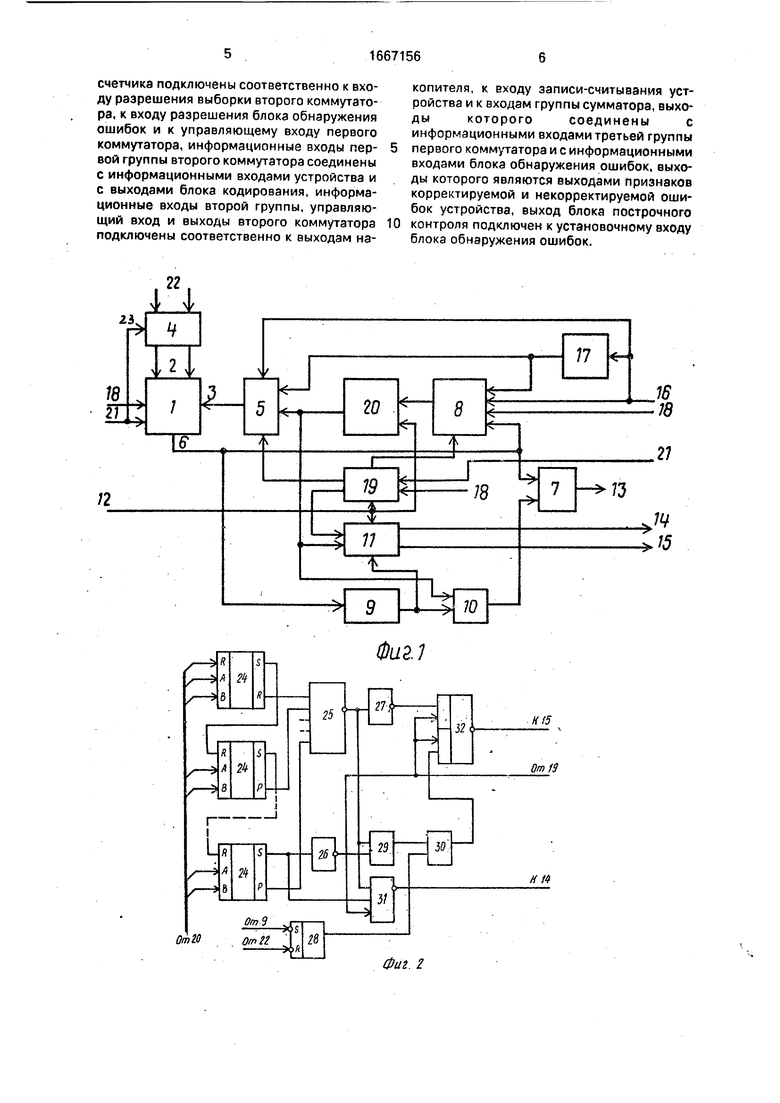

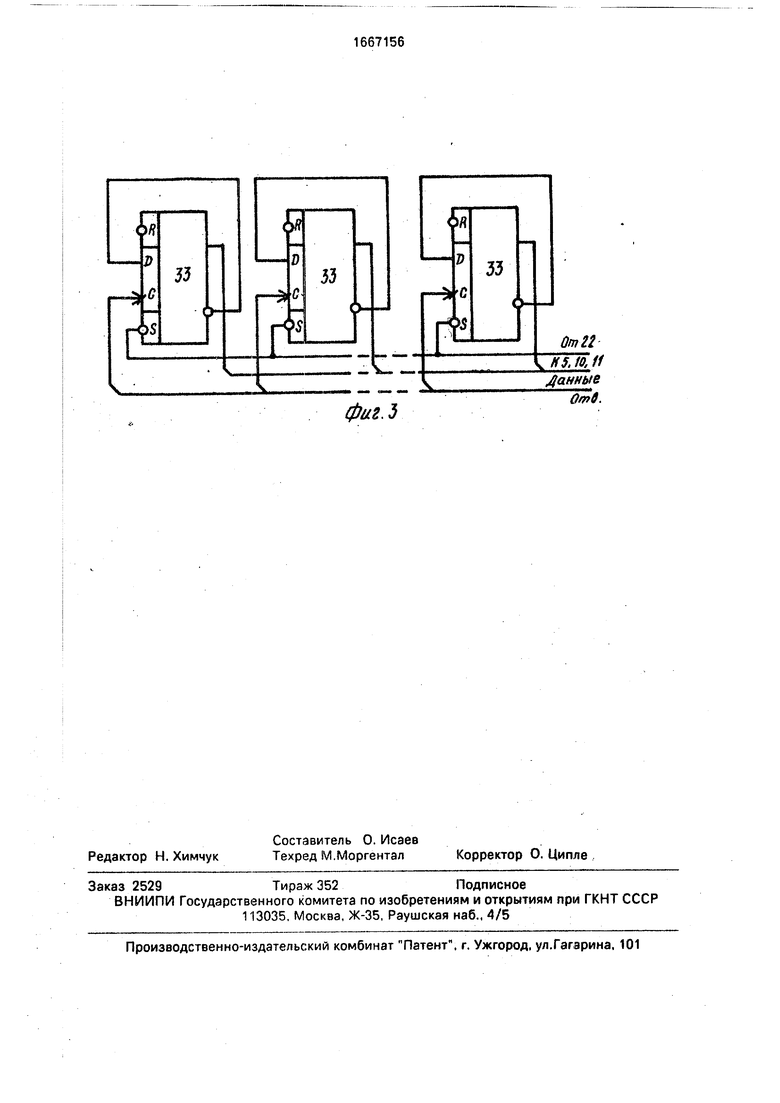

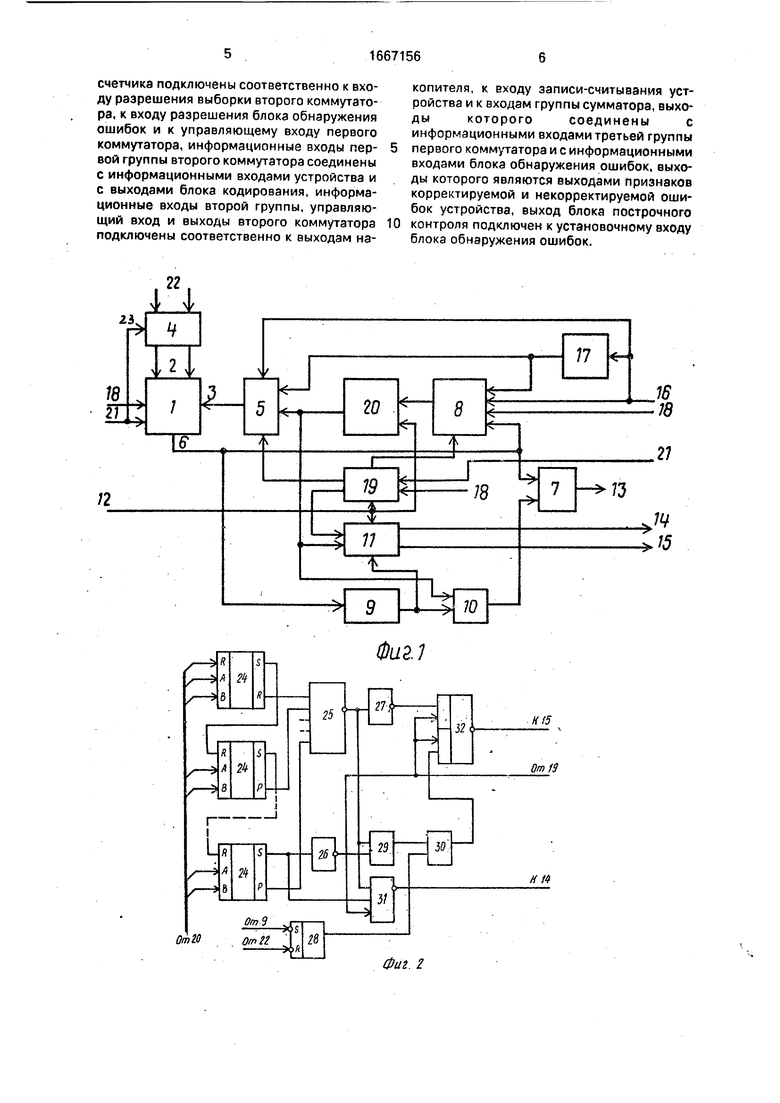

На фиг.1 приведена схема запоминающего устройства с исправлением ошибок; на фиг.2 - схема блока обнаружения ошибок; на фиг.З - пример реализации сумматора.

Устройство содержит накопитель 1 с адресными 2 и информационными 3 входами, регистр адреса 4, первый коммутатор 5, выходы 6 накопителя 1, бл&к коррекции 7, второй коммутатор 8, блок построчного контроля 9, группу элементов И 10, блок обнаружения ошибок 11, вход сброса 12, информационные выходы 13, выходы признаков корректируемой 14 и некорректируемой 15 ошибок, информационные входы 16, блок кодирования 17, вход записи-считывания 18, счетчик 19, сумматор 20, вход обмена 21, адресные входы 22, вход 23 регистра адреса 4.

Блок обнаружения ошибок 11 (фиг.2) содержит одноразрядные сумматоры 24. элемент ИЛИ-НЕ 25, элементы НЕ 26,27, триггер 28, элементы И 29,30, элемент И-НЕ 31 и элемент И-ИЛИ-НЕ 32.

На фиг.З показан вариант выполнения сумматора 20, состоящего из триггеров 33.

Устройство работает следующим образом.

В режиме записи на вход 18 приходит сигнал записи, а информация поступает на входы 16 устройства и далее в блок кодироCS

о VI

ел о

вания 17, в котором вырабатываются по строкам контрольные разряды по модулю 2 Входная информация вмосте с контрольны ми разрядами поступает через коммутатор 8 и коммутатор 5 в накопитель 1 До этого сигналом с входа устройства 12 счетчик 19, сумматор 20 в блок обнаружения ошибок 11 приведены в исходное состояние С выходов коммутатора 8 информация с контрольными разрядами поступает в разрядный сумматор 20 по модулю 2, в котором суммируется весь массив информации При этом счетчик 19 считает копичество поступивших информационных слов по сигналам обмена, поступившим со вход.э 21, После окончания массива информации счетчик 19 вырабатывает сигнал разрешения прохождения суммы из сумматора 20 через коммутатор 5 в накопитель 1.

В режиме считывания информация из накопителя 1 поступает в блок коррекции 7, на блок построчного контротя 9 и через коммутатор 8 на сумматор 20. На вход 18 посгу- паетсигнс / считывания, на вход 21 cut чал и обм-эна В конце массива считанной информации F3 сумматор 20 поступает из накопителя 1 контрольное Одновременно происходит нос тронный контроль слов в блоке 9 Если информация не искажена, то резульга. суммирования м ссиич и контрольного слова чог жеч состоять ич 0 Эшг результат и реэу/ ьтэт построчи )го контроля поступакп для акали ,а в блик обнару, ения ошибок 11 (фиг.2)

В случзз. если ь гумме будут содержать ся одни 0 и при отсутствии ошибок посфоч- ного контроля, не вырабатывается сигнал корректируемой 14 или неисправимой ошибки 15. Опрос ошибки формируется счетчиком 19 в реж 1мрсчитыванния р конце прохождения массива информации и подается в блок обнаружения ошибок 11 При отсутствии ошибок ипи в сигнала неисправимой ошибки повторное считывание с коррекцией информации не производится. Нсиспраьимяя опибка блвяет дв/х си- лов: если количество единиц в сумме массива . сспи отсутствую, единицы в сумме и имеется ошибка построчного контроля (состояние 1 триггер 26). Два вида неисправности объединяются в элементе 32, на который приходит также сигма разрешения.

Сигнал корректируемой ошибки 1-1 вырабатывается элементом И-НЕ 31, кэгда в сумме массива присутствует одня 1 При наличии коррелируемой ошибки т осжипе повторного считывания проис-ицит коррекция информации в блоке орр ч-ции 7

При этом информация в сумматоре 20 не суммируется, сумматор находится в состоянии, которое образовалось при первом считывании Это достигается тем, что коммутатор 8 отключен от сумматора.а старший разряд счетчика 19 управляет 3-м состоянием коммутатора Единица в сумме массива информации свидетельствует об ошибке в стопбце, с выхода сумматора 20 она посту0 лает на элементы И 10, где при повторном считывании складывается с единицей, которая появляется при ошибке в блоке построчного контроля 9. В это же время на вход блока коррекции 7 из накопителя приходит

5 слово, нуждающееся в коррекции. Бит информации, находящийся в месте пересечения неисправности по строке и столбцу, инвеотируетсч. Откорректированная информация проходит на выходы устройства

0 13

Формула изобретения Запоминающее устройство с исправлением ошибок, содержащее накопитель, адресные входы которого подключены к

5 выходам регистра адреса информационные входы которого являются адресными входами устройства, синхровход регистра адреса является входом обмена устройства и под- мкчен к входу выборки накопителя, вход

записи считывания которого является одно- .чменннм олодом устройства, информационные входы накопителя соединены с вилодами первого коммутатора, информационные входы первой группы которого

Ь подключены к выходам блока кодирования, входы которого являются информационными входами устройства и соединены с информационными входами второй группы первого коммутатора, выходы накопителя

0 подключены к входам блока построчного контроля и к входам первой группы блока коррекции, входы второй группы которого соединены с выходами элементов И группы, первые ч вторые входы которых подключе5 ны соответственно к выходу блока построчного контроля и к информационным входам фртьеи группы первого коммутатора, выходы блока коррекции являются информационными выходами устройства, отличаю0 щ е е с я тем, что, с целью повышения надежности, в устройство введены сумма- iOp, блок обнаружения ошибок, второй коммутатор и счетчик, причем вход сброса счетчика соединен с входами сброса сумма5 тора и блока обнаружения ошибок и является входом сброса устройства, установочный вход счетчика соединен с входом записи-считывания устройства, синх- счегчика подключен к входу обмена уг тройства, первый, оторой и третий выходы

счетчика подключены соответственно к входу разрешения выборки второго коммутатора, к входу разрешения блока обнаружения ошибок и к управляющему входу первого коммутатора, информационные входы первой группы второго коммутатора соединены с информационными входами устройства и с выходами блока кодирования, информационные входы второй группы, управляющий вход и выходы второго коммутатора подключены соответственно к выходам на

копителя, к входу записи-считывания устройства и к входам группы сумматора, выходы которого соединены с информационными входами третьей группы первого коммутатора и с информационными входами блока обнаружения ошибок, выходы которого являются выходами признаков корректируемой и некорректируемой ошибок устройства, выход блока построчного контроля подключен к установочному входу блока обнаружения ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1989 |

|

SU1649615A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1322379A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1649614A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти при блочной организации считывания информации. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель, регистр адреса, первый и второй коммутаторы, блок кодирования, блок коррекции, блок построчного контроля, блок обнаружения ошибок, сумматор, счетчик, группу элементов И. В режиме записи массива в устройстве формируются контрольные разряды по каждой строке (слову) и контрольная сумма массива. В режиме считывания данные о наличии ошибок при построчном контроле и текущая контрольная сумма массива поступают в блок обнаружения ошибок, формирующий сигналы корректируемой и некорректируемой ошибок. Для коррекции ошибок осуществляется повторное считывание массива. 3 ил.

От Юow22

Фиг.

К15

ОтМ

Фиг 2

фиг.З

.

| Авторское свидетельство СССР № 1276145 | |||

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1297120A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-07-30—Публикация

1989-04-11—Подача