Изобретение относится к автоматике и может быть использовано для управления различными объектами, в том числе радио- управля мими моделями.

Цель тобрэтения - повышение помехоустойчивости дешифратора.

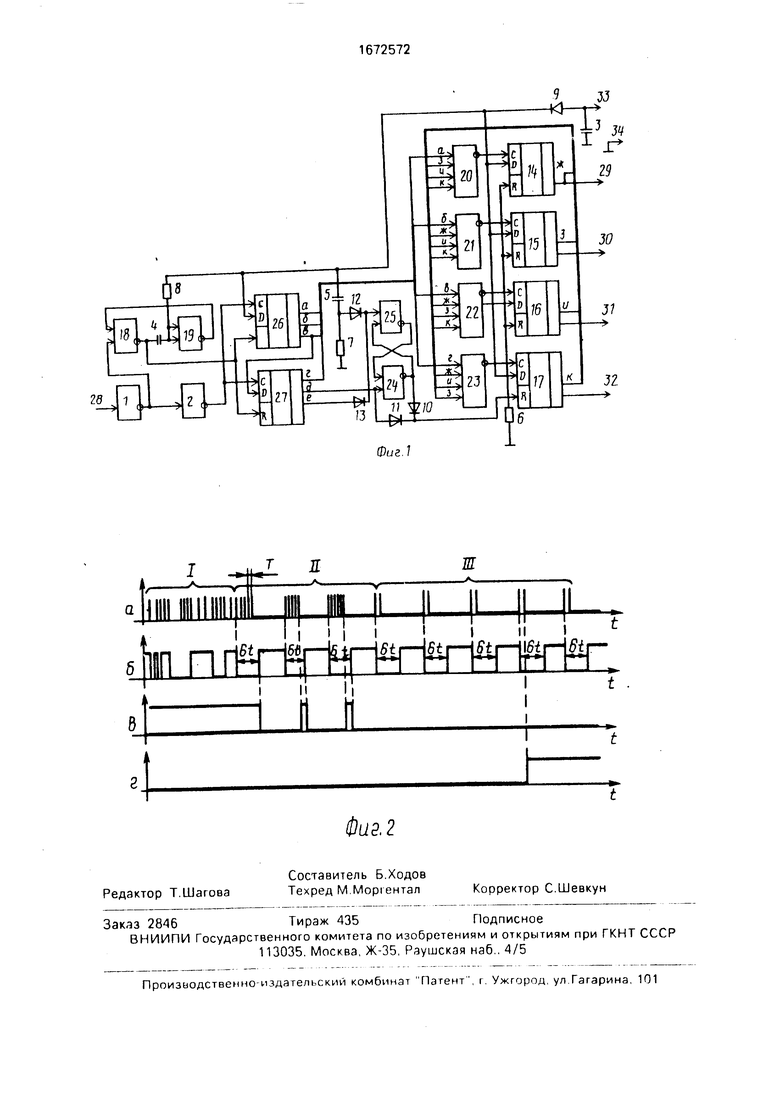

Hd фиг. 1 приведена принципиальная схема дешифратора; на фиг 2 приведены временные диаграммы, поясняющие-его работу.

Дешифратор содержит первый и второй инверторы 1 и 2, первый-третий накопительные элементы 3-5, первый-третий резистивные элементы 6-8, первый-пятый выпрямительные элементы 9 - 13, первый- четвертый сдвиговие регистры 14 - 17, пер- вый-восьмой элементы 18 - 25 ИЛИ-НЕ и пятый и шестой сдвиговые регистры 26 и 27. На фиг. 1 позицией 28 обозначен вход дешифратора, позициями 29-32 - соответственно лервый-четвертый выходы дешифратора, позициями 33 и 34 - соответственно иины положительного и нулевого потенциалов. На фиг 2 соответствующими индексами обозначены следующие сигналы: а сигнал на выходе инвертора 1; б - сиг нал на выходе элемента ИЛИ-НЕ 18; в - сигнал на R-входе регистров 14-17; г - сигнал на выходе регистра 14. Участок 1 характеризует дежурный режим работы дешифратора, участок I I характеризует режим Стоп, участок I I характеризует режимы Влево, Вправо, Вперед, Назад.

Дешифратор работает следующим образом.

Режим дежурный. На вход 28 дешифратора поступают шумы приемного устройства. При включении питания, по мере заряда накопительного элемента 5, на выходе элемента 24 ИЛИ-НЕ формируется сигнал логической 1, который через выпрямительный элемент 10 поступает на R-входы регистров 14-17, устанавливая их в исходное состояние. На выходах 29-32 дешифратора формируется сигнал, соответствующий уровню логического О. В дальнейшем элемент 5 разряжается через резистивный элемент 7, Шумы приемного устройстве через инвертор 1 поступают на инвертор 2 и одно вибратор (выполненный на элементах 4, 8,

Ил

1C

18 19) С выхода инвертора 2 шумовой сигнал поступает на С-входы регистров 26 и 27, на R-входы которых поступает сигнал с выхода элемента 18. Если с выхода инвертора 1 поступают два, три, четыре, пять и шесть импульсов, то на входе элемента 18 формируется импульс длительностью 6Т. Так как входной шумовой сигнал представляет собой случайный сигнал, то на выходе элемента 18 формируются сигналы с различной длительностью. На С-входы регистров 26 и 27 поступают группы импульсов, состоящие из произвольного числа импульсов, что приводит к формированию на выходах 29 - 32 ложных команд, Если на R-входах pei истров 26 и 27 присутствует логический О, а на С-входах присутствует первый импульс с выхода инвертора 2, то на первом выходе регистра 26 (являющимся выходом второго разряда) по-прежнему наблюдается логический О. При поступлении второго, третьего, четвертого и пятого входных импульсов на соответствующих выходах регистров 26 и 27 последовательно формируются логические 1, которые, в свою очередь, вызывают появление логического О на выходах соответствующих элементов 20 - 23. Однако, в связи с тем. что на R-входах регистров присутствует логическая V, то их состояние (лог. О) не изменяется. Если за пятым входным импульсом наступает пауза, то на выходе элемента 18 формируется логическая 1, регист ры 26 и 27 устанавливаются в исходное состояние, на выходах элементов 20 - 2.3 устанавливаются логические 1. Цикл работы дешифратора заканчивается. При поступлении на вход 28 шести шумовых импульсов сигнал логической I формируется на втором выходе регистра 27, который поступает на соответствующий вход элемента 24 и анод элемента I I. Этот сигнал вызывает появление логического О на выходе элемента 24, однако на R-входы регистров 14 - 17 по-прежнему подается (через элемент I) логическая 1. В конце цикла на R-входах регистров 26 и 27 формируется логическая 1, что вызывает появление на их выходах сигнал логического О. Аналогичный сигнал формируется на R-входах регист ров 14 - 17. На выходах элементов 20 - 23 формируются сигналы логической 1. Так как смена сигналов на выходах элементов 20 23 и R-входах регистров 14 - 17 происходит одновременно, то на выходах последних смены сигналов не происходит, но регистры 14 - 17 готовы к работе Выход регистра 14 и первые выходы регистров 15 - 1 1 являются выходом четвертого разряда (вторые выходы - выходы третьего разряда)

Режим Стоп без помех. В этом режиме дешифратор начинает работу из дежурного режима. На вход 28 поступает пакет из шести импульсов, скважность которых равна

двум. На выходе элемента 18 формируется сигнал длительностью 6Т, поступающий на R-входы регистров 26 и 27. Пять импульсов этою пакета не вызывает изменения сигналов на выходах 29 - 32. Шестой импульс

пакета формирует на выходе элемента 24 сигнал логического О. В момент окончания цикла уровень логического О поступает на R-входы регистров 14 - 17. Пять импульсов второго пакета не вызывают изменения сигналов на выходах 29 - 32. Шестой импульс этого пакета стирает информацию, записанную в эти регистры. Последующие пакеты импульсов вызывают аналогичную реакцию дешифратора.

Режим Стоп с помехой. Если к третьему пакету импульсов добавить дополнительный импульс помехи, то он вызывает появление сигнала на третьем выходе регистра 27, который формирует на выходе элемента 24 сигнал логической 1, Этот уровень сохраняется до конца четвертою цикла. При поступлении последующих пакетов импульсов работа дешифратора соответствует второму циклу режима Стоп без

помех.

Режим Влево без помех. В этом режиме пакеты импульсов содержат по два импульса. На четвертом цикле на выходе 29 формируется сигнал команды. При режиме

Влево с помехой дешифратор переходит в кратковременный режим Стоп, а через четыре пакета команды Влево без помех дешифратор выполняет намеченную команду. Режим Вправо без помех Ь этом режиме в пакете импульсов содержится три импульса, а сигнал команды формируется на выходе 30.

Режим Вперед без помех. В этом режиме в пакете импульсов содержится четы5 ре импульса, а сигнал команды формируется на выходе 31.

Режим Назад без помех. В этом режиме в пакете импульсов содержится пять импульсов, а сигнал команды формируется на

0 выходе 31.

Режимы Вправо, Впэред и Назад с помехой имеют алгоритм работы аналогич ный режиму Влево с помехой.

5Формула изобретения

Пятикомандный дешифратор для радиоуправляемой модели, содержащий инверторы, накопительные элементы, резистивные элементы, выпрьми-ельные

элементы, первый - четвертый сдвиговые регистры, D-входы которых объединены и подключены к катоду первого выпрямительного элемента, анод которого соединен с первым выводом первого накопительного элемента и подключен к шине положительного потенциала, второй вывод первого накопительного элемента и первые выводы первого и второго резистивных элементов соединены с шиной нулевого потенциала, катоды второго и третьего выпрямительных элементов объединены с вторым выводом первого резистивного элемента и подключены к R-входу четвертого сдвигового регистра, катоды четвертого и пятого выпрямительных элементов объединены, вход первого инвертора является входом дешифратора, выход первого сдвигового регистра и первые выходы второго - четвертого регистров являются соответственно первым - четвертым выходами дешифратора, отличающийся тем, что, с целью повышения помехоустойчивости дешифратора, в него введены первый - восьмой элементы ИЛИ-НЕ и пятый и шестой сдви- говые регистры, выход первого элемента ИЛИ-НЕ соединен с первым выводом второго накопительного элемента и R-входами пятого и шестого сдвиговых регистров второй вывод второго накопительного элемен- та соединен с первым выводом третьего резистивного элемента и первым и вторым входами второго элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого обьединен с входом второго инвертора и подключен к выходу первого инвертора, выход второго инвертора соединен с С-входом пятого и шестого сдвиговых регистров, перпый и второй выходы пятого сдвигово- го регистра соединены с первыми входами соответственно третьего и четвертого элементов ИЛИ-НЕ. выходы которых соединены с С-входами соответственно первого и второго сдвиговых регистров, третий выход

пятого сдвигового регистра соединен с D- входом шестого сдвигового регистра и первым входом пятого элемента ИЛИ-НЕ, выход которого соединен с С-входом третьего сдвигового регистра, первый выход шестого сдвигового регистра соединен с первым входом шестого элемента ИЛИ-НЕ, выход которого соединен с С-входом четвертого сдвигового регистра, R-входы первого - третьего сдвиговых регистров подключены к R-входу четвертого сдвигового регистра, второй выход шестого сдвигового регистра соединен с анодом третьего выпрямительного элемента и первым входом седьмого элемента ИЛИ-НЕ, выход которого соединен с анодом второго выпрямительного элемента и первым входом восьмого элемента ИЛИ-НЕ, выход которого соединен с вторым входом седьмого элемента ИЛИ-НЕ, второй вход восьмого элемента ИЛИ-НЕ подключен к катоду четвертого выпрямительного элемента, анод которого соединен с вторым выводом второго резистивного элемента и первым выводом третьего накопительного элемента, второй вывод которого объединен с вторым выводом третьего резистивного элемента, D-входом пятого сдвигового регистра и подключен к катоду первого выпрямительного элемента, третий выход шестого сдвигового регистра соединен с анодом пятого выпрямительного элемента, вторые входы четвертого - шестого элементов ИЛИ-НЕ подключены к выходу первого сдвигового регистра, второй выход второго сдвигового регистра соединен с вторым входом третьего элемента ИЛИ-НЕ, третьими входами пятого и шестого элементов ИЛИ- НЕ, второй выход третьего сдвигового регистра соединен с третьими входами третьего и четвертого элементов ИЛИ-НЕ и четвертым входом шестого элемента ИЛИ-НЕ, второй выход четвертого сдвигового регистра соединен с четвертыми входами третьего - пятого элементов ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления радиоуправляемой моделью | 1988 |

|

SU1586733A1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| Запоминающее устройство | 1989 |

|

SU1718272A1 |

| Устройство для формирования синхро-СигНАлОВ | 1979 |

|

SU849187A1 |

| Детектор экстрасистол | 1985 |

|

SU1377030A1 |

| Устройство защиты от импульсных помех | 1986 |

|

SU1408533A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для обмена информацией | 1986 |

|

SU1424001A1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

Изобретение относится к автоматике и может быть использовано для управления различными объектами, в том числе радиоуправляемыми моделями. Цель изобретения - предотвращение ложные срабатывания дешифратора при отсутствии на его входах полезного сигнала, что обеспечивает повышение помехоустойчивости дешифратора. Пятикомандный дешифратор для радиоуправляемой модели содержит инверторы 1 и 2, накопительные элементы 3 - 5, резистивные элементы 6 - 8, выпрямительные элементы 9 - 13, сдвиговые регистры 14 - 17, 26, 27, элементы ИЛИ-НЕ 18 - 25. 2 ил.

| Дешифратор команд для радиоуправляемой модели | 1985 |

|

SU1377134A1 |

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

Авторы

Даты

1991-08-23—Публикация

1988-09-23—Подача