(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИНХРОСИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

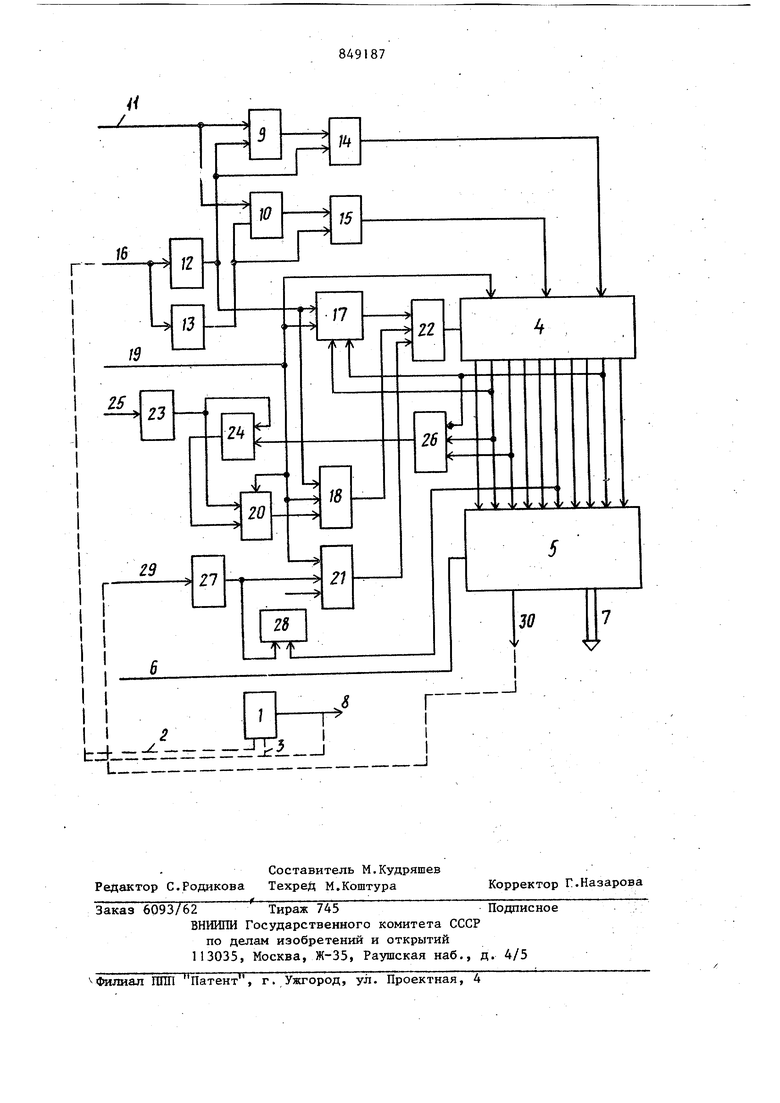

Изобретение предназначено для ис пользования в вычислительной техник в частности в синхронных микропро цессорных устройствах обработки информации, которые вьшолняют необход мые операции с помощью синхронизирующих импульсов. Известно устройство генерации уп равляющих синхросигналов , реализованное в интегральном исполнении на одном полупроводниковом кристалле и включающее схемы для обеспечения сброса системы. Генератор-форми рователь вьщает строб состояния и обеспечивает синхронизацию чтения центральным процессором команд и да ных f 1 . Однако стрзгктурная организация такого устройства не ориентирована на применение его в других микропроцессорных системах или других синхронных устройствах обработки информации. Наиболее близким к предлагаемому по технической сущности является генератор синхроимпульсов, предназначенный для обеспечения синхрони- зирую1цими последовательностями микропроцессорной системы. В генератор синхроимпульсов входит сдвиговый регистр, внутренний генератор тактовых импульсов, кварцевый резонатор, внешнее управление, дешифратор состояний сдвигового регистра, схема работы по шагам, схема сброса Недостатком известного генератора является ограниченные функциональные возможности, так как с помо|цью этого устройства можно получить только две фазы синхросигналов. Цель изобретения - расширение функциональных возможностей устройства за счет возможности запоминания состоянийсоответствующего информационного выхода устройства и возможности работ по циклам. Поставленная цель достигается тем, что в устройство для формирования синхросигналов, содержащее внутренний генератор тактовых импульсов, сдвиговый регистр, дешифратор состояний, причем выход дешифратора является информационным выходом устройства, группа разрядных выходов сдвигового регистра соединена с груп пой входов дешифратора состояний, введены шесть триггеров, три элемента НЕ, повторитель, два элемента И, четыре элемента И-НЕ, причем нулевой вход первого триггера соединен с входом прерьшаний устройства и с нулевым входом второго триггера, вход синхронизации устройства через первый элемент НЕ соединен с входом синхронизации первого триггера, с первым входом первого элемента И, с единичным входом третьего триггера и с единичным входом четвертого триггера, вход синхронизации устройства через повторитель соединен с входом синхронизации второго триггера и с первым входом второго элемента И, вход сброса устройства соединен с входом сброса сдвигового регистра с входом сброса третьего, четвертогот, пятого и шестого триггеров, вход запуска устройства через второй элемент НЕ соединен с первым входом первого элемента И-НЕ и с единичным входом пятого триггера, вход конца цикла устройства соединен .с выходом конца цикла дешифратора состояний и через элемент НЕ с управляющим входом шестого триггера и с первым входом второго элемента И-НЕ, разрешающий вход устройства соединен с упр ляющим входом дешифратора состояний, вторые входы первого и второго элементов И соединены соответственн с вьрсодами первого и второго тригге ров , выход первого элемента И соеди нен с первым информационным входом сдвигового регистра, выход второго элемента И соединен со вторым информационным входом сдвигового регистра, выход третьего триггера сое динен с первым входом третьего элемента И-НЕ, второй вход третьего эл мента И-НЕ соединен с выходом четве того триггера, третий вход третьего элемента И-НЕ соединен с выходом шестого триггера, выход третьего элемента И-НЕ соединен с управляющи входом сдвигового регистра, единичный вход третьего триггера соединен 74 с первым выходом группы выходом сдвигового регистра и с первым входом четвертого элемента И-НЕ, нулевой вход третьего триггера соединен со вторым ВЫХОДОМ труппы ВЫХОДОМ сдвигового регистра и с первым входом четвертого элемента И-НЕ, третий выход группы выходом сдвигового регистра соединен с третьим входом четвертого элемента , четвертый выход группы выходов сдвигового регистра соединен со вторым входом второго элемента И-НЕ, выход четвертого элемента И-НЕ соединен со вторым входом первого элемента И-НЕ, выход пятого триггера соединён с единичным входом четвертого триггера, выход второго элемента И-НЕ соединен с единичным входом шестого триггера, выход первого элемента И-НЕ соединен с нулевым входом пятого триггера, выход внутреннего генератора тактовых импульсов соединен с тактовым выходом устройства и с входом синхронизации устройства, управляющий выход конца цикла дешифратора соединен с выходом конца цикла устройства. На чертеже приведена схема предлагаемого устройства. Устройство содержит внутренний генератор 1 тактовых импульсов с выводами 2 и 3 для подключения кварцевого резонатора, сдвиговый регистр 4, дешифратор 5 состояний, выход 6 внешнего управления, выходы 7 генерируемых синхросигналов, управляющий выход 8, триггеры 9 и 10, внешний вход II прерывания, элемент НЕ 12, повторитель 13, элементы И 14 и 15, вход 16 синхронизации, триггер 17, триггер 18, вход 19 сброса, триг- гер 20, триггер 21, элемент И-НЕ 22, элемент НЕ 23, элемент И-НЕ 24, вход 25 запуска, элемент И-НЕ 26, элемент НЕ 27,- элемент И-НЕ 28, упра.вляющий вход 29 устройства, вход 30 конца цикла работы сдвигового регистра. Устройство работает следующим образом. На вход Ь6 поступают тактовые импульсы либо с выхода 8, либо от внешнего генератора тактовых импульсов. После прохождения элемента НЕ 12 и повторителя 13 инверсное и прямое значения входных тактовых импульсов поступает соответственно на первые | .входы элемента И 14 и элемента И 15, которые стробируются соответственно выходами триггеров 9 и 10. С выходо элемента И 1.4 и элемента И 15 параф1азные тактовые импульсы поступают на синхронизирующие входы сдвигового регистра 4, который с поступлени ем тактовых импульсов начинает осуществлять сдвиг информации, поступа ющей на информационный вход сдвигов го регистра 4 с выхода элемента . , И-НЕ 22, три входа Которого подключены соответственно к выходам триггера 17, триггера 18 и триггера 21. Информация с выходом сдвигового регистра 4 поступает на входы дешифратора 5 состояний, в котором шабл ном металлизации запрограммированы генерируемые устройством управляющие синхросигналы на выходах 7 и выходной сигнал конца цикла работы сд гового регистра 4 на выходе 30 устройства. Вход 6 внешнего управления дешифратором 5 состояний позволяет наст ивать устройство на генерацию одного из двух вариантов генерируемых устройством синхросигналов на выходах 7 и запрограммированных одним шаблоном металлизации. Вход сброса 19 предназначен для приведения устройства в исходное состояние, т.е. для подготовки его к работе посредством подключения к входу сброса 19 внешнего сигнала сб са. Уровнем логического нуля внешне го сигнала сброса происходит устано ка в единичное состояния триггеров сдвигового регистра 4, триггера 17, триггера 21 и сброс в нулевое состо ние триггеров 18 и 20, В таком случае на выходе элемента И-НЕ 22 присутствует уровень логической еди ницы, т.е. эта схема оказьшается закрытой сигналом с уровнем логического нуля с выхода триггера 18 и на всех выходах сдвигового регистра 4 присутствует уровень логической еди ницы, т.е. устройство не генерирует управляющие синхросигналы на выходах 30, если даже на синхронизирующие входы сдвигового регистра 4 и поступают парафазные тактовые импульсы с выходом элемента И 14, и элемента И 15. Единичным значением внешнего сигнала запуска, поступающего на вход 25 запуска, производится установка асинхронного триггера 20 запуска в единичное состояние. По заднему фронту тактового импульса, поступающе- , го на синхронизирующий вход триггера 18 запуска с выхода инвертора 12 происходит,запись состояния триггера 20 в триггер 18, и с этого момента на выходе элемента И-НЕ 22 устанавливается уровень логического нуля при условии, что в триггеры 17 и 21 записана логическая единица. Единичными значениями парафазных тактовых импульсов, поступающих на синхронизирующие входы сдвигового регистра 4 с выходов элементов И 14 и I5 в сдвиговом регистре 4, происходит сдвиг информации, поступающей на сдвиговый регистр 4 с выхода элемента И-НЕ 22, и на выходах сдвигового регистра 4 формируются сигналы с уровнем логического нуля с длительностью, равной периоду входным тактовых импульсов и сдвинутые один относительно другого на 1/2 периода входной тактовой серии. На выходах 7 устройства формируются управляющие синхросигналы, а на выходе 30 - сигнал с уровнем логической единицы конца цикла работы сдвигового регистра 4. Заданный режим работы сдвигового регистра 4 обеспечивается тем, что сбросовый вход триггера I7 подключен ко второму выходу сдвигового регистра 4, а информационный вход этого триггера - к девятому выходу сдвигового регистра 4. Для запуска устройства на непрерывный режим генерации управляющих синхросигналов необходимо присутствие на входе 25 запуска сигнала с уровнем логической единицы в течение всего времени работы, а на входе 29 запуска - сигнала с уровнен логической единицы или в течение всего времени работы устройства, или на вход 29 должен поступать единичный сигнал в конце каждого цикла работы устройства. Для входа 29 запуска этим сигналом может быть сигнал с выхода 30 конца цикла работы сдвигового регистра. После подачи сигнала на вывод 25 запуска и начала генерации устройстве управляющих синхросигналов на выходах 7-с помощью элементов И-НЕ 24 и 26 и сигналов со второго, восьмого и девятого выходов сдвигового регистра 4 осуществляется анаЛИЗ наличия сигнала запуска на выходе 25 устройства. Если сигнал запуска на входе 25 присутствует, то устройство продолжает генерацию управляющих синхросигналов на выводах 7, если же он отсутствует, то по окончании текущего цикла работы сдвигового регистра 4 ге.нерадия управляющих синхросигналов прекращается.

Происходит это следующим образом, При отсутствии сигнала запуска на входе 25 запуска происходит сброс в нуль асинхронного триггера 20, его состояние записьюается в синхронный триггер 18, элемент И-НЕ 22 закрывается, т.е. на ее выходе присутствует логическая единица и по окончании текущего цикла работы устройства на всех выходах сдвигового регистра 4 будет присутствовать логическая единица, т.е. формирования сдвину тых сигналов с уровнем логического нуля на выходах сдвигового регистра 4 производиться не будет.

Вход 1 1 прерывания служит для пре рывания генерации управляющих синхросигналов на выходах 7 устройства в любом месте цикла генерации с последующим продолжением генерации прерыванных последовательностей управлякхЦих синхросигналов путем подачи на вход 11 прерьшания внешнего сигнала прерывания. Для прерывания генерации синхросигналов необходи МО на вывод 1I прерывания подать низ кий уровень сигнала прерывания, который по задним фронтам тактовых импульсов с выходом элемента НЕ 12 и повторителя I3 записывается в триггеры 9 и 10, после чего будут закрыты элемент И 14 и элемент И 15, т.е. на синхронизирующие входы сдвигового ре1 истра 4 прекращается поступление тактовых импульсов с выходов элементов И 14 и 15, что приводи к тому, что сдвиговый регистр 4 прекращает изменение своего состояния, т.е. произойдет замор 1живание выхоных синхросигналов на выходах 7 устройства.

Для дальнейшего продолжения генерции управляющих синхросигналов на выводах 7 необходимо на вАод 11 прерывания подать единичным значение сигнала прерывания, который записывается в триггеры 9 и 10, открываются элементы И 14 и 15, на синхронизирующие входы сдвигового регистра

4 продолжается поступление тактовых импульсав, а на выходах 7 устройства продолжается генерация управляющих синхросигналов.

Таким образом, предлагаемая структурная организация устройства для формирования синхросигналов для микропроцессоров позволяет расширить функциональные возможности устройства, распшрить область его применения практически на любую синхронную микропроцессорную вычислительную систему. Применение предлагаемого устройства сокращает количество микросхем при проектировании устройства синхронизации, повьш1ает надежность и степень микроминиатюризации микропроцессорных вычислительных систем.

Формула изобретения

Устройство для формирования синхрсигналов, содержащее внутренний генератор тактовых импульсов, сдвиговый регистр, дешифратор состояний, причем выход дешифратора состояний является информационным выходом устройства, группа разрядньгх выходов сдвигового регистра соединена с группой входов дешифратора состояний, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности запоминания состояний соответствующего информационного выхода устройства и возможности работы по циклам, устройство содержит шесть триггеров, три элемента НЕ, повторитель, два элемента И,, четыре элемента И-НЕ, причем нулевой вход первого триггера соединен с входом прерываний устройства и с нулевым входом второго триггера, вход синхронизации устройства через первый элемент НЕ соединен с входом синхронизации первого триггера, с первым входом первого элмента И,.с единичным входом третьего триггера и с единичным входом четвертого триггера, вход синхронизации устройства через повторитель соединен с входом синхронизации второго триггера и с первым входом второго элемента И, вход сброса устройства соединен с входом сброса сдвигового регистра, с .входом сброса треТьего, четвертого, пятого и шестого

триггеров, вход запуска устройства через второй элемент НЕ соединен с первым входом первого элемента И-НЕ и с единичньм входом пятого триггера, вход конца цикла устройства соединен с выходом конца цикла дешифратора состояний и через элемент НЕ с управляющим входом шестого триггера и с первым входов второго элемента И-НЕ, разрешающий вход устройства соединен с управляюпщм входом дешифратора состояний, вторые входы первого и второго элементов И соединены соответственно с выходами первого и второго триггеров, выход первого элемента И соединен с первым информационным входом сдвигового регистра, выход второго элемента И соединен со вторым информационным входом сдвигового регистра, выход третьего триггера соединен с первым входом третьего элемента И-НЕ, второй вход третьего элемента И-НЕ соединен с выходом четвертого триггера, третий вход третьего элемента И-НЕ соединен с выходом шестого триггера, выход третьего элемента И-НЕ соединен с управляющим входом сдвигового регистра, единичный вход третьего триггера соединен с .первым выходом группы выходом сдвигового регистра и с первым

входом четвертого элемента И-НЕ, нулевой вход третьего триггера соединен со вторым выходом группы выходом сдвигового регистра и с первым входом четвертого элемента И-НЕ, третий выход группы выходом сдвигового регистра соединен с третьим входом четвертого элемента И-НЕ, четвертый выход группы выходов сдвигового регистра соединен со вторым входом второго элемента И-НЕ, выход четвертого элемента И-НЕ соединен со вторым входом первого элемента И-НЕ, выход пятого триггера соединен с единичным входом четвертого триггера, выход второго элемента И-НЕ соединен с единичным входом шестого триггера, выход первого элемента И-НЕ соединен с нулевым входом пятого триггера, выход внутреннего генератора тактовых импульсов соединен с тактовым выходом устройства и с уходом синхронизации устройства, управляющий выход конца цикла дешифратора состояний соединен с выходом конца цикла устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-07-23—Публикация

1979-10-08—Подача