cm н L йчн

00

ю

XI

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1976 |

|

SU670935A1 |

| Устройство для обмена информацией | 1982 |

|

SU1091151A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2029352C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

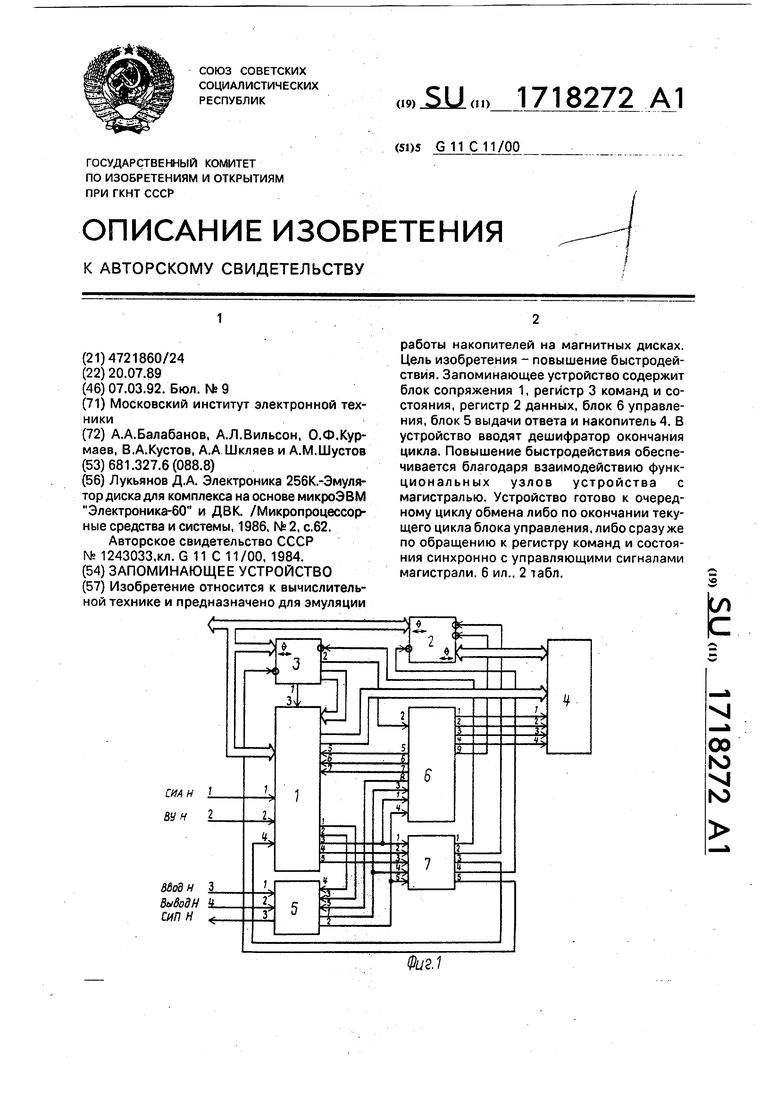

Изобретение относится к вычислительной технике и предназначено для эмуляции работы накопителей на магнитных дисках. Цель изобретения - повышение быстродействия. Запоминающее устройство содержит блок сопряжения 1, регистр 3 команд и состояния, регистр 2 данных, блок 6 управления, блок 5 выдачи ответа и накопитель 4. В устройство вводят дешифратор окончания цикла. Повышение быстродействия обеспечивается благодаря взаимодействию функциональных узлов устройства с магистралью. Устройство готово к очередному циклу обмена либо по окончании текущего цикла блока управления, либо сразу же по обращению к регистру команд и состояния синхронно с управляющими сигналами магистрали. 6 ил., 2 табл. w fe

Выводи i. сип н

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и предназначено для эмуляции работы накопителей на магнитных дисках.

Оперативные запоминающие устройства, эмулирующие работу накопителей на магнитных дисках (электронные квазидиски), существенно повышают производительность микроЭВМ, оснащенной гибкими магнитными дисками в качестве внешней памяти, позволяют уменьшить износ магнитных носителей и, следовательно, увеличить надежность работы микроЭВМ,

Известны устройства, которые могут эмулировать работу накопителей на магнитных дисках. Эти устройства позволяют повысить производительность микроЭВМ, имеют значительный объем памяти и эффективные способы адресации (метод окна). Однако, значительные габариты и высокое энергопотребление ограничивают их применение в составе микроЭВМ.

Известно устройство, содержащее магистральные приемники, устройства обмена информацией, селектор адреса, узел регенерации и управления, блок дешифрации кода операции, регистр номера дорожки и сектора, перкодировщик, схему контроля на нечетность, регистры ошибок, регистр адре- са вектора прерываний и накопитель.

Недостатком указанного устройства является малое быстродействие, ограниченное пропускной способностью интерфейса накопителя на гибких магнитных дисках (ГМД7012).

Известно также устройство, содержащее приемопередатчики магистрали, дешифратор адреса ОЗУ, регистры состояния ОЗУ, генератор паритета, устройство конт- роля паритета, выходной регистр-защелку, селектор выбора ОЗУ, регистр-мультиплексор адреса, приемопередатчики сигналов управления, устройство записи, чтения и выработки временных интервалов, устрой- ство регенерации и накопитель.

Недостатком данного устройства является невозможность применения эффективного метода адресации (метод окна).

Наиболее близким по технической сущ- ности и достигаемому результату к предлагаемому является устройство, содержащее накопитель, регистр данных и блок управления, причем входы и выходы регистра данных, входы и выходы первой группы блока управления являются одними из информа- ционых и адресных входов и выходов устройства, другими информационными входами и выходами которого являются информационные входы и выходы накопителя,

а тактовыми входами - входы синхронизации блока управления, одни из выходов первой группы которого соединены соответственно с первым управляющим входом регистра данных, одними из управляющих и адресных входов накопителя, регистр команд и состояния, блок выдачи ответа, формирователь одиночных импульсов, элемент НЕ, накопительный элемент и ограничительный элемент, причем первый выход формирователя одиночных импульсов подключен к входу элемента НЕ, второй выход - к первому выводу накопительного элемента, а третий выход - к второму выводу накопительного элемента и первому выводу ограничительного элемента, входы регистра команд и состояния подключены к одним из входов регистра данных, выходы регистра команд и состояния соединены с входами второй группы блока управления, первый управляющий вход регистра команд и состояния подключен к первому входу синхронизации блока управления, первый и второй выходы блока выдачи ответа соединены соответственно с вторым управляющим входом регистра команд и состояния, одним из входов третьей группы блока управления и вторым управляющим входом регистра данных, входы блока выдачи ответа подключены к одним из выходов второй группы блока управления, другие выходы второй группы которого соединены соответственно с третьим управляющим входом регистра состояния, прямым и инверсным входами формирователя одиночных импульсов, другие адресные входы накопителя подключены к другим выходам первой группы блока управления, вход сброса которого соединен с выходом элем.ента НЕ. одни из выходов регистра команд и состояния являются другими адресными выходами устройства, установочные входы регистра команд и состояния и другие входы третьей группы блока управления являются управляющими входами устройства, выходы с второго по шестой блока выдачи ответа и другие выходы регистра команд и состояния являются управляющими выходами устройства, второй вывод ограничительного элемента и вход стробирования формирователя одиночных импульсов являются входами питания устройства. Блок выдачи ответа содержит элементы И с первого по пятый, элементы ИЛИ и элементы И-НЕ, причем первый вход первого элемента И соединен с первыми входами второго и четвертого элементов И, вторыз входы которых подключены соответственно к выходу первого элемента И-НЕ и выходу третьего элемента И, первый вход которого соединен с выходом второго И-НЕ, первый вход которого подключен к выходу первого элемента ИЛИ, первый вход которого является первым входом блока, вторым входом которого являются первые входы первого элемента И-НЕ, пятого элемента И и второй вход первого элемента ИЛИ, третьим и четвертым входами блока являются соответственно первый вход первого элемента И, вторые входы элементов И-НЕ и пятого элемента И, входами с пятого по десятый блока являются соответственно второй вход первого элемента И и первый вход второго элемента ИЛИ, вто рой вход третьего элемента И, третий вход первого элемента И, второй вход второго элемента ИЛИ, третий вход третьего элемента И и третий вход второго элемента И, выходами блока с первого по шестой являются соответственно второй выход третьего элемента И, выходы первого и четвертого элементов И, выходы второго элемента ИЛИ второго и пятого элементов И.

Однако этому устройству присущ ряд недостатков. Во-первых, недостаточное быстродействие. Формирование некоторых управляющих сигналов, например сигнала КЭС, осуществляется ждущим мультивибратором. Последний вырабатывает импульс длительностью гарантированно превышающий длительность переходных процессов в накопителе. Поскольку длительность переходных процессов в накопителе зависит от внешних условий, например от температуры, то длительность импульса выбирается по наихудшему случаю с не всегда оправданным запасом. Таким образом, сам принцип схемотехнической реализации данного устройства предусматривает снижение быстродействия.

Целью изобретения является повышение быстродействия,

Для этого в запоминающее устройство, содержащее регистр команд и состояния, регистр данных, блок управления, блок выдачи ответа, накопитель и блок сопряжения, адресные входы первой группы которого соединены с информационными входами-выходамирегистраданных, информационными входами-выходами регистра команд и состояния и являются адресными и информационными входами-выходами устройства, адресные выходы блока сопряжения соединены с адресными входами накопителя, первый и второй входы блока сопряжения являются соответственно входом синхронизации устройства и входом выбора устройства, первый и второй входы блока выдачи ответа являются соответственно входами ввода и вывода устройства, первый, второй, третий

и четвертый выходы блока управления соединены соответственно с входом выборки строк, входом задания режима, первым и вторым входами выборки столбцов накопителя, третий выход блока выдачи ответа является выходом синхронизации устройства, введен дешифратор окончания цикла, адресные входы второй группы блока сопряжения соединены с выходами группы

0 регистра команд и состояния, пятый, шестой и седьмой входы блока сопряжения соединены с пятым, шестым и седьмым выходами блока управления соответственно, третий вход блока сопряжения соединен

5с первым выходом регистра команд и состояния, первый выход блока сопряжения соединен с третьим входом блока выдачи ответа, второй выход блока сопряжения соединен с входом обращения блока управле0 ния и первым входом дешифратора окончания цикла, третий выход блока сопряжения соединен с четвертым входом блока выдачи ответа, четвертый и пятый выходы блока сопряжения соединены с вторым и

5 третьим входами дешифратора окончания цикла соответственно, входы-выходы второй группы регистра данных соединены с информационными входами-выходами накопителя, второй выход регистра команд и

0 состояния соединен с входом задания режима блока управления, входы чтения и записи блока управления соединены соответственно с первым и вторым выходами блока выдачи ответа и четвертым и пятым входами

5 дешифратора окончания цикла, восьмой выход блока управления соединен с пятым входом блока выдачи ответа, девятый выход блока управления соединен с вторым входом управления записью регистра данных.

0 первый выход дешифратора окончания цикла соединен с входом управления записью регистра команд и состояния, третий выход дешифратора окончания цикла соединен с четвертым входом блока сопряжения, вто5 рой выход дешифратора окончания цикла соединен с первым входом управления записью регистра данных, четвертый выход дешифратора окончания цикла соединен с входом задания режима регистра данных.

0 пятый выход дешифратора окончания цикла соединен с входом задания режима регистра команд и состояния.

В предложенном устройстве осуществляется асинхронный обмен между магист5 ралью и блоком управления и синхронный обмен между магистралью и регистром команд и состояния. Устройство готово к очередному циклу обмена либо по окончании текущего цикла блока управления, либо сразу же по обращению к регистру команд и

состояния синхронно с управляющими сигналами магистрали, В отличие от известного устройства, где готовность устройства к новому циклу обмена определяется длительностью импульса на выходе ждущего мультивибратора, в предложенном устройстве готовность устройства к новому циклу определяет дешифратор окончания цикла, который позволяет повысить быстродействие, исключает ложные срабатывания, уменьшает зависимость от внешних дестабилизирующих факторов.

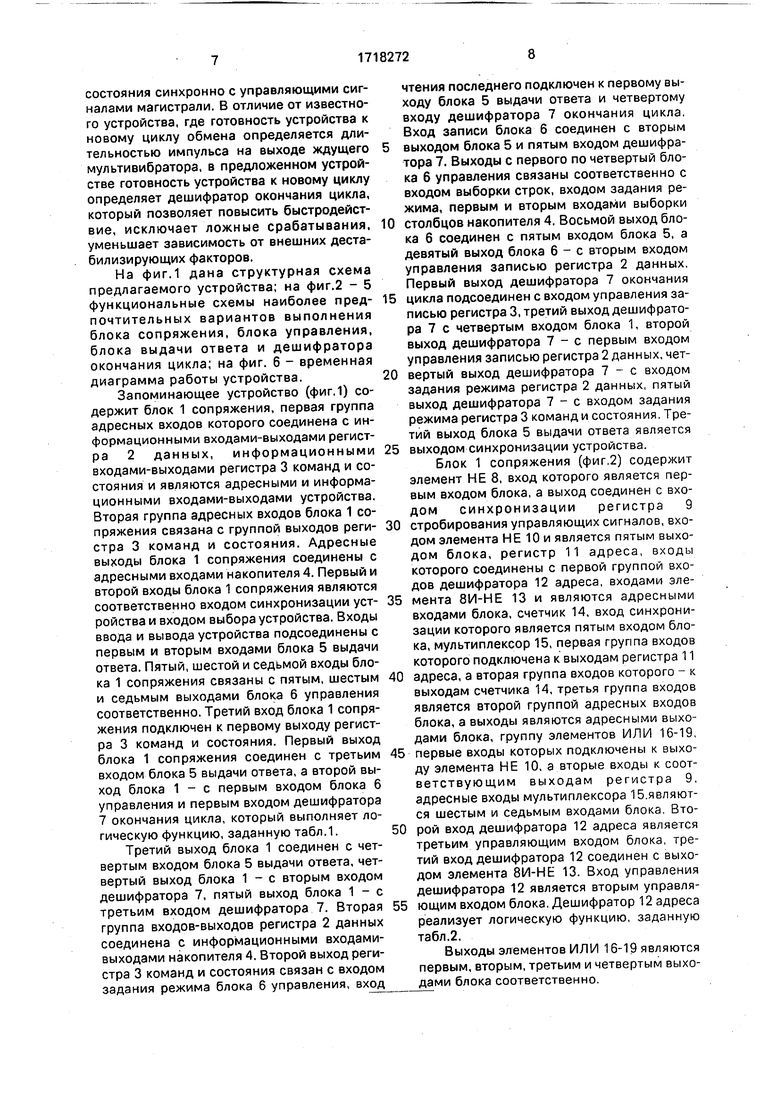

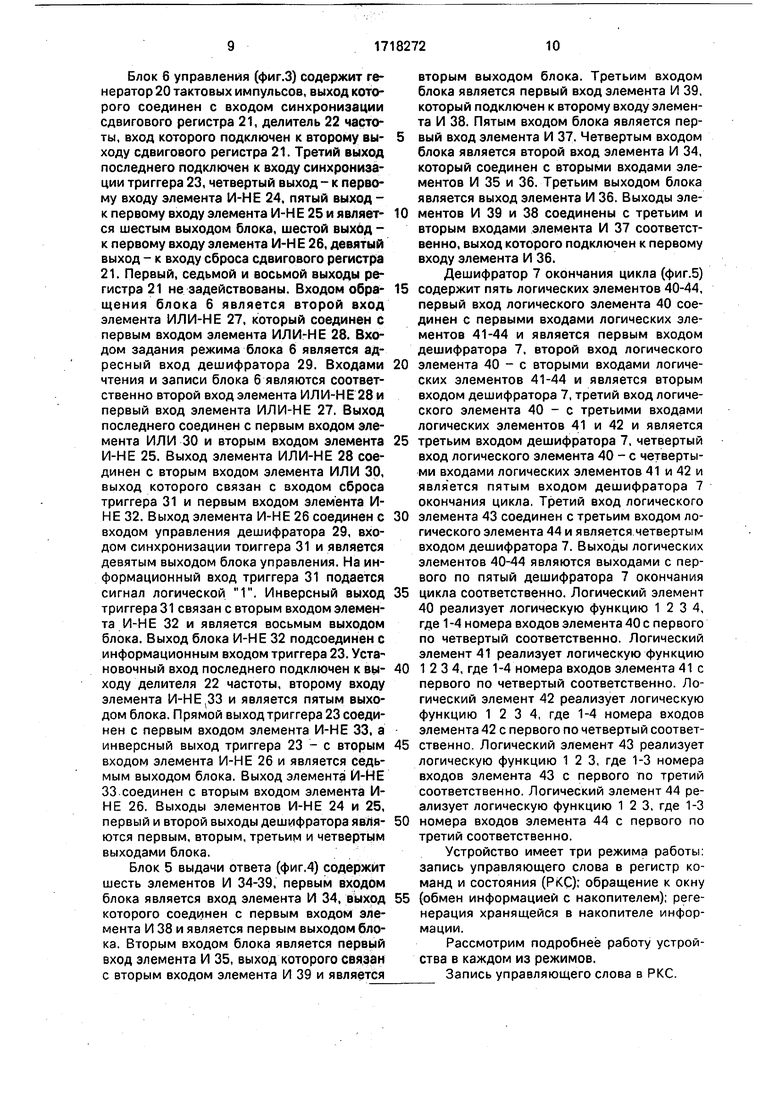

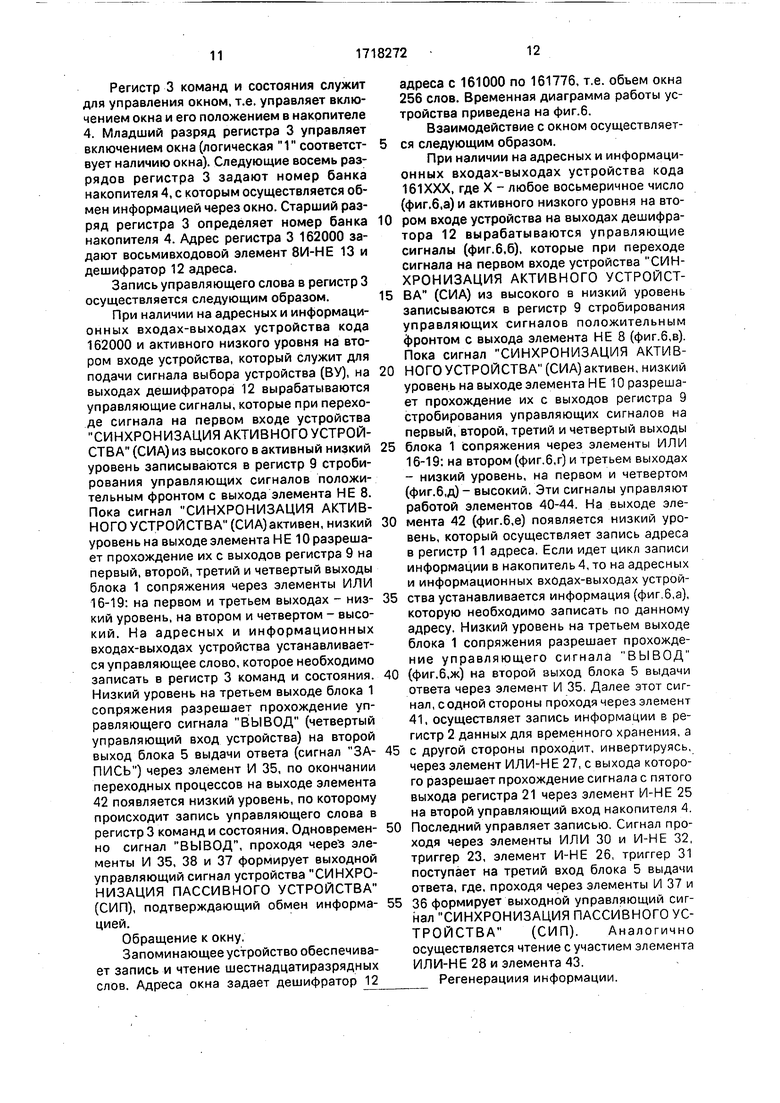

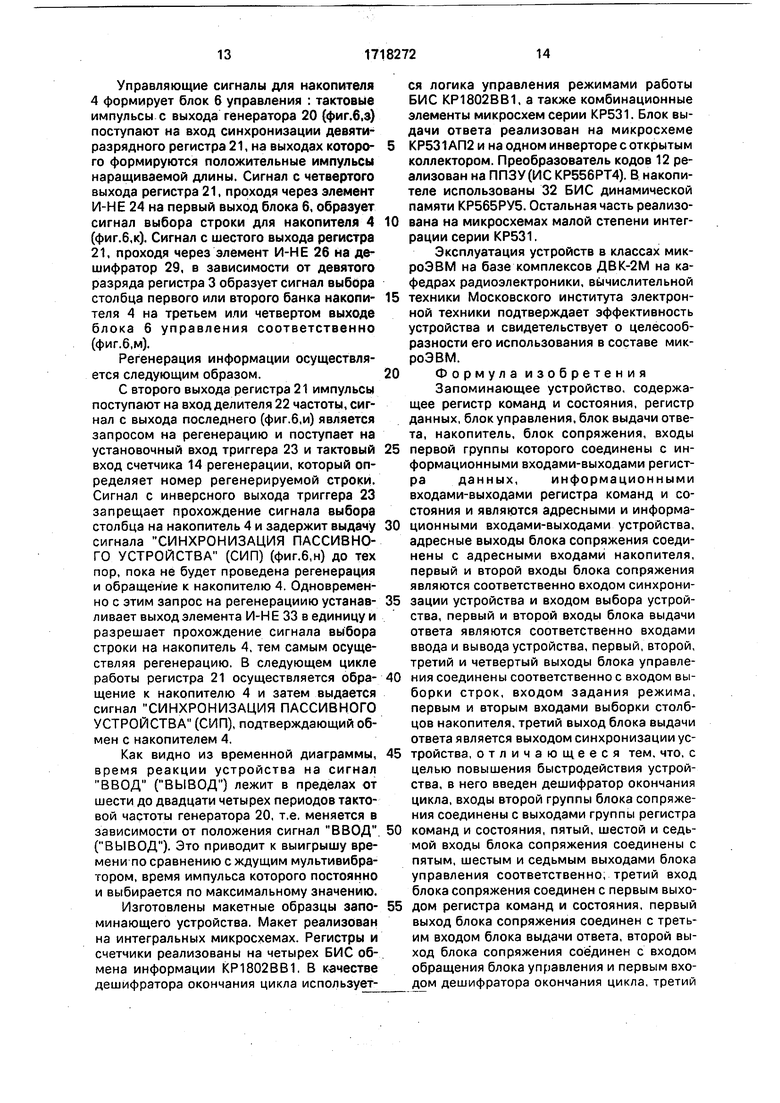

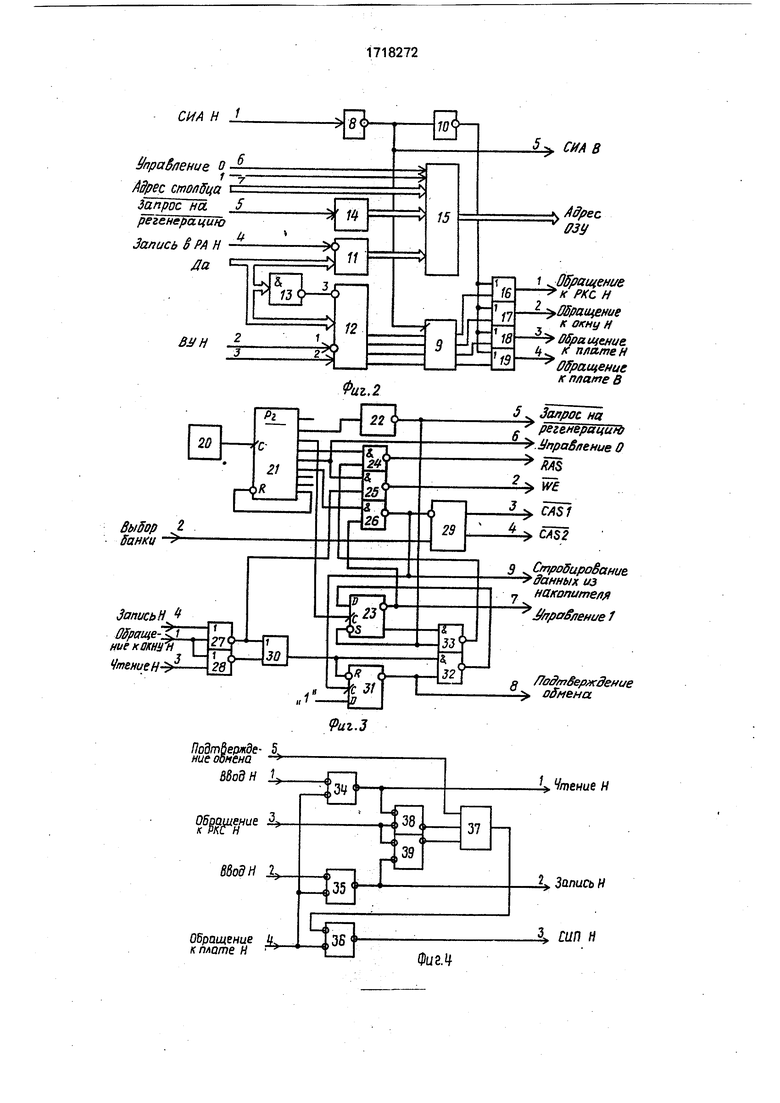

На фиг.1 дана структурная схема предлагаемого устройства; на фиг.2 - 5 функциональные схемы наиболее предпочтительных вариантов выполнения блока сопряжения, блока управления, блока выдачи ответа и дешифратора окончания цикла; на фиг. 6 - временная диаграмма работы устройства.

Запоминающее устройство (фиг.1) содержит блок 1 сопряжения, первая группа адресных входов которого соединена с информационными входами-выходами регистра 2 данных, информационными входами-выходами регистра 3 команд и состояния и являются адресными и информационными входами-выходами устройства. Вторая группа адресных входов блока 1 сопряжения связана с группой выходов регистра 3 команд и состояния. Адресные выходы блока 1 сопряжения соединены с адресными входами накопителя 4. Первый и второй входы блока 1 сопряжения являются соответственно входом синхронизации устройства и входом выбора устройства. Входы ввода и вывода устройства подсоединены с первым и вторым входами блока 5 выдачи ответа. Пятый, шестой и седьмой входы блока 1 сопряжения связаны с пятым, шестым и седьмым выходами блока 6 управления соответственно. Третий вход блока 1 сопряжения подключен к первому выходу регистра 3 команд и состояния. Первый выход блока 1 сопряжения соединен с третьим входом блока 5 выдачи ответа, а второй выход блока 1-е первым входом блока 6 управления и первым входом дешифратора 7 окончания цикла, который выполняет логическую функцию, заданную табл.1.

Третий выход блока 1 соединен с четвертым входом блока 5 выдачи ответа, четвертый выход блока 1 - с вторым входом дешифратора 7, пятый выход блока 1-е третьим входом дешифратора 7. Вторая группа входов-выходов регистра 2 данных соединена с информационными входами- выходами накопителя 4. Второй выход регистра 3 команд и состояния связан с входом задания режима блока 6 управления, вход

чтения последнего подключен к первому выходу блока 5 выдачи ответа и четвертому входу дешифратора 7 окончания цикла. Вход записи блока б соединен с вторым

выходом блока 5 и пятым входом дешифратора 7. Выходы с первого по четвертый блока 6 управления связаны соответственно с входом выборки строк, входом задания режима, первым и вторым входами выборки

0 столбцов накопителя 4. Восьмой выход блока 6 соединен с пятым входом блока 5, а девятый выход блока 6 - с вторым входом управления записью регистра 2 данных. Первый выход дешифратора 7 окончания

5 цикла подсоединен с входом управления записью регистра 3, третий выход дешифратора 7 с четвертым входом блока 1, второй выход дешифратора 7 - с первым входом управления записью регистра 2 данных, чет0 вертый выход дешифратора 7 - с входом задания режима регистра 2 данных, пятый выход дешифратора 7 - с входом задания режима регистра 3 команд и состояния. Третий выход блока 5 выдачи ответа является

5 выходом синхронизации устройства.

Блок 1 сопряжения (фиг,2) содержит элемент НЕ 8, вход которого является первым входом блока, а выход соединен с входом синхронизации регистра 9

0 стробирования управляющих сигналов, входом элемента НЕ 10 и является пятым выходом блока, регистр 11 адреса, входы которого соединены с первой группой входов дешифратора 12 адреса, входами эле5 мента 8И-НЕ 13 и являются адресными входами блока, счетчик 14, вход синхронизации которого является пятым входом блока, мультиплексор 15, первая группа входов которого подключена к выходам регистра 11

0 адреса, а вторая группа входов которого - к выходам счетчика 14, третья группа входов является второй группой адресных входов блока, а выходы являются адресными выходами блока, группу элементов ИЛИ 16-19,

5 первые входы которых подключены к выходу элемента НЕ 10, а вторые входы к соответствующим выходам регистра 9. адресные входы мультиплексора 15.являют- ся шестым и седьмым входами блока. Вто0 рой вход дешифратора 12 адреса является третьим управляющим входом блока, третий вход дешифратора 12 соединен с выходом элемента 8И-НЕ 13. Вход управления дешифратора 12 является вторым управля5 ющим входом блока. Дешифратор 12 адреса реализует логическую функцию, заданную табл,2.

Выходы элементов ИЛИ 16-19 являются первым, вторым, третьим и четвертым выходами блока соответственно.

Блок 6 управления (фиг.З) содержит генератор 20 тактовых импульсов, выход которого соединен с входом синхронизации сдвигового регистра 21, делитель 22 частоты, вход которого подключен к второму вы- ходу сдвигового регистра 21. Третий выход последнего подключен к входу синхронизации триггера 23, четвертый выход - к первому входу элемента И-НЕ 24, пятый выход - к первому входу элемента И-Н Е 25 и являет- ся шестым выходом блока, шестой выход - к первому входу элемента И-НЕ 26, девятый выход - к входу сброса сдвигового регистра 21. Первый, седьмой и восьмой выходы регистра 21 не задействованы. Входом обра- щения блока 6 является второй вход элемента ИЛ И-НЕ 27, который соединен С первым входом элемента ИЛ И-НЕ 28. Входом задания режима блока б является адресный вход дешифратора 29. Входами чтения и записи блока б являются соответственно второй вход элемента И Л И-НЕ 28 и первый вход элемента ИЛ И-НЕ 27. Выход последнего соединен с первым входом элемента ИЛИ 30 и вторым входом элемента И-НЕ 25. Выход элемента И Л И-НЕ 28 соединен с вторым входом элемента ИЛИ 30, выход которого связан с входом сброса триггера 31 и первым входом элемента И- НЕ 32. Выход элемента И-НЕ 26 соединен с входом управления дешифратора 29, входом синхронизации тоиггера 31 и является девятым выходом блока управления. На информационный вход триггера 31 подается сигнал логической 1. Инверсный выход триггера 31 связан с вторым входом элемента И-НЕ 32 и является восьмым выходом блока. Выход блока И-НЕ 32 подсоединен с информационным входом триггера 23. Установочный вход последнего подключен к вы- ходу делителя 22 частоты, второму входу элемента И-НЕ(33 и является пятым выходом блока. Прямой выход триггера 23 соединен с первым входом элемента И-НЕ 33, а инверсный выход триггера 23 - с вторым входом элемента И-НЕ 26 и является седьмым выходом блока. Выход элемента И-НЕ 33 соединен с вторым входом элемента И- НЕ 26. Выходы элементов И-НЕ 24 и 25, первый и второй выходы дешифратора явля- ются первым, вторым, третьим и четвертым выходами блока.

Блок 5 выдачи ответа (фиг.4) содержит шесть элементов И 34-39, первым входом блока является вход элемента И 34, выход которого соединен с первым входом элемента И 38 и является первым выходом блока. Вторым входом блока является первый вход элемента И 35, выход которого связан с вторым входом элемента И 39 и является

вторым выходом блока. Третьим входом блока является первый вход элемента И 39, который подключен к второму входу элемента И 38. Пятым входом блока является первый вход элемента И 37. Четвертым входом блока является второй вход элемента И 34, который соединен с вторыми входами элементов И 35 и 36. Третьим выходом блока является выход элемента И 36. Выходы элементов И 39 и 38 соединены с третьим и вторым входами элемента И 37 соответственно, выход которого подключен к первому входу элемента И 36.

Дешифратор 7 окончания цикла (фиг.5) содержит пять логических элементов 40-44, первый вход логического элемента 40 соединен с первыми входами логических элементов 41-44 и является первым входом дешифратора 7, второй вход логического элемента 40 - с вторыми входами логических элементов 41-44 и является вторым входом дешифратора 7, третий вход логического элемента 40 - с третьими входами логических элементов 41 и 42 и является третьим входом дешифратора 7, четвертый вход логического элемента 40 - с четвертыми входами логических элементов 41 и 42 и является пятым входом дешифратора 7 окончания цикла. Третий вход логического элемента 43 соединен с третьим входом логического элемента 44 и является четвертым входом дешифратора 7. Выходы логических элементов 40-44 являются выходами с первого по пятый дешифратора 7 окончания цикла соответственно. Логический элемент 40 реализует логическую функцию 1234, где 1-4 номера входов элемента 40 с первого по четвертый соответственно. Логический элемент 41 реализует логическую функцию 1234, где 1-4 номера входов элемента 41с первого по четвертый соответственно. Логический элемент 42 реализует логическую функцию 1234, где 1-4 номера входов элемента 42 с первого по четвертый соответственно. Логический элемент 43 реализует логическую функцию 1 2 3, где 1-3 номера входов элемента 43 с первого по третий соответственно. Логический элемент 44 реализует логическую функцию 1 2 3. где 1-3 номера входов элемента 44 с первого по третий соответственно.

Устройство имеет три режима работы: запись управляющего слова в регистр команд и состояния (РКС); обращение к окну (обмен информацией с накопителем); регенерация хранящейся в накопителе информации.

Рассмотрим подробнее работу устройства в каждом из режимов.

Запись управляющего слова в РКС.

Регистр 3 команд и состояния служит для управления окном, т.е. управляет включением окна и его положением в накопителе 4. Младший разряд регистра 3 управляет включением окна (логическая 1 соответствует наличию окна). Следующие восемь разрядов регистра 3 задают номер банка накопителя 4, с которым осуществляется обмен информацией через окно. Старший разряд регистра 3 определяет номер банка накопителя 4. Адрес регистра 3 162000 задают восьмивходовой элемент 8И-НЕ 13 и дешифратор 12 адреса.

Запись управляющего слова в регистр 3 осуществляется следующим образом.

При наличии на адресных и информаци- онных входах-выходах устройства кода 162000 и активного низкого уровня на втором входе устройства, который служит для подачи сигнала выбора устройства (ВУ), на выходах дешифратора 12 вырабатываются управляющие сигналы, которые при переходе сигнала на первом входе устройства СИНХРОНИЗАЦИЯ АКТИВНОГО УСТРОЙСТВА (СИА) из высокого в активный низкий уровень записываются в регистр 9 строби- рования управляющих сигналов положительным фронтом с выхода элемента НЕ 8. Пока сигнал СИНХРОНИЗАЦИЯ АКТИВНОГО УСТРОЙСТВА (СИА) активен, низкий уровень на выходе элемента НЕ 10 разрешает прохождение их с выходов регистра 9 на первый, второй, третий и четвертый выходы блока 1 сопряжения через элементы ИЛИ 16-19: на первом и третьем выходах - низкий уровень, на втором и четвертом - высокий. На адресных и информационных входах-выходах устройства устанавливается управляющее слово, которое необходимо записать в регистр 3 команд и состояния. Низкий уровень на третьем выходе блока 1 сопряжения разрешает прохождение управляющего сигнала ВЫВОД (четвертый управляющий вход устройства) на второй выход блока 5 выдачи ответа (сигнал ЗАПИСЬ) через элемент И 35, по окончании переходных процессов на выходе элемента 42 появляется низкий уровень, по которому происходит запись управляющего слова в регистр 3 команд и состояния. Одновременно сигнал ВЫВОД, проходя через элементы И 35, 38 и 37 формирует выходной управляющий сигнал устройства СИНХРОНИЗАЦИЯ ПАССИВНОГО УСТРОЙСТВА (СИП), подтверждающий обмен информацией.

Обращение к окну.

Запоминающее устройство обеспечивает запись и чтение шестнадцатиразрядных слов. Адреса окна задает дешифратор 12

адреса с 161000 по 161776, т.е. объем окна 256 слов. Временная диаграмма работы устройства приведена на фиг.6.

Взаимодействие с окном осуществляется следующим образом.

При наличии на адресных и информационных входах-выходах устройства кода 161XXX, где X - любое восьмеричное число (фиг.б.а) и активного низкого уровня на вто0 ром входе устройства на выходах дешифратора 12 вырабатываются управляющие сигналы (фиг.6,б), которые при переходе сигнала на первом входе устройства СИНХРОНИЗАЦИЯ АКТИВНОГО УСТРОЙСТ5 В А (СИА) из высокого в низкий уровень записываются в регистр 9 стробирования управляющих сигналов положительным фронтом с выхода элемента НЕ 8 (фиг.6,в). Пока сигнал СИНХРОНИЗАЦИЯ АКТИВ0 НОГО УСТРОЙСТВА (СИА)активен, низкий уровень на выходе элемента НЕЮ разрешает прохождение их с выходов регистра 9 стробирования управляющих сигналов на первый, второй, третий и четвертый выходы

5 блока 1 сопряжения через элементы ИЛИ 16-19: на втором (фиг.6,г) и третьем выходах - низкий уровень, на первом и четвертом (фиг.6,д) высокий. Эти сигналы управляют работой элементов 40-44. На выходе эле0 мента 42 (фиг.6,е) появляется низкий уровень, который осуществляет запись адреса в регистр 11 адреса. Если идет цикл записи информации в накопитель 4, то на адресных и информационных входах-выходах устрой5 ства устанавливается информация (фиг.6,а), которую необходимо записать по данному адресу. Низкий уровень на третьем выходе блока 1 сопряжения разрешает прохождение управляющего сигнала ВЫВОД

0 (фиг.б.ж) на второй выход блока 5 выдачи ответа через элемент И 35. Далее этот сигнал, содной стороны проходя через элемент 41, осуществляет запись информации в регистр 2 данных для временного хранения, а

5 с другой стороны проходит, инвертируясь, через элемент ИЛИ-НЕ 27, с выхода которого разрешает прохождение сигнала с пятого выхода регистра 21 через элемент И-НЕ 25 на второй управляющий вход накопителя 4.

0 Последний управляет записью. Сигнал проходя через элементы ИЛИ 30 и И-НЕ 32, триггер 23, элемент И-НЕ 26, триггер 31 поступает на третий вход блока 5 выдачи ответа, где, проходя через элементы И 37 и

5 36 формирует выходной управляющий сигнал СИНХРОНИЗАЦИЯ ПАССИВНОГО УСТРОЙСТВА (СИП). Аналогично осуществляется чтение с участием элемента ИЛИ-НЕ 28 и элемента 43.

Регенерациия информации.

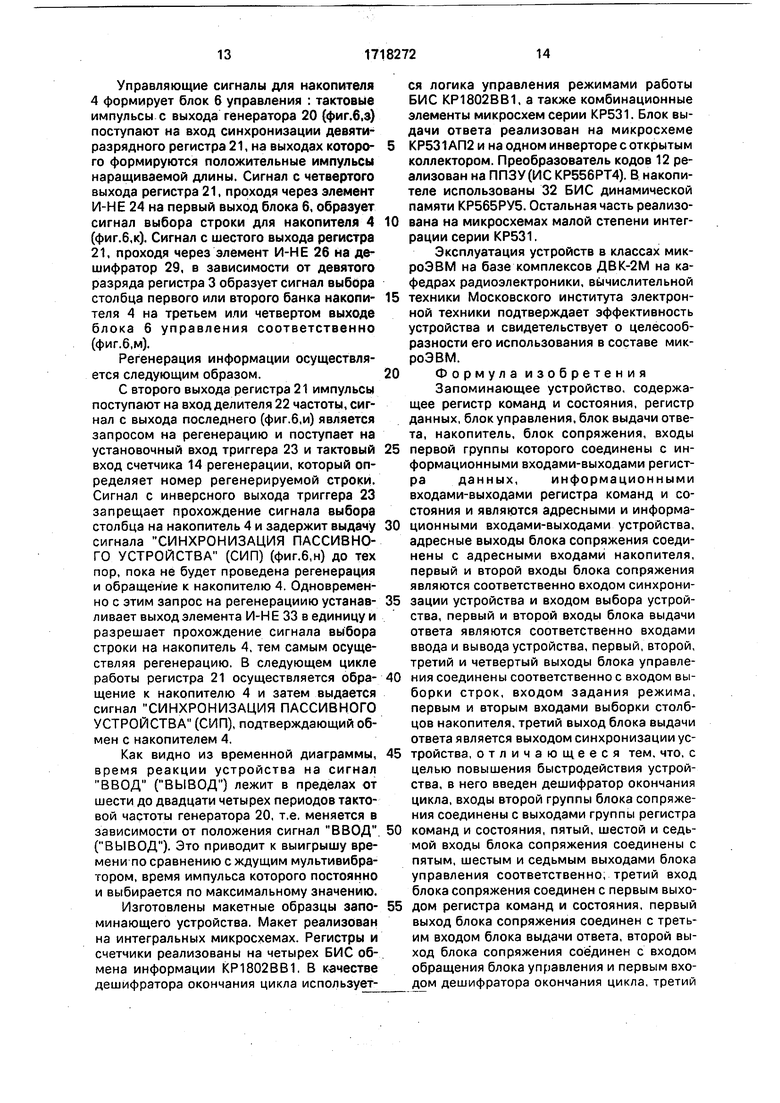

Управляющие сигналы для накопителя 4 формирует блок 6 управления : тактовые импульсы с выхода генератора 20 (фиг.б.з) поступают на вход синхронизации девятиразрядного регистра 21, на выходах которо- го формируются положительные импульсы наращиваемой длины. Сигнал с четвертого выхода регистра 21, проходя через элемент И-НЕ 24 на первый выход блока б, образует сигнал выбора строки для накопителя 4 (фиг.6,к). Сигнал с шестого выхода регистра 21, проходя через элемент И-НЕ 26 на дешифратор 29, в зависимости от девятого разряда регистра 3 образует сигнал выбора столбца первого или второго банка накопи- теля 4 на третьем или четвертом выходе блока 6 управления соответственно (фиг.б.м).

Регенерация информации осуществляется следующим образом.

С второго выхода регистра 21 импульсы поступают на вход делителя 22 частоты, сигнал с выхода последнего (фиг.6,и) является запросом на регенерацию и поступает на установочный вход триггера 23 и тактовый вход счетчика 14 регенерации, который определяет номер регенерируемой строки. Сигнал с инверсного выхода триггера 23 запрещает прохождение сигнала выбора столбца на накопитель 4 и задержит выдачу сигнала СИНХРОНИЗАЦИЯ ПАССИВНОГО УСТРОЙСТВА (СИП) (фиг.6,н) до тех пор, пока не будет проведена регенерация и обращение к накопителю 4. Одновременно с этим запрос на регенерациию устанав- ливает выход элемента И-НЕ 33 в единицу и разрешает прохождение сигнала выбора строки на накопитель 4, тем самым осуществляя регенерацию. В следующем цикле работы регистра 21 осуществляется обра- щение к накопителю 4 и затем выдается сигнал СИНХРОНИЗАЦИЯ ПАССИВНОГО УСТРОЙСТВА (СИП), подтверждающий обмен с накопителем 4,

Как видно из временной диаграммы, время реакции устройства на сигнал ВВОД (ВЫВОД) лежит в пределах от шести до двадцати четырех периодов тактовой частоты генератора 20, т.е. меняется в зависимости от положения сигнал ВВОД (ВЫВОД). Это приводит к выигрышу времени по сравнению с ждущим мультивибратором, время импульса которого постоянно и выбирается по максимальному значению.

Изготовлены макетные образцы запо- минающего устройства. Макет реализован на интегральных микросхемах. Регистры и счетчики реализованы на четырех БИС обмена информации КР1802ВВ1. В качестве дешифратора окончания цикла используется логика управления режимами работы БИС КР1802ВВ1, а также комбинационные элементы микросхем серии КР531. Блок выдачи ответа реализован на микросхеме КР531АП2 и на одном инверторе с открытым коллектором. Преобразователь кодов 12 реализован на ППЗУ (ИС КР556РТ4). В накопителе использованы 32 БИС динамической памяти КР565РУ5. Остальная часть реализована на микросхемах малой степени интеграции серии КР531.

Эксплуатация устройств в классах мик- роЭВМ на базе комплексов ДВК-2М на кафедрах радиоэлектроники, вычислительной техники Московского института электронной техники подтверждает эффективность устройства и свидетельствует о целесообразности его использования в составе мик- роЭВМ.

Формула изобретения Запоминающее устройство, содержащее регистр команд и состояния, регистр данных, блок управления, блок выдачи ответа, накопитель, блок сопряжения, входы первой группы которого соединены с информационными входами-выходами регистра данных, информационными входами-выходами регистра команд и состояния и являются адресными и информационными входами-выходами устройства, адресные выходы блока сопряжения соединены с адресными входами накопителя, первый и второй входы блока сопряжения являются соответственно входом синхронизации устройства и входом выбора устройства, первый и второй входы блока выдачи ответа являются соответственно входами ввода и вывода устройства, первый, второй, третий и четвертый выходы блока управления соединены соответственно с входом выборки строк, входом задания режима, первым и вторым входами выборки столбцов накопителя, третий выход блока выдачи ответа является выходом синхронизации устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введен дешифратор окончания цикла, входы второй группы блока сопряжения соединены с выходами группы регистра команд и состояния, пятый, шестой и седьмой входы блока сопряжения соединены с пятым, шестым и седьмым выходами блока управления соответственно, третий вход блока сопряжения соединен с первым выходом регистра команд и состояния, первый выход блока сопряжения соединен с третьим входом блока выдачи ответа, второй выход блока сопряжения соединен с входом обращения блока управления и первым входом дешифратора окончания цикла, третий

выход блока сопряжения соединен с четвертым входом блока выдачи ответа, четвертый и пятый выходы блока сопряжения соединены с вторым и третьим входами дешифратора окончания цикла соответственно, входы-выходы второй группы регистра данных соединены с информационными входами-выходами накопителя, второй выход регистра команд и состояния соединен с входом задания режима блока управления, входы чтения и записи блока управления соединены соответственно с первым и вторым выходами блока выдачи ответа и четвертым и пятым входами дешифратора окончания цикла, восьмой выход блока управления соединен с пятым входом блока

Примечание. ХХХХХ-любой набор,

отличающийся от предыдущих.

Примечание. ХХХХ XXX - любой набор, отличающийся от предыдущих.

выдачи ответа, девятый выход блока управления соединен с вторым входом управления записью регистра данных, первый выход дешифратора окончания цикла соединен с входом управления записью регистра команд и состояния, третий выход дешифратора окончания цикла соединен с четвертым входом блока сопряжения, второй выход дешифратора окончания цикла

соединен с первым входом управления записью регистра данных, четвертый выход дешифратора окончания цикла соединен с входом задания режима регистра данных, пятый выход дешифратора окончания цикла

соединен с входом задания режима регистра команд и состояния.

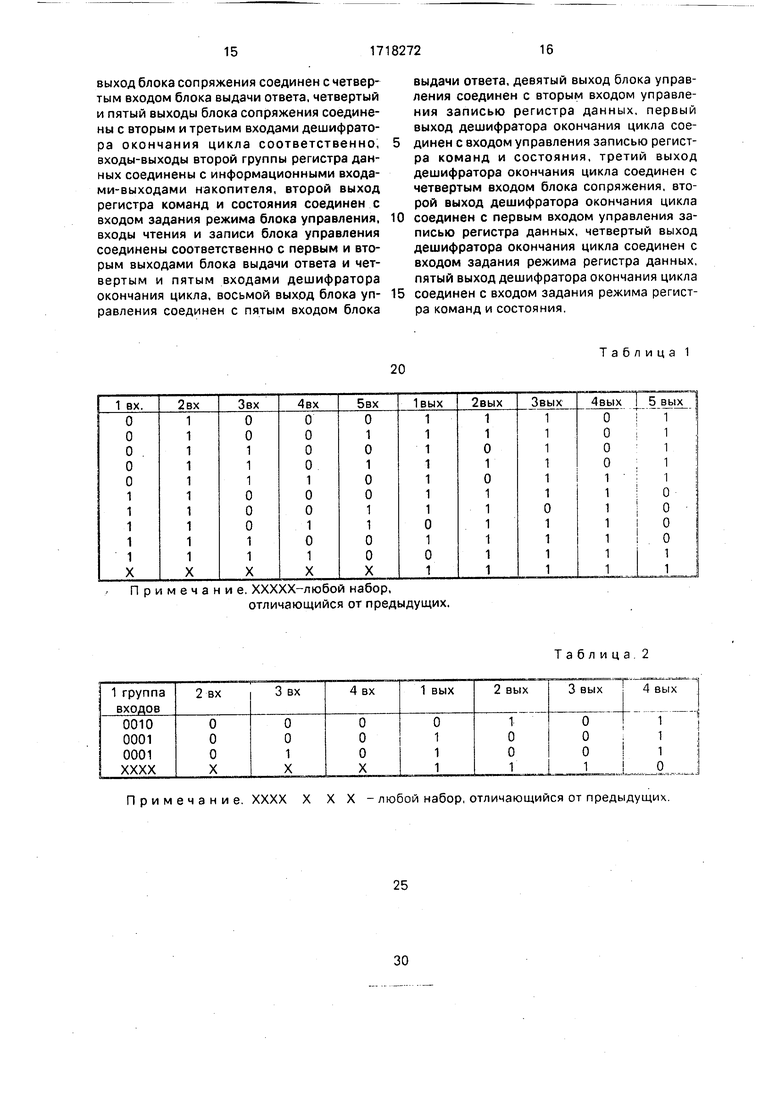

Таблица 1

Таблица. 2

4 вых

Т 1 1 О

ЗаписьН %

0fyawe- bL- - ние комм

Чтением-.

Риг.З

flodm,

ycfjmuc ci

Чмена я jL

г

а

к РКСГН

ВводН 1

Обращение к плате Н

с

5

Адрес ОЗУ

PKC Н

- щение. 4 к плате Н

о Лодтёерждение обмена

Н

Н

Л Д/л «

Фиг.

ДА а

СИ АН S

1ГХ Адрес

СПАВ в

Обращение

к окну ну

Обращениея

к плате В°Запись 8Р

РА Н-

Вы Sod Hж

ТИ

Запрос на - регенераций Ч

Ш WE л

CAS

сипн н

5ТЛЛЛЛЛЛЛЯПЛ|1ЛЛШП1ШЛ1ШШиШШ1Л

. IJ1 I

накс

данные

torn St.

etna

tttUH ST

24 т

Pui.Q

| Ножевой прибор к валичной кардочесальной машине | 1923 |

|

SU256A1 |

| /Микропроцессорные средства и системы, 1986, № 2, с.62 | |||

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-03-07—Публикация

1989-07-20—Подача