0W /

Изобретение относится к контрольно-измерительной технике и может быть использовано в аппаратуре контроля параметров интегральных схем.

Целью изобретения является повышение точности формирования импульсов выходных воздействий за счет автоматической коррекции уровней формируемых импульсов в зависимости от их скважности.

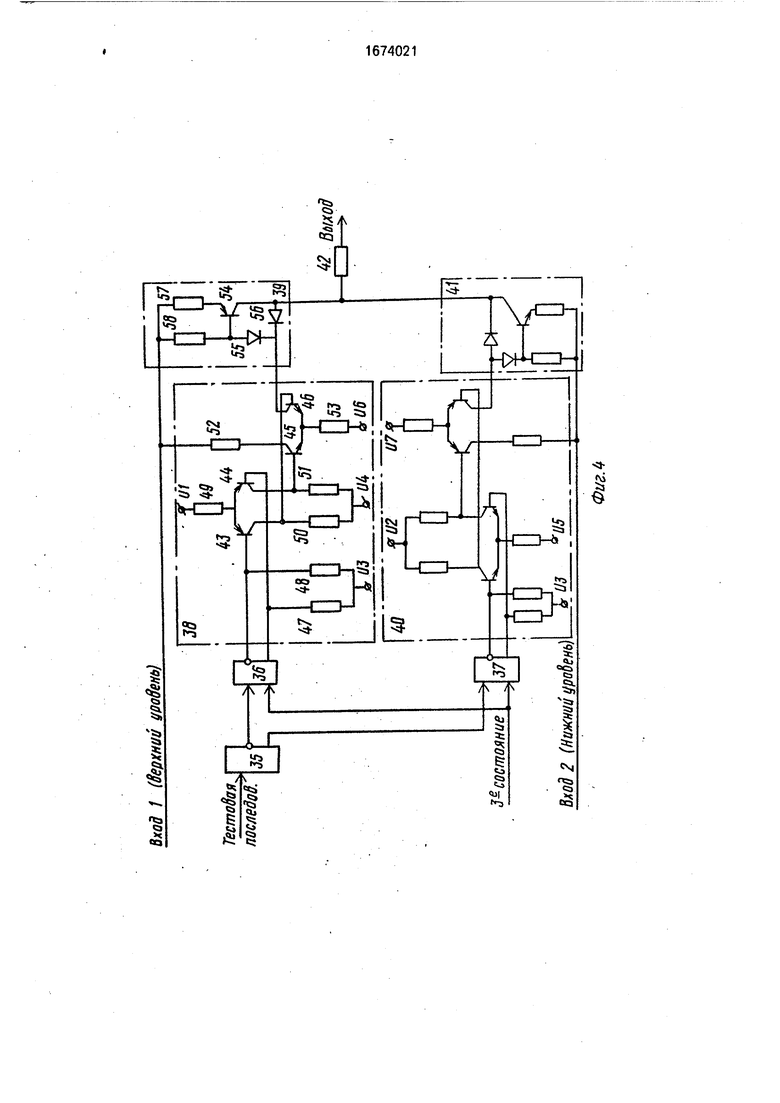

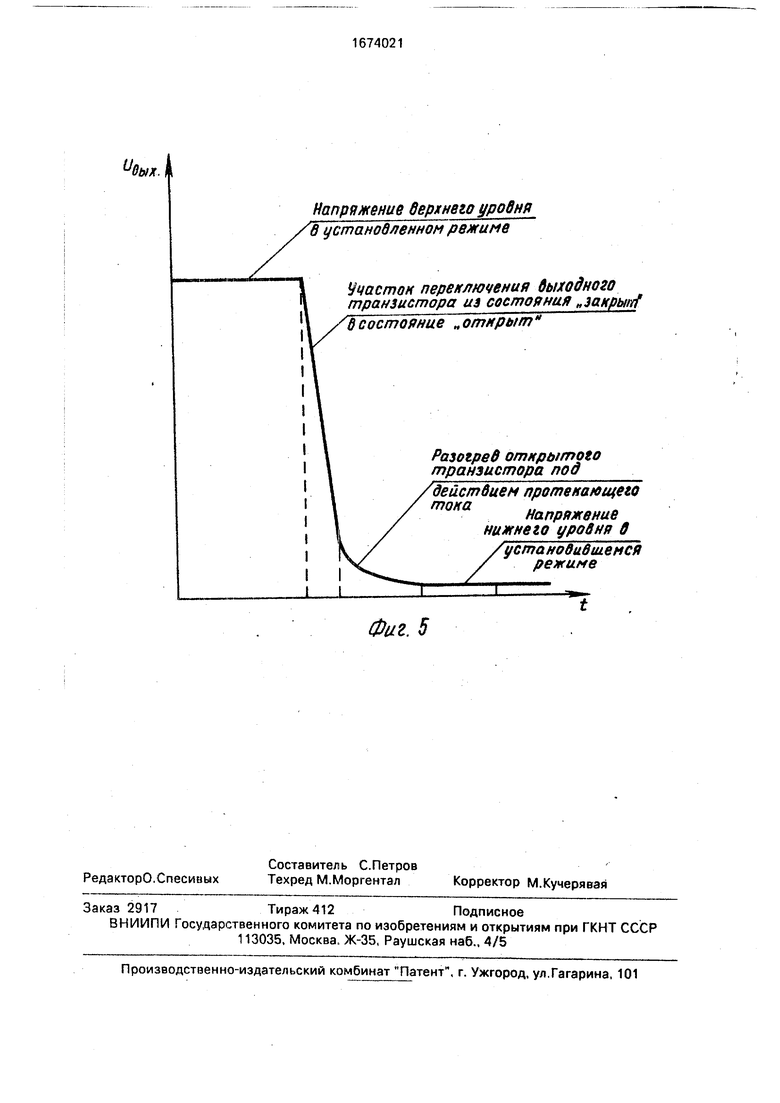

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема буферного усилителя; на фиг.З - схема компенсации; на фиг.4 - схема формирования импульсов; на фиг.5 - вид выходного сигнала формирователя импульсов.

Выходное устройство тестера для контроля интегральных схем содержит буферный усилитель 1, первый и второй входы которого являются соответственно входами Драйвер 1 и Драйвер 2 устройства, первый блок 2 компенсации, соединенный первым входом через инвертор 3 с входом тестовой последовательности устройства, вторым входом с входом Компенсация устройства, третьим входом с входом Установка т 1, выход блок 2 соединен с третьим входом буферного усилителя 1, второй блок 4 компенсации, соединенный первым входом с входом тестовой последовательности устройства, вторым входом с входом Установка т 2 устройства, а выходом с четвертым входом буферного усилителя 1, формирователь 5 импульсов, соединенный первым и вторым входами соответственно с первым и вторым выходами буферного усилителя 1, третьим входом с входом тестовой последовательности устройства и четвертым входом с входом 3-е состояние устройства, а выходом через ключ 6 с выходом устройства, через второй ключ 7 с входом Силовая линия устройства, а через третий ключ 8 с входом Обратная связь устройства, делитель 9, соединенный входом с выходом узла, первый и второй компараторы 10 и 11, соединенные первыми входами с выходом делителя 9, вторыми входами с входом Строб устройства, формирователь 12 уровней, первый и второй входы которого являются входами соответственно Уровень 1 и Уровень 2 устройства, первым выходом соединенный с третьтим входом первого компаратора 10, выход которого является выходом Компаратор Г устройства, вторым выходом с третьим входом второго компаратора 11, выход которого является выходом Компаратор 2 устройства.

Буферный усилитель 1 преобразует сигналы, поступающие по входам Драйвер 1

и Драйвер 2 в выходные сигналы Выход 1 и Выход 2, которые поступают на соответствующие входы формирователя 4 импульсов.

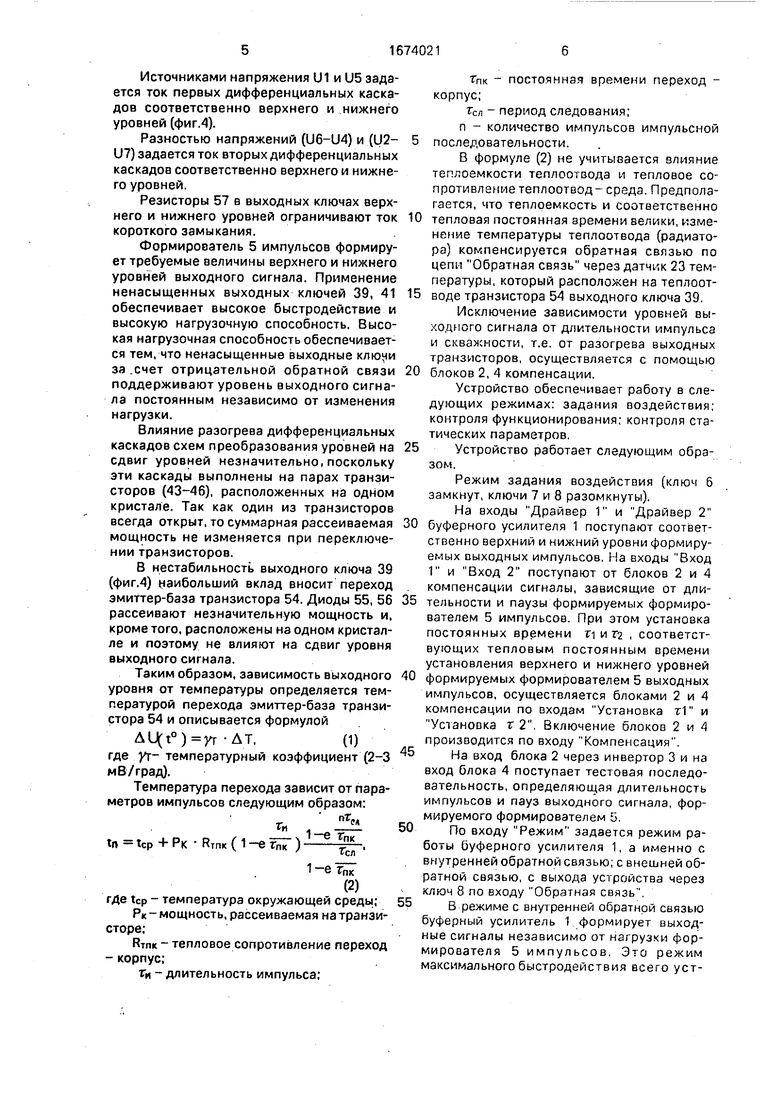

Буферный усилитель 1 состоит из двух

идентичных схем 13 и 14 усиления.

Каждая схема усиления содержит усилитель 15 с резистором 16 обратной связи, сумматор, выполненный на резисторах 1720, корректирующие резисторы 21 и 22, с помощью которых осуществляется коррекция нуля соответственно в режиме с внутренней и внешней обратной связью, датчик 23 температуры, выполненный на полупроводниковом диоде, источник 24 тока, управляемые ключи 25-27 и инвертор 28.

В зависимости от состояния сигнала по входу Режим схема усиления может находиться в состоянии с внутренней обратной

связью, ключ 25 замкнут, ключи 26, 27 разомкнуты; в состоянии с внешней обратной связью, ключ 25 разомкнут, ключи 26, 27 замкнуты.

На выходе Выход Г буферного усилителя 1 устанавливается верхний уровень выходного сигнала, на выходе Выход 2 - нижний уровень.

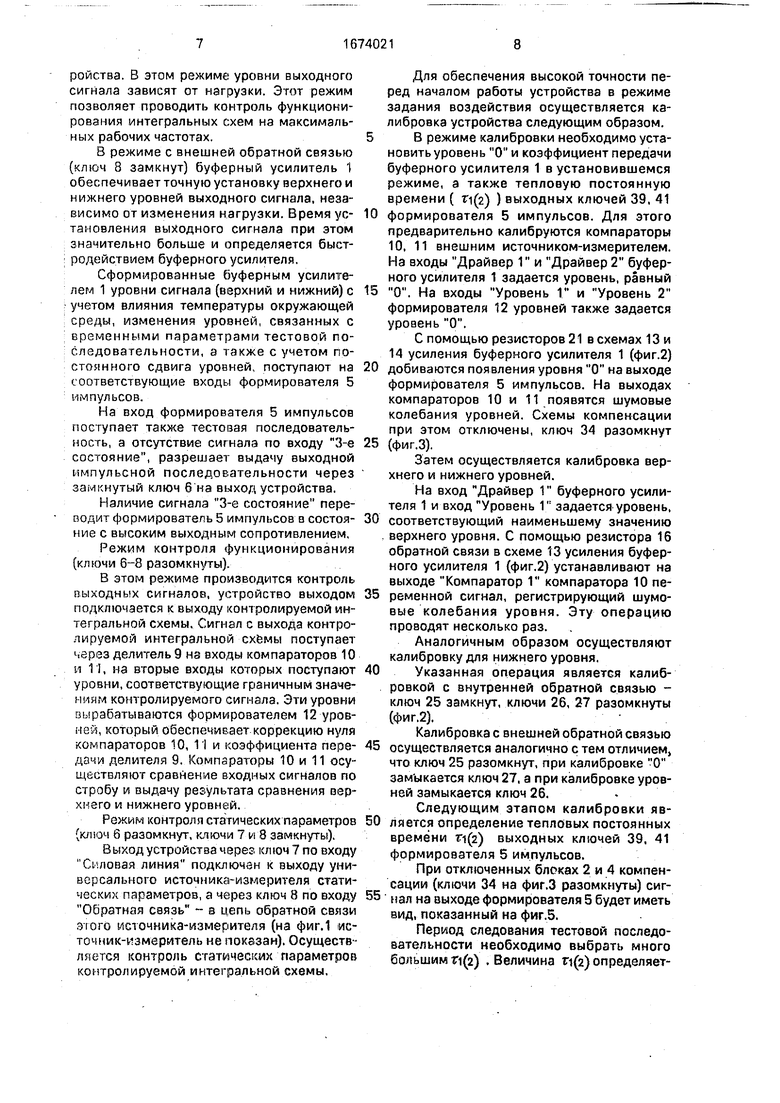

Схема компенсации (фиг.З) содержит интегрирующую цепь с регулируемой постоянной времени, выполненную на резисторе 29 и варикапе 30, масштабирующий усилитель 31 с регулируемым с помощью резисторов 32, 33 коэффициентом усиления, управляемый ключ 34.

Схема компенсации вырабатывает сигнал, компенсирующий сдвиг уровня формирователя 5 импульсов, зависящий от длительности и паузы входной тестовой последовательности. Постоянная времени интегрирующей цепи на элементах 29 и 30 является регулируемой и устанавливается равной тепловой постоянной,времени выходных транзисторов формирователя 5 импульсов.

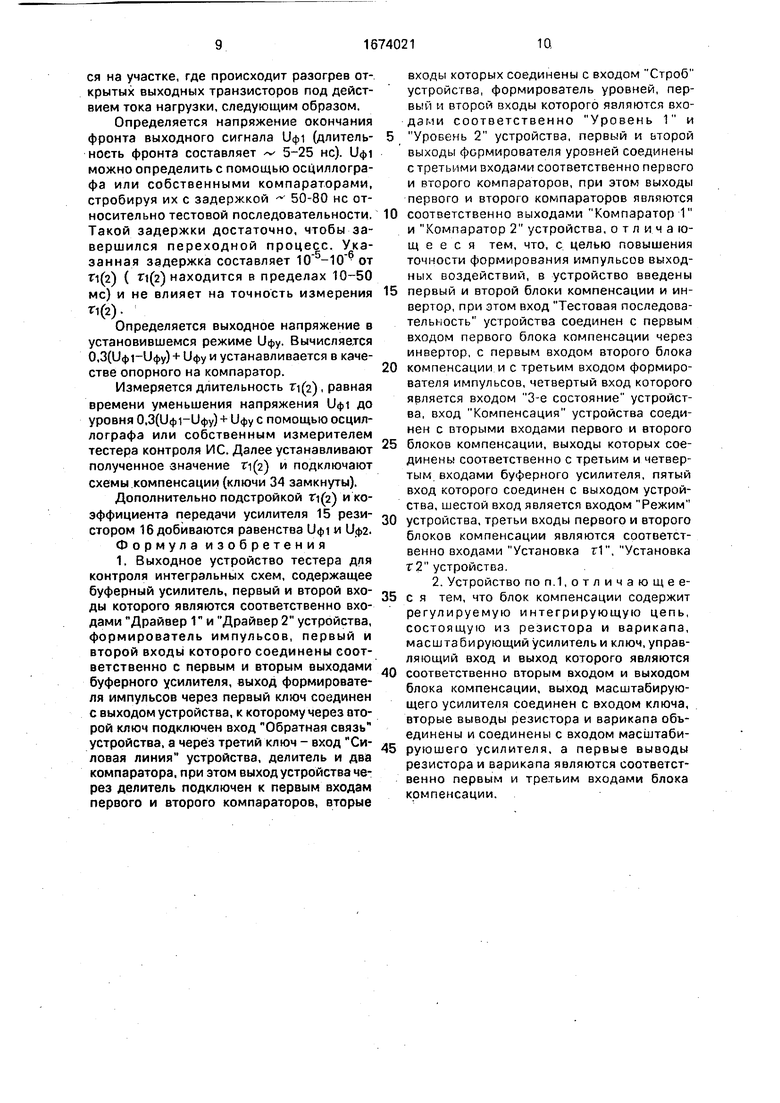

Формирователь импульсов содержит (фиг.4) логические схемы 35-37, выполненные на быстродействующих ЭСЛ ключах, схему 38 преобразования верхнего уровня, ключ 39, схему 40 преобразования нижнего

0 уровня, ключ 41, и согласующий резистор 42.

Схема преобразования уровня включает первый дифференциальный каскад на транзисторах 43, 44. второй дифференци5 альный каскад на транзисторах 45,46 и резисторы 47-53.

Выходной ключ представляет собой ненасыщенный ключ на транзисторе 54, диодах 55, 56 и резисторах 57, 58.

Источниками напряжения U1 и U5 задается ток первых дифференциальных каскадов соответственно верхнего и нижнего уровней (фиг.4).

Разностью напряжений (U6-U4) и (U2- U7) задается ток вторых дифференциальных каскадов соответственно верхнего и нижнего уровней.

Резисторы 57 в выходных ключах верхнего и нижнего уровней ограничивают ток короткого замыкания.

Формирователь 5 импульсов формирует требуемые величины верхнего и нижнего уровней выходного сигнала. Применение ненасыщенных выходных ключей 39. 41 обеспечивает высокое быстродействие и высокую нагрузочную способность. Высокая нагрузочная способность обеспечивается тем, что ненасыщенные выходные ключи за счет отрицательной обратной связи поддерживают уровень выходного сигнала постоянным независимо от изменения нагрузки.

Влияние разогрева дифференциальных каскадов схем преобразования уровней на сдвиг уровней незначительно,поскольку эти каскады выполнены на парах транзисторов (43-46). расположенных на одном кристале. Так как один из транзисторов всегда открыт, то суммарная рассеиваемая мощность не изменяется при переключении транзисторов.

В нестабильность выходного ключа 39 (фиг.4) наибольший вклад вносит переход эмиттер-база транзистора 54. Диоды 55, 56 рассеивают незначительную мощность и. кроме того, расположены на одном кристалле и поэтому не влияют на сдвиг уровня выходного сигнала.

Таким образом, зависимость выходною уровня от температуры определяется температурой перехода эмиттер-база транзистора 54 и описывается формулой

ДЦт°)хг -AT,(1)

где /г- температурный коэффициент (2-3 мВ/град).

Температура перехода зависит от параметров импульсов следующим образом:

ги

пТ,

с

tn tcp + Рк RTHK ( 1 -€ Гпк )

1-е гпк

Гсл

1-е тшГ (2) гДе tcp - температура окружающей среды;

Рк-мощность, рассеиваемая на транзисторе;

Ятпк - тепловое сопротивление переход - корпус;

ти - длительность импульса:

Тпк - постоянная времени переход - корпус;

тсл - период следования; п - количество импульсов импульсной 5 последовательности.

В формуле (2) не учитывается влияние теплоемкости теплеют вода и тепловое сопротивление теплоотвод- среда. Предполагается, что теплоемкость и соответственно

10 тепловая постоянная времени велики, изменение температуры теплоотвода (радиатора) компенсируется обратная связью по цепи Обратная связь через датчик 23 температуры, который расположен на теплоот15 воде транзистора 54 выходного ключа 39.

Исключение зависимости уровней выходного сигнала от длительности импульса и скважности, т.е. от разогрева выходных транзисторов, осуществляется с помощью

20 блоков 2, 4 компенсации.

Устройство обеспечивает работу в следующих режимах; задания воздействия; контроля функционирования; контроля статических параметров.

25Устройство работает следующим образом.

Режим задания воздействия (ключ 6 замкнут, ключи 7 и 8 разомкнуты).

На входы Драйвер 1 и Драйвер 2

30 буферного усилителя 1 поступают соответственно верхний и нижний уровни формируемых выходных импульсов. На входы Вход 1 и Вход 2 поступают от блоков 2 и 4 компенсации сигналы, зависящие от дли35 тельности и паузы формируемых формирователем 5 импульсов. При этом установка постоянных времени л и Г2 . соответствующих тепловым постоянным времени установления верхнего и нижнего уровней

40 формируемых формирователем 5 выходных импульсов, осуществляется блоками 2 и 4 компенсации по входам Установка г1 и Установка г 2. Включение блоков 2 и 4 производится по входу Компенсация .

45На вход блока 2 через инвертор 3 и на

вход блока 4 поступает тестовая последовательность, определяющая длительность импульсов и пауз выходного сигнала, формируемого формирователем Ъ.

50По входу Режим1 задается режим работы буферного усилителя 1, а именно с внутренней обратной связью; с внешней обратной связью, с выхода устроиства через ключ 8 по входу Обратная СЕЫЗЬ.

55в режиме с внутренней обратной связью

буферный усилитель 1 формирует выходные сигналы независимо от нагрузки формирователя 5 импульсов. Это режим максимального быстродействия всего устройства. В этом режиме уровни выходного сигнала зависят от нагрузки. Этот режим позволяет проводить контроль функционирования интегральных схем на максимальных рабочих частотах.

В режиме с внешней обратной связью (ключ 8 замкнут) буферный усилитель 1 обеспечивает точную установку верхнего и нижнего уровней выходного сигнала, независимо от изменения нагрузки. Время установления выходного сигнала при этом значительно больше и определяется быстродействием буферного усилителя.

Сформированные буферным усилителем 1 уровни сигнала (верхний и нижний) с учетом влияния температуры окружающей среды, изменения уровней, связанных с временными параметрами тестовой последовательности, а также с учетом постоянного сдвига уровней, поступают на соответствующие входы формирователя 5 импульсов.

На вход формирователя 5 импульсов поступает также тестовая последовательность, а отсутствие сигнала по входу 3-е состояние, разрешает выдачу выходной импульсной последовательности через замкнутый ключ 6 на выход устройства.

Наличие сигнала 3-е состояние переводит формирователь 5 импульсов в состояние с высоким выходным сопротивлением. Режим контроля функционирования (ключи 6-8 разомкнуты).

В этом режиме производится контроль выходных сигналов, устройство выходом подключается к выходу контролируемой интегральной схемы. Сигнал с выхода контролируемой интегральной схемы поступает через делитель 9 на входы компараторов 10 и 11, на вторые входы которых поступают уровни, соответствующие граничным значениям контролируемого сигнала. Эти уровни вырабатываются формирователем 12 уровней, который обеспечивает коррекцию нуля компараторов 10, 11 и коэффициента передачи делителя 9. Компараторы 10 и 11 осуществляют сравнение входных сигналов по стробу и выдачу результата сравнения верхнего и нижнего уровней.

Режим контроля статических параметров (ключ б разомкнут, ключи 7 и 8 замкнуты).

Выход устройства через ключ 7 по входу Силовая линия подключен к выходу универсального источника-измерителя статических параметров, а через ключ 8 по входу Обратная связь - в цепь обратной связи эчого источника-измерителя (на фиг.1 источник-измеритель не показан). Осуществляется контроль статических параметров контролируемой интегральной схемы.

Для обеспечения высокой точности перед началом работы устройства в режиме задания воздействия осуществляется калибровка устройства следующим образом.

В режиме калибровки необходимо установить уровень О и коэффициент передачи буферного усилителя 1 в установившемся режиме, а также тепловую постоянную времени ( г 1(2) ) выходных ключей 39, 41

формирователя 5 импульсов. Для этого предварительно калибруются компараторы 10, 11 внешним источником-измерителем. На входы Драйвер Г и Драйвер 2 буферного усилителя 1 задается уровень, равный

О. На входы Уровень 1 и Уровень 2 формирователя 12 уровней также задается уровень О.

С помощью резисторов 21 в схемах 13 и 14 усиления буферного усилителя 1 (фиг.2)

добиваются появления уровня О на выходе формирователя 5 импульсов. На выходах компараторов 10 и 11 появятся шумовые колебания уровней. Схемы компенсации при этом отключены, ключ 34 разомкнут

(фиг.З).

Затем осуществляется калибровка верхнего и нижнего уровней.

На вход Драйвер 1 буферного усилителя 1 и вход Уровень 1 задается уровень.

соответствующий наименьшему значению верхнего уровня. С помощью резистора 16 обратной связи в схеме 13 усиления буферного усилителя 1 (фиг.2) устанавливают на выходе Компаратор 1 компаратора 10 переменной сигнал, регистрирующий шумовые колебания уровня. Эту операцию проводят несколько раз.

Аналогичным образом осуществляют калибровку для нижнего уровня.

Указанная операция является калибровкой с внутренней обратной связью - ключ 25 замкнут, ключи 26, 27 разомкнуты (фиг.2).

Калибровка с внешней обратной связью

5 осуществляется аналогично с тем отличием, что ключ 25 разомкнут, при калибровке О зам ыкается ключ 27, а при калибровке уровней замыкается ключ 26.

Следующим этапом калибровки яв0 лается определение тепловых постоянных времени п(2) выходных ключей 39, 41 формирователя 5 импульсов.

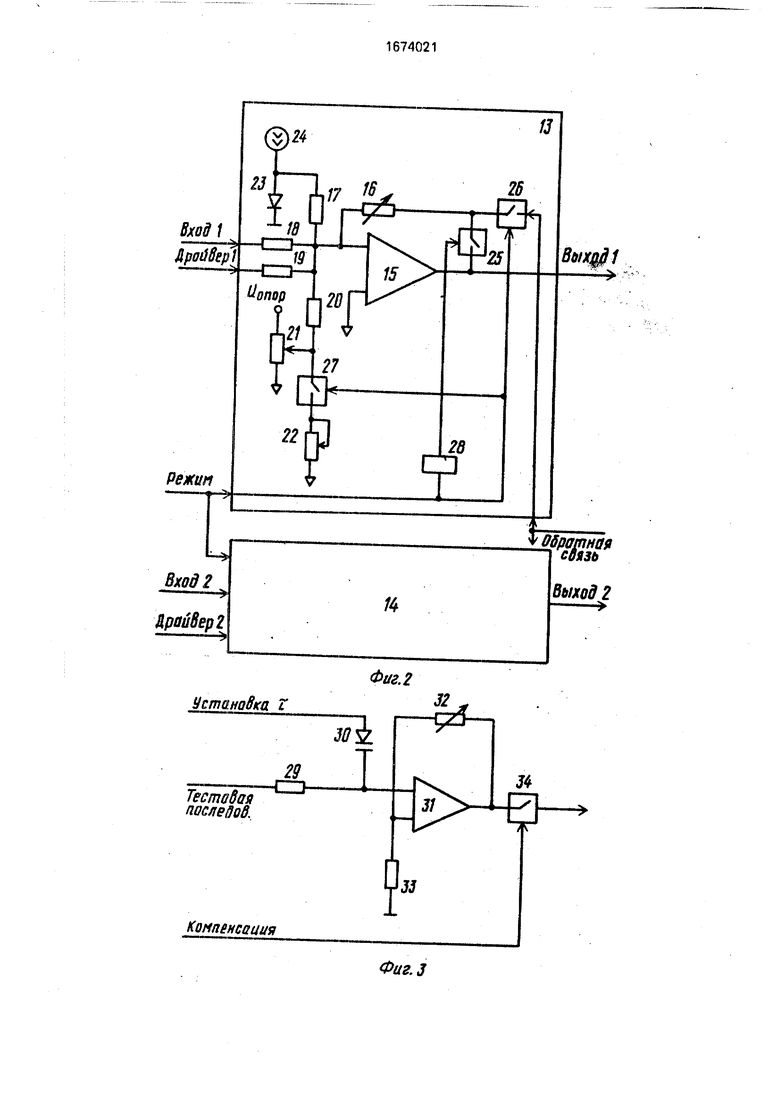

При отключенных блоках 2 и 4 компенсации (ключи 34 на фиг.З разомкнуты) сиг5 нал на выходе формирователя 5 будет иметь вид, показанный на фиг.5.

Период следования тестовой последовательности необходимо выбрать много большим п(а) . Величина п(2) определяется на участке, где происходит разогрев открытых выходных транзисторов под действием тока нагрузки, следующим образом.

Определяется напряжение окончаний фронта выходного сигнала иф1 (длитель- ность фронта составляет 5-25 не). 11ф1 можно определить с помощью осциллографа или собственными компараторами, стробируя их с задержкой 50-80 не относительно тестовой последовательности. Такой задержки достаточно, чтобы завершился переходной процесс. Указанная задержка составляет от 71(2) ( 1(2) находится в пределах 10-50 мс) и не влияет на точность измерения

Г,(2) Определяется выходное напряжение в установившемся режиме Уфу. Вычисляется 0,3(иф1-1)фу) + ифу и устанавливается о качестве опорного на компаратор.

Измеряется длительность Ti(2), равная времени уменьшения напряжения 1)ф1 до уровня 0,3() + ифу с помощью осциллографа или собственным измерителем тестера контроля ИС. Далее устанавливают полученное значение п(2) и подключают схемы компенсации (ключи 34 замкнуты).

Дополнительно подстройкой ri(2) и коэффициента передачи усилителя 15 рези- стором 16 добиваются равенства 11ф1 и иф2.

Формула изобретения

1. Выходное устройство тестера для контроля интегральных схем, содержащее буферный усилитель, первый и второй вхо- ды которого являются соответственно входами Драйвер 1 и Драйвер 2 устройства, формирователь импульсов, первый и второй входы которого соединены соответственно с первым и вторым выходами буферного усилителя, выход формирователя импульсов через первый ключ соединен с выходом устройства, к которому через второй ключ подключен вход Обратная связь устройства, а через третий ключ - вход Си- ловая линия устройства, делитель и два компаратора, при этом выход устройства через делитель подключен к первым входам первого и второго компараторов, вторые

входы которых соединены с входом Строб устройства, формирователь уровней, первый и второй входы которого явлпютсч входами соответственно Уровень 1 и Уровень 2 устройства, первый и ьторой выходы формирователя уровней соединены с третьими входами соответственно первого и второго компараторов, при этом выходы первого и второго компараторов яиляются соответственно выходами Компаратор 1 и Компаратор 2 устройства, отличающееся тем, что, с целью повышения точности формирования импульсов выходных воздействий, в устройство введены первый и второй блоки компенсации и инвертор, при отом вход Тестовая последовательность устройства соединен с первым входом первого блока компенсации через инвертор, с первым входом второго блока компенсации и с третьим входом формирователя импульсов, четвертый вход которого является входом 3-е состояние устройства, вход Компенсация устройства соединен с вторыми входами первого и второго блоков компенсации, выходы которых соединены соответственно с третьим и четвертым входами буферного усилителя, пятый вход которого соединен с выходом устройства, шестой вход лвляетсл входом Режим устройства, третьи входы первого и второго блоков компенсации являются соответственно входами Установка г1, Установка г 2 устройства.

2. Устройство поп.1,отличающее- с я тем, что блок компенсации содержит регулируемую интегрирующую цепь, состоящую из резистора и варикапа, масштабирующий усилитель и ключ, управляющий вход и выход которого являются соответственно вторым входом и выходом блока компенсации, выход масштабирующего усилителя соединен с входом ключа, вторые выводы резистора и варикапа объединены и соединены с входом масштабирующего усилителя, а первые выводы резистора и варикапа являются соответственно первым и третьим входами блока компенсации.

пая

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЛОГАБАРИТНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР, УСТОЙЧИВЫЙ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИМ ИЗЛУЧЕНИЕМ | 2013 |

|

RU2557479C2 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для сопряжения абонентских станций с линией связи локальной сети | 1986 |

|

SU1437872A1 |

| Устройство для контроля цифровых схем | 1986 |

|

SU1522130A1 |

| Формирователь прямоугольных импульсов | 1989 |

|

SU1674356A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| Устройство для автоматического контроля интегральных схем | 1986 |

|

SU1401418A2 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| Трехфазный выпрямитель напряжения с корректором коэффициента мощности | 2023 |

|

RU2813799C1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано в аппаратуре контроля параметров интегральных схем. Цель изобретения - повышение точности формирования импульсов выходных воздействий за счет автоматической коррекции формируемых импульсов в зависимости от их скважности. Устройство содержит буферный усилитель 1, формирователь 5 импульсов, ключи 6 - 8, делитель 9, компараторы 10, 11, формирователь 12 уровней. Введение схем 2 и 4 компенсации, инвертора 3 и образование новых функциональных связей обеспечивает возможность автоматической коррекции формируемых импульсов. В описании приведены примеры реализации буферного усилителя 1, схем 2 и 4 компенсации, формирователя 5 импульсов. 1 з.п. ф-лы, 5 ил.

Установка Г

Ьиг,2

32

Фиг.З

Вход 1 (Верхний уровень)

Вход 2 (Нижний уро&ень)

W Выход

ILJJ

Фиг Л

Напряжение верхнего уровня в установленном режиме

Участок переключения быходного транзистора из состояния „закрыт

6состояние „открыт

Разогрев открытого транзистора под

действием протекающею

токанапряжение

нижнего уровня в

уста но вив ш. емся режиме

Т

Фиг. 5

| Выходной узел тестера для контроля логических схем | 1982 |

|

SU1018064A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Грачев О.Г | |||

| и др | |||

| Система Элекон-СФ для контроля электрических параметров БИС ЗУ и микропроцессоров | |||

| - Электронная промышленность, 1980, № 6, с.21-31. | |||

Авторы

Даты

1991-08-30—Публикация

1989-01-30—Подача