Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах и в системах числового программного управления.

Цель изобретения - упрощение конструкции за счет уменьшения аппаратурных затрат интерполятора.

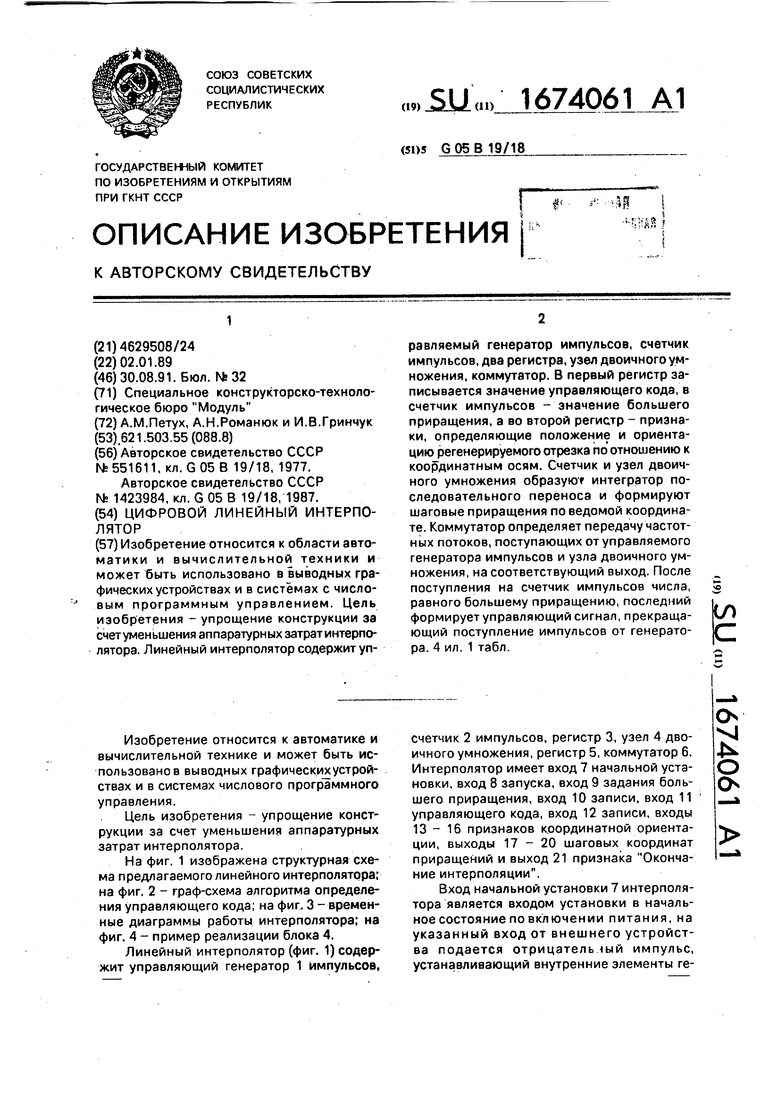

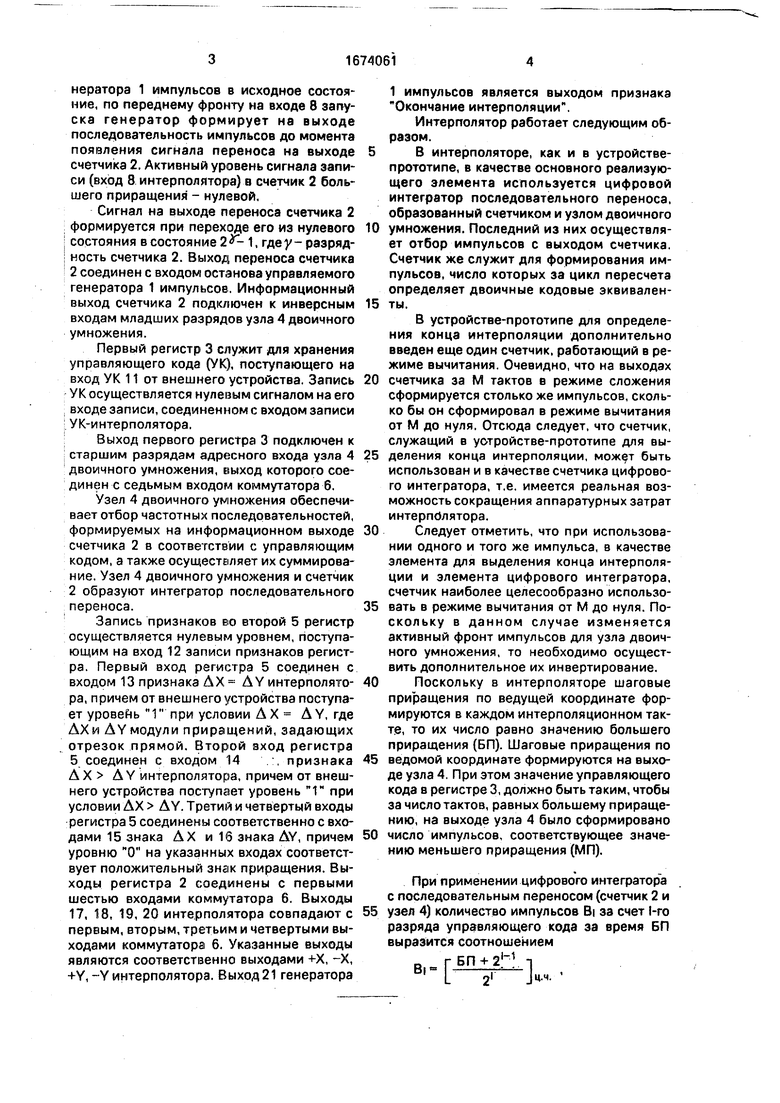

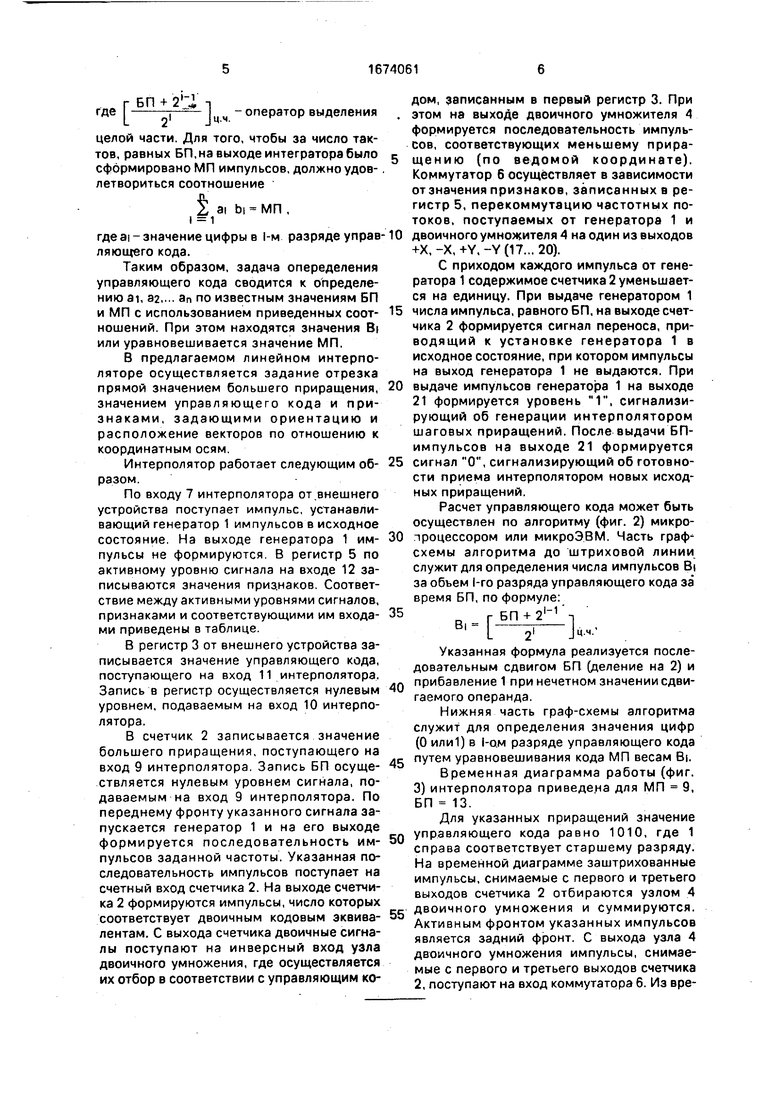

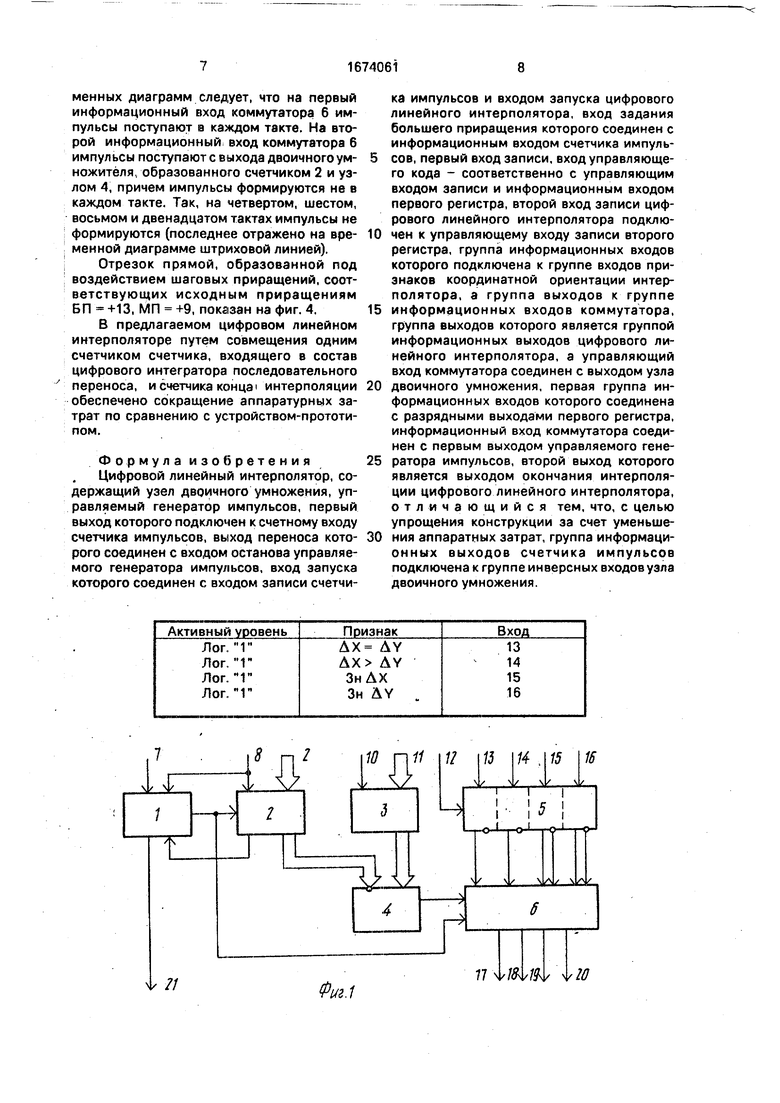

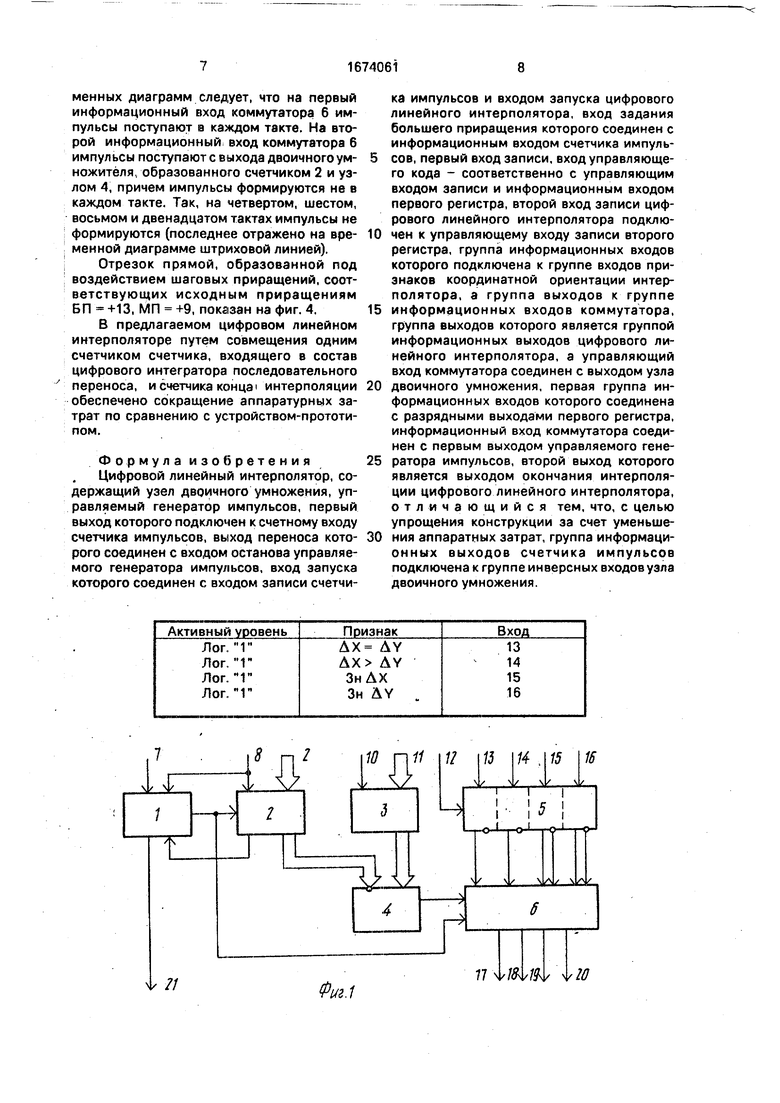

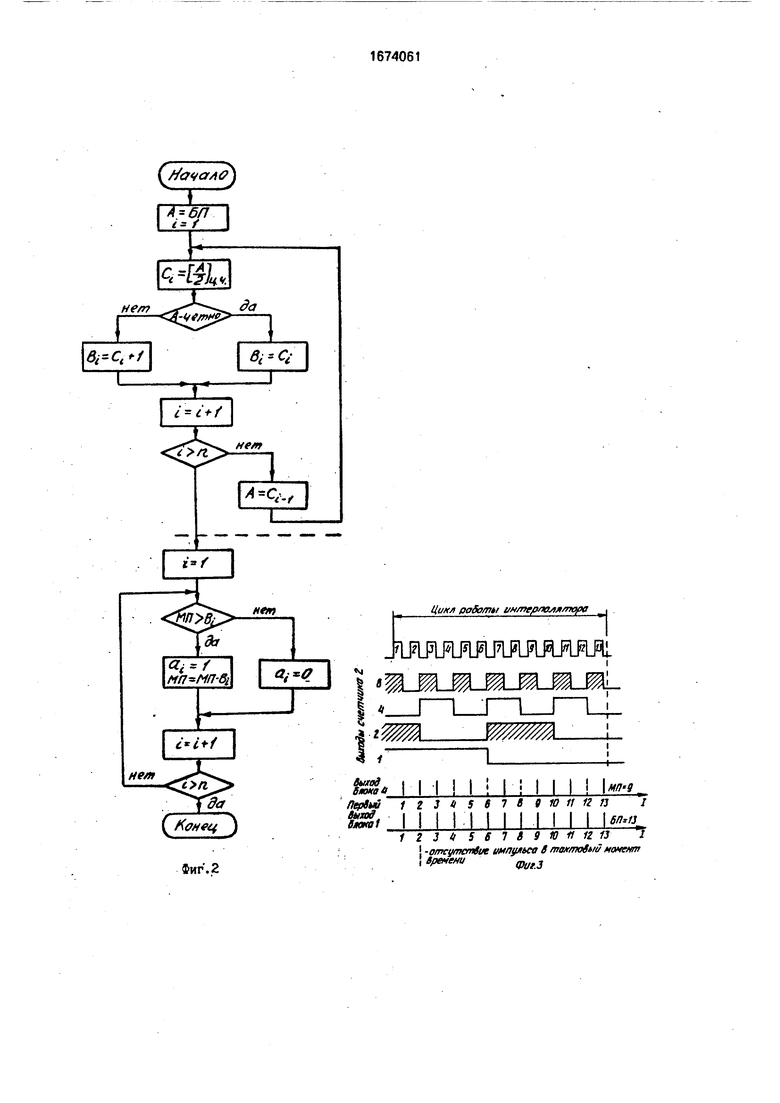

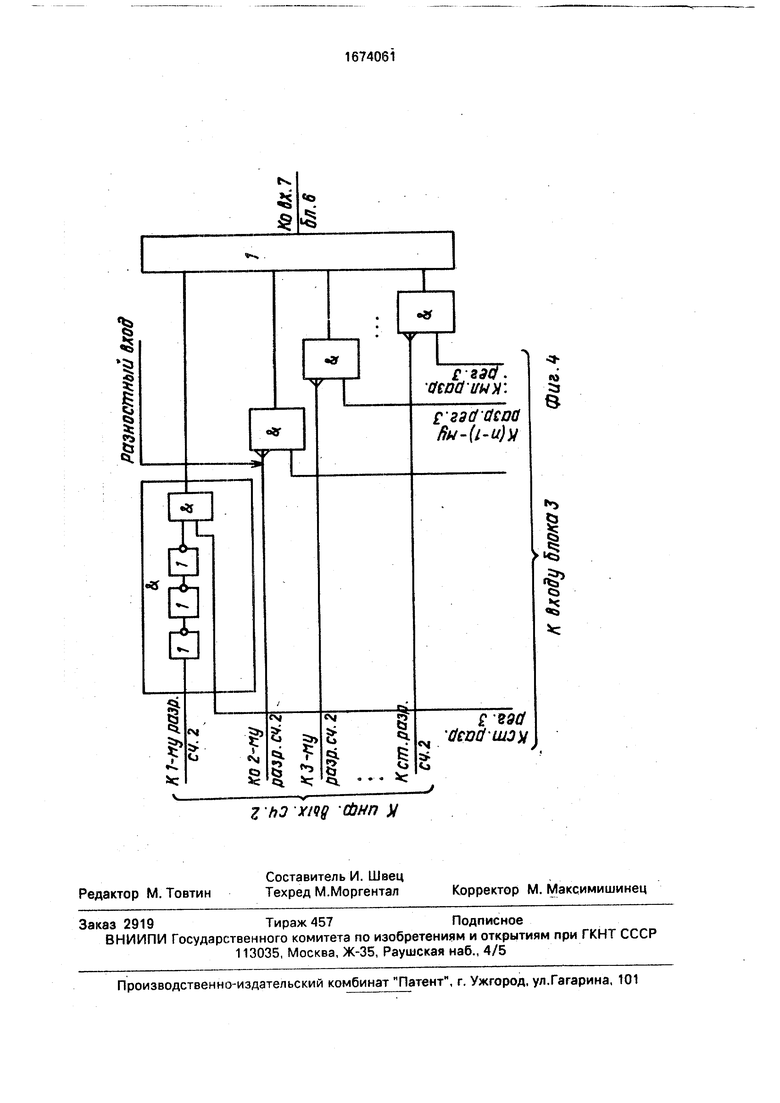

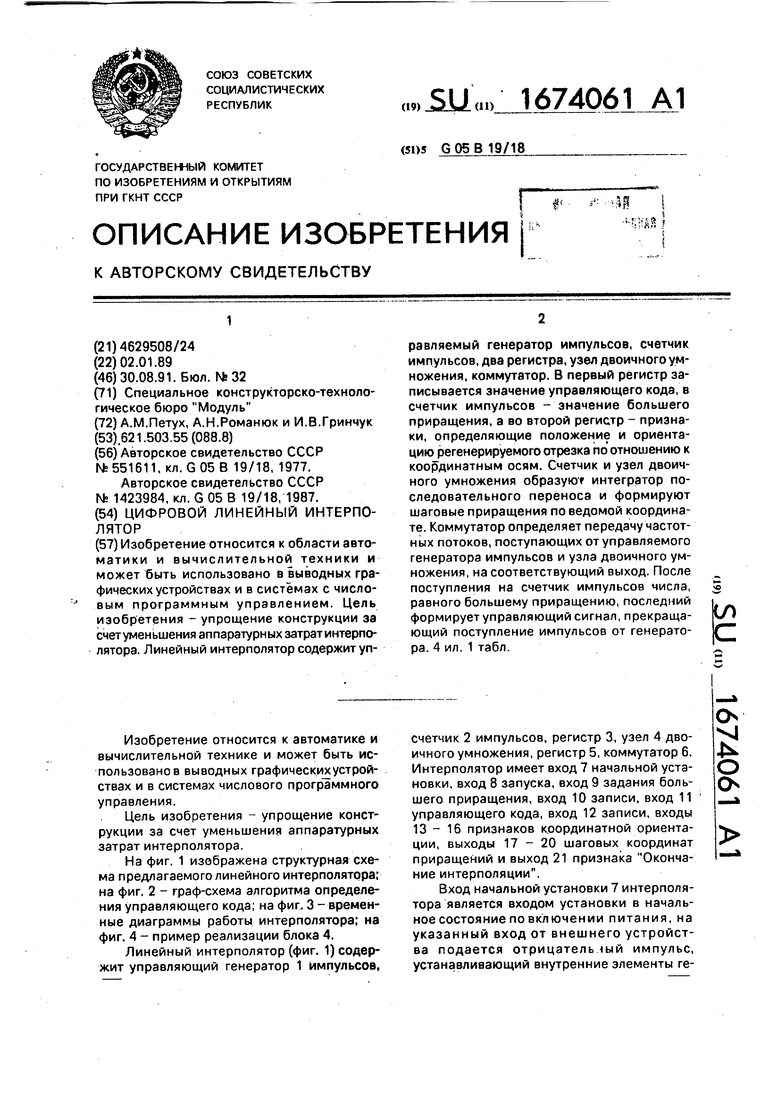

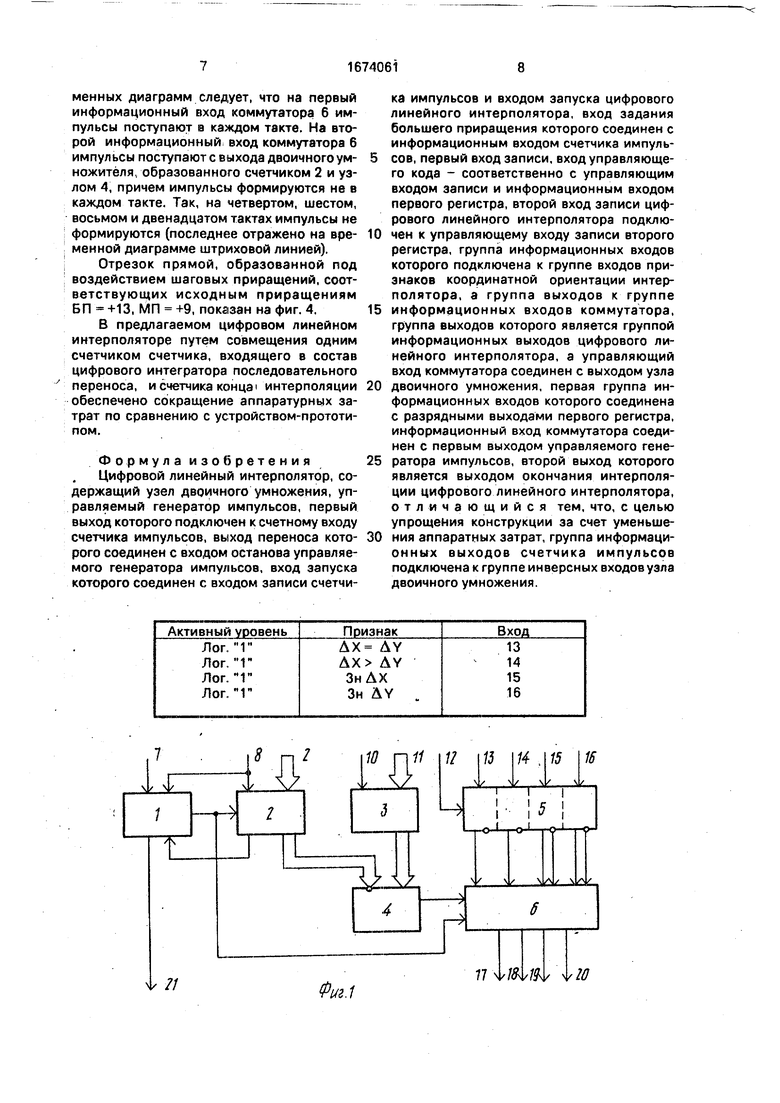

На фиг. 1 изображена структурная схема предлагаемого линейного интерполятора; на фиг. 2 - граф-схема алгоритма определения управляющего кода; на фиг. 3 - временные диаграммы работы интерполятора; на фиг. 4 - пример реализации блока 4.

Линейный интерполятор (фиг. содержит управляющий генератор 1 импульсов,

счетчик 2 импульсов, регистр 3, узел 4 двоичного умножения, регистр 5, коммутатор 6. Интерполятор имеет вход 7 начальной установки, вход 8 запуска, вход 9 задания большего приращения, вход 10 записи, вход 11 управляющего кода, вход 12 записи, входы 13 - 16 признаков координатной ориентации, выходы 17 - 20 шаговых координат приращений и выход 21 признака Окончание интерполяции.

Вход начальной установки 7 интерполятора является входом установки в начальное состояние по включении питания, на указанный вход от внешнего устройства подается отрицатель ый импульс, устанавливающий внутренние элементы гес vi

о о

нератора 1 импульсов в исходное состояние, по переднему фронту на входе 8 запуска генератор формирует на выходе последовательность импульсов до момента появления сигнала переноса на выходе счетчика 2. Активный уровень сигнала записи (вход 8 интерполятора) в счетчик 2 большего приращения - нулевой.

Сигнал на выходе переноса счетчика 2 формируется при переходе его из нулевого состояния в состояние , где у- разрядность счетчика 2. Выход переноса счетчика 2 соединен с входом останова управляемого генератора 1 импульсов. Информационный выход счетчика 2 подключен к инверсным входам младших разрядов узла 4 двоичного умножения.

Первый регистр 3 служит для хранения управляющего кода (УК), поступающего на вход УК 11 от внешнего устройства. Запись УК осуществляется нулевым сигналом на его входе записи, соединенном с входом записи УК-интерполятора,

Выход первого регистра 3 подключен к старшим разрядам адресного входа узла 4 двоичного умножения, выход которого соединен с седьмым входом коммутатора 6.

Узел 4 двоичного умножения обеспечивает отбор частотных последовательностей, формируемых на информационном выходе счетчика 2 в соответствии с управляющим кодом, а также осуществляет их суммирование. Узел 4 двоичного умножения и счетчик 2 образуют интегратор последовательного переноса.

Запись признаков во второй 5 регистр осуществляется нулевым уровнем, поступающим на вход 12 записи признаков регистра. Первый вход регистра 5 соединен с входом 13 признака ДХ Л У интерполятора, причем от внешнего устройства поступает уровейь 1 при условии АХ А У, где АХи AY модули приращений, задающих отрезок прямой. Второй вход регистра 5 соединен с входом 14признака

А X А У интерполятора, причем от внешнего устройства поступает уровень 1 при условии АХ А У. Третий и четвертый входы регистра 5 соединены соответственно с входами 15 знака АХ и 16 знака АУ, причем уровню О на указанных входах соответствует положительный знак приращения. Выходы регистра 2 соединены с первыми шестью входами коммутатора 6. Выходы 17, 18, 19, 20 интерполятора совпадают с первым, вторым, третьим и четвертыми выходами коммутатора 6. Указанные выходы являются соответственно выходами +Х. -X, +Y,-У интерполятора. Выход 21 генератора

1 импульсов является выходом признака Окончание интерполяции.

Интерполятор работает следующим образом.

В интерполяторе, как и в устройствепрототипе, в качестве основного реализующего элемента используется цифровой интегратор последовательного переноса, образованный счетчиком и узлом двоичного

умножения. Последний из них осуществляет отбор импульсов с выходом счетчика. Счетчик же служит для формирования импульсов, число которых за цикл пересчета определяет двоичные кодовые эквиваленты.

В устройстве-прототипе для определения конца интерполяции дополнительно введен еще один счетчик, работающий в режиме вычитания. Очевидно,что на выходах

счетчика за М тактов в режиме сложения сформируется столько же импульсов, сколько бы он сформировал в режиме вычитания от М до нуля. Отсюда следует, что счетчик, служащий в уотройстве-прототипе для выделения конца интерполяции, может быть использован и в качестве счетчика цифрового интегратора, т.е. имеется реальная возможность сокращения аппаратурных затрат интерполятора.

Следует отметить, что при использовании одного и того же импульса, в качестве элемента для выделения конца интерполяции и элемента цифрового интегратора, счетчик наиболее целесообразно использовать в режиме вычитания от М до нуля. Поскольку в данном случае изменяется активный фронт импульсов для узла двоичного умножения, то необходимо осуществить дополнительное их инвертирование.

Поскольку в интерполяторе шаговые приращения по ведущей координате формируются в каждом интерполяционном такте, то их число равно значению большего приращения (БП). Шаговые приращения по

ведомой координате формируются на выходе узла 4. При этом значение управляющего кода в регистре 3, должно быть таким, чтобы за число тактов, равных большему приращению, на выходе узла 4 было сформировано

число импульсов, соответствующее значению меньшего приращения (МП).

При применении цифрового интегратора

с последовательным переносом (счетчик 2 и

узел 4) количество импульсов Bi за счет 1-го

разряда управляющего кода за время БП

выразится соотношением

гБП + -I 81 L 2 .

БП + -i I -оператор выделения

целой части. Для того, чтобы за число тактов, равных БП, на выходе интегратора было сформировано МП импульсов, должно удовлетвориться соотношение

,1,

ai bi МП ,

где ai-значение цифры в 1-м разряде управ ляющего кода.

Таким образом, задача опеределения управляющего кода сводится к определению ai, a2,... an по известным значениям БП и МП с использованием приведенных соот- ношений. При этом находятся значения Bi или уравновешивается значение МП.

В предлагаемом линейном интерполяторе осуществляется задание отрезка прямой значением большего приращения, значением управляющего кода и признаками, задающими ориентацию и расположение векторов по отношению к координатным осям.

Интерполятор работает следующим об- разом.

По входу 7 интерполятора от внешнего устройства поступает импульс, устанавливающий генератор 1 импульсов в исходное состояние. На выходе генератора 1 им- пульсы не формируются В регистр 5 по активному уровню сигнала на входе 12 записываются значения признаков Соответствие между активными уровнями сигналов, признаками и соответствующими им входа- ми приведены в таблице.

В регистр 3 от внешнего устройства записывается значение управляющего кода, поступающего на вход 11 интерполятора. Запись в регистр осуществляется нулевым уровнем, подаваемым на вход 10 интерполятора.

В счетчик 2 записывается значение большего приращения, поступающего на вход 9 интерполятора. Запись БП осуще- ствляется нулевым уровнем сигнала, подаваемым на вход 9 интерполятора. По переднему фронту указанного сигнала запускается генератор 1 и на его выходе формируется последовательность им- пульсов заданной частоты. Указанная последовательность импульсов поступает на счетный вход счетчика 2. На выходе счетчика 2 формируются импульсы, число которых соответствует двоичным кодовым эквива- лентам. С выхода счетчика двоичные сигналы поступают на инверсный вход узла двоичного умножения, где осуществляется их отбор в соответствии с управляющим кодом, записанным в первый регистр 3. При этом на выходе двоичного умножителя А формируется последовательность импульсов, соответствующих меньшему приращению (по ведомой координате). Коммутатор 6 осуществляет в зависимости отзначения признаков, записанных в регистр 5, перекоммутацию частотных потоков, поступаемых от генератора 1 и двоичного умножителя 4 на один из выходов +Х, -X, +Y, -Y(17... 20).

С приходом каждого импульса от генератора 1 содержимое счетчика 2 уменьшается на единицу. При выдаче генератором 1 числа импульса, равного БП, на выходе счетчика 2 формируется сигнал переноса, приводящий к установке генератора 1 в исходное состояние, при котором импульсы на выход генератора 1 не выдаются. При выдаче импульсов генератора 1 на выходе 21 формируется уровень 1, сигнализирующий об генерации интерполятором шаговых приращений. После выдачи БП- импульсов на выходе 21 формируется сигнал О, сигнализирующий об готовности приема интерполятором новых исходных приращений.

Расчет управляющего кода может быть осуществлен по алгоритму (фиг. 2) микропроцессором или микроЭВМ. Часть граф- схемы алгоритма до штриховой линии служит для определения числа импульсов Bi за обьем 1-го разряда управляющего кода за время БП, по формуле:

в,- гБп.+

В|- | 2Г

Указанная формула реализуется последовательным сдвигом БП (деление на 2) и прибавление 1 при нечетном значении сдвигаемого операнда.

Нижняя часть граф-схемы алгоритма служит для определения значения цифр (О или1) в (-ом разряде управляющего кода путем уравновешивания кода МП весам Bi.

Временная диаграмма работы (фиг. 3) интерполятора приведена для МП 9, БП 13.

Для указанных приращений значение управляющего кода равно 1010, где 1 справа соответствует старшему разряду. На временной диаграмме заштрихованные импульсы, снимаемые с первого и третьего выходов счетчика 2 отбираются узлом 4 двоичного умножения и суммируются. Активным фронтом указанных импульсов является задний фронт. С выхода узла 4 двоичного умножения импульсы, снимаемые с первого и третьего выходов счетчика 2, поступают на вход коммутатора 6. Из временных диаграмм следует, что на первый информационный вход коммутатора 6 импульсы поступают в каждом такте. На второй информационный вход коммутатора 6 импульсы поступают с выхода двоичного умножителя, образованного счетчиком 2 и узлом 4, причем импульсы формируются не в каждом такте. Так, на четвертом, шестом, восьмом и двенадцатом тактах импульсы не формируются (последнее отражено на временной диаграмме штриховой линией).

Отрезок прямой, образованной под воздействием шаговых приращений, соответствующих исходным приращениям БП - +13, МП +9, показан на фиг. 4.

В предлагаемом цифровом линейном интерполяторе путем совмещения одним счетчиком счетчика, входящего в состав цифрового интегратора последовательного переноса, и счетчика конца1 интерполяции обеспечено сокращение аппаратурных затрат по сравнению с устройством-прототипом.

Формула изобретения Цифровой линейный интерполятор, содержащий узел двоичного умножения, управляемый генератор импульсов, первый выход которого подключен к счетному входу счетчика импульсов, выход переноса которого соединен с входом останова управляемого генератора импульсов, вход запуска которого соединен с входом записи счетчика импульсов и входом запуска цифрового линейного интерполятора, вход задания большего приращения которого соединен с информационным входом счетчика импульсов, первый вход записи, вход управляющего кода - соответственно с управляющим входом записи и информационным входом первого регистра, второй вход записи цифрового линейного интерполятора подключен к управляющему входу записи второго регистра, группа информационных входов которого подключена к группе входов признаков координатной ориентации интерполятора, а группа выходов к группе

информационных входов коммутатора, группа выходов которого является группой информационных выходов цифрового линейного интерполятора, а управляющий вход коммутатора соединен с выходом узла

двоичного умножения, первая группа информационных входов которого соединена с разрядными выходами первого регистра, информационный вход коммутатора соединен с первым выходом управляемого генератора импульсов, второй выход которого является выходом окончания интерполяции цифрового линейного интерполятора, отличающийся тем, что, с целью упрощения конструкции за счет уменьшения аппаратных затрат, группа информационных выходов счетчика импульсов подключена к группе инверсных входов узла двоичного умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1615744A2 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

| Линейный интерполятор | 1985 |

|

SU1272310A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в выводных графических устройствах и в системах с числовым программным управлением. Цель изобретения - упрощение конструкции за счет уменьшения аппаратурных затрат интерполятора. Линейный интерполятор содержит управляемый генератор импульсов, счетчик импульсов, два регистра, узел двоичного умножения, коммутатор. В первый регистр записывается значение управляющего кода, в счетчик импульсов - значение большего приращения, а во второй регистр - признаки, определяющие положение и ориентацию регенерируемого отрезка по отношению к координатным осям. Счетчик и узел двоичного умножения образуют интегратор последовательного переноса и формируют шаговые приращения по ведомой координате. Коммутатор определяет передачу частотных потоков, поступающих от управляемого генератора импульсов и узла двоичного умножения, на соответствующий выход. После поступления на счетчик импульсов числа, равного большему приращению, последний формирует управляющий сигнал, прекращающий поступление импульсов от генератора. 4 ил.

21

Фиг.1

П 13 14 15 16

Nixч|/

ТI

II и I

О / WЧЛ

77 Ш& /

10

7/ачал0

л-с

нет

и,« I I I I I I I I мич

ПерВм 113 5818910111213 I Выад i i i i i i i i i i i i i ,

бигод Вяокой

Выход, I I I I I I I I I I

вяжа I I I I I I I I I I ...

1234S67S9V fZfJ

6Л П

tf Wflt +

-otrvymcmtue инпульса В тактов w манент 14Mww j

Цикл роботы ун/перлоля пора

.

Щ ЖЖЖЖЖ Ш1

и,«

бигод Вяокой

I ,

6Л П

34S67S9V fZfJ

tf Wflt +

-otrvymcmtue инпульса В тактов w манент 14Mww j

1

о

5

в

I

t 5

| Цифровой линейный интерполятор | 1975 |

|

SU551611A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-08-30—Публикация

1989-01-02—Подача