Фиг /

Изобретение относится к области вычислительной техники и может быть исполь- зовано для управления оперативной памятью в микропроцессорных системах,

Цель изобретения - повышение быстродействия устройства.

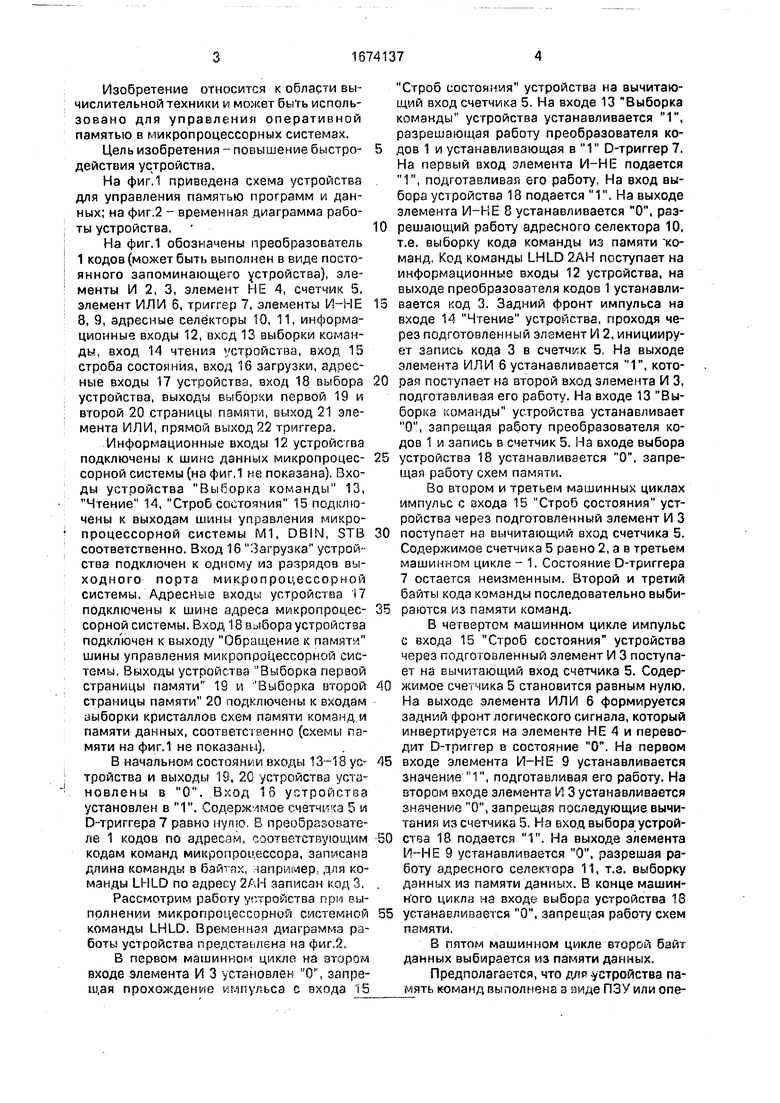

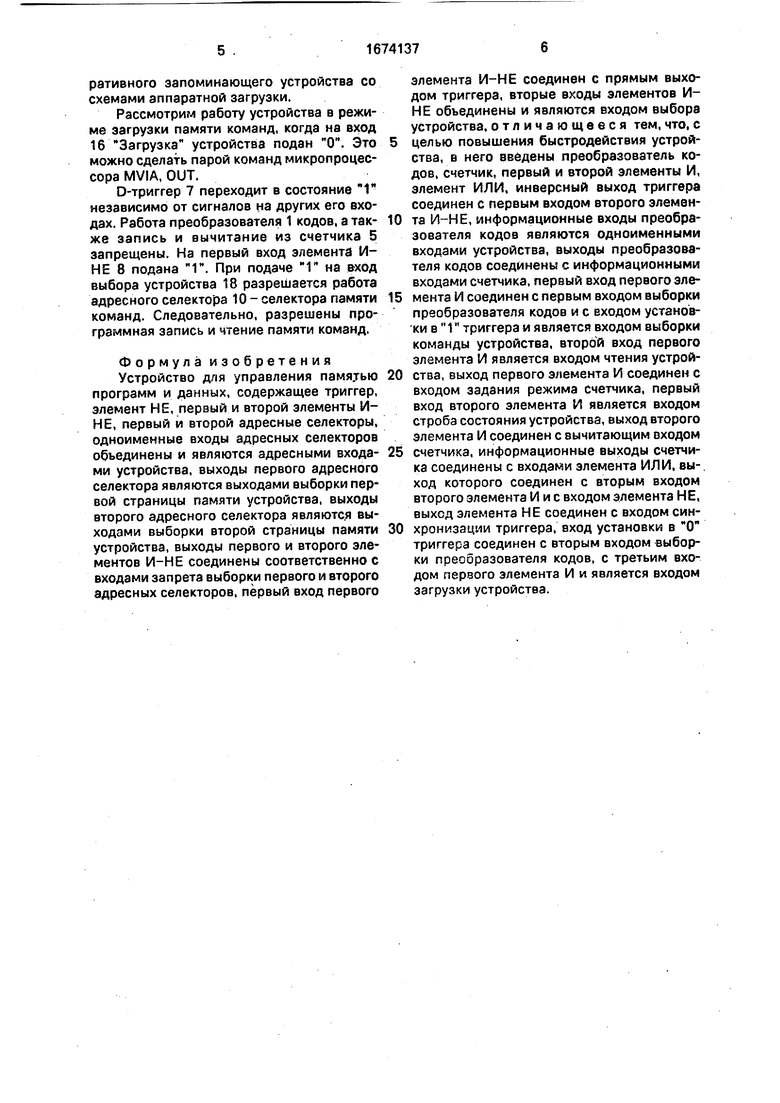

На фиг.1 приведена схема устройства для управления памятью программ и данных; на фиг.2 - временная диаграмма работы устройства.

На фиг.1 обозначены преобразователь 1 кодов (может быть выполнен в виде постоянного запоминающего устройства), элементы И 2, 3, элемент НЕ 4, счетчик 5, элемент ИЛИ 6, триггер 7, элементы И-НЕ 8, 9, адресные селекторы 10, 11, информационные входы 12, вход 13 выборки команды, вход 14 чтения устройства, вход 15 строба состояния, вход 16 загрузки, адресные входы 17 устройства, вход 18 выбора устройства, выходы выборки первой 19 и второй 20 страницы памяти, выход 21 элемента ИЛИ, прямой выход 22 триггера.

Информационные входы 12 устройства подключены к шине данных микропроцессорной системы (на фиг.1 не показана). Входы устройства Выборка команды 13, Чтение 14, Строб состояния 15 подключены к выходам шины управления микропроцессорной системы М1, DBIN, STB соответственно. Вход 16 Загрузка устройства подключен к одному из разрядов выходного порта микропроцессорной системы. Адресные входы устройства 17 подключены к шине адреса микропроцессорной системы. Вход 18 выбора устройства подкл ючен к выходу Обращение к памяти шины управления микропроцессорной системы. Выходы устройства Выборка первой страницы памяти 19 и Выборка второй страницы памяти 20 подключены к входам аыборки кристаллов схем памяти команд и памяти данных, соответственно (схемы памяти на фиг.1 не показаны).

В начальном состоянии входы 13-18 устройства и выходы 19, 20 устройства установлены в О. Вход 16 устройства установлен в 1. Содержимое счетчика 5 и D-триггера 7 равно нулю. В преобразователе 1 кодов по адресам, соответствующим кодам команд микропроцессора, записана длина команды в байтах, например, для команды LHLD по адресу 2АН записан код 3. Рассмотрим работу устройства при выполнении микропроцессорной системной команды LHLD. Временная диаграмма работы устройства представлена на фиг.2.

В первом машинном цикле на втором входе элемента И 3 установлен 0й, запрещая прохождение импульса с входа )5

Строб состояния устройства на вычитающий вход счетчика 5. На входе 13 Выборка команды устройства устанавливается Г, разрешающая работу преобразователя кодов 1 и устанавливающая в 1 D-триггер 7. На первый вход элемента И-НЕ подается 1, подготавливая его работу. На вход выбора устройства 18 подается 1, На выходе элемента И-НЕ 8 устанавливается О, раз0 решающий работу адресного селектора 10, т.е. выборку кода команды из памяти команд. Код команды LHLD 2AH поступает на информационные входы 12 устройства, на выходе преобразователя кодов 1 устанавли5 вается код 3. Задний фронт импульса на входе 14 Чтение устройства, проходя через подготовленный элемент И 2, инициирует запись кода 3 в счетчик 5, На выходе элемента ИЛИ 6 устанавливается 1, кото0 рая поступает на второй вход элемента И 3, подготавливая его работу. На входе 13 Выборка команды устройства устанавливает О, запрещая работу преобразователя кодов 1 и запись в счетчик 5. На входе выбора

5 устройства 18 устанавливается О, запрещая работу схем памяти.

Во втором и третьем машинных циклах импульс с входа 15 Строб состояния устройства через подготовленный элемент И 3

0 поступает на вычитающий вход счетчика 5. Содержимое счетчика 5 равно 2, а в третьем машинном цикле - 1. Состояние D-триггера 7 остается неизменным. Второй и третий байты кода команды последовательно выби5 раются из памяти команд.

В четвертом машинном цикле импульс с входа 15 Строб состояния устройства через подготовленный элемент И 3 поступает на вычитающий вход счетчика 5. Содер0 жимое счетчика 5 становится равным нулю. На выходе элемента ИЛИ 6 формируется задний фронт логического сигнала, который инвертируется на элементе НЕ 4 и переводит D-триггер в состояние О. На первом

5 входе элемента И-НЕ 9 устанавливается значение 1, подготавливая его работу. На втором входе элемента И 3 устанавливается значение О, запрещая последующие вычитания из счетчика 5. На вход выбора устрой0 стоа 18 подается 1. На выходе элемента И-НЕ 9 устанавливается О, разрешая работу адресного селектора 11, т.е. выборку данных из памяти данных. В конце машинного цикла на входе выбора устройства 18

5 устанавливается 0й, запрещая работу схем памяти.

В пятом машинном цикле второй байт данных выбирается из памяти данных.

Предполагается, что для устройства память команд выполнена а виде ПЗУ или oneративного запоминающего устройства со схемами аппаратной загрузки.

Рассмотрим работу устройства в режиме загрузки памяти команд, когда на вход 16 Загрузка устройства подан О. Это можно сделать парой команд микропроцессора MVIA. OUT.

D-триггер 7 переходит в состояние 1 независимо от сигналов на других его входах. Работа преобразователя 1 кодов, а так- же запись и вычитание из счетчика 5 запрещены. На первый вход элемента И- НЕ 8 подана Г. При подаче 1 на вход выбора устройства 18 разрешается работа адресного селектора 10 - селектора памяти команд. Следовательно, разрешены программная запись и чтение памяти команд.

Формула изобретения Устройство для управления памятью программ и данных, содержащее триггер, элемент НЕ. первый и второй элементы И- НЕ, первый и второй адресные селекторы, одноименные входы адресных селекторов объединены и являются адресными входа- ми устройства, выходы первого адресного селектора являются выходами выборки первой страницы памяти устройства, выходы второго адресного селектора являются выходами выборки второй страницы памяти устройства, выходы первого и второго элементов И-НЕ соединены соответственно с входами запрета выборки первого и второго адресных селекторов, первый вход первого

элемента И-НЕ соединен с прямым выходом триггера, вторые входы элементов И- НЕ объединены и являются входом выбора устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены преобразователь кодов, счетчик, первый и второй элементы И. элемент ИЛИ, инверсный выход триггера соединен с первым входом второго элемента И-НЕ, информационные входы преобразователя кодов являются одноименными входами устройства, выходы преобразователя кодов соединены с информационными входами счетчика, первый вход первого элемента И соединен с первым входом выборки преобразователя кодов и с входом установки в Г триггера и является входом выборки команды устройства, второй вход первого элемента И является входом чтения устройства, выход первого элемента И соединен с входом задания режима счетчика, первый вход второго элемента И является входом строба состояния устройства, выход второго элемента И соединен с вычитающим входом счетчика, информационные выходы счетчика соединены с входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И и с входом элемента НЕ, выход элемента НЕ соединен с входом синхронизации триггера, вход установки в О триггера соединен с вторым входом выборки преобразователя кодов, с третьим входом первого элемента И и является входом загрузки устройства.

Фиг.I

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для отладки программ | 1985 |

|

SU1298752A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Устройство управления процессом приготовления многокомпонентных смесей | 1989 |

|

SU1688127A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство для отладки программ | 1988 |

|

SU1608673A1 |

Изобретение относится к области вычислительной техники и может быть использовано для управления оперативной памятью в микропроцессорных системах. Цель изобретения - повышение быстродействия устройства. Устройство содержит преобразователь 1 кодов, элементы И 2, 3, элемент НЕ 4, счетчик 5, элемент ИЛИ 6, триггер 7, элементы И-НЕ 8, 9, адресные селекторы 10, 11, информационные 12 входы, вход 13 выборки команды, вход 14 чтения устройства, вход 15 строба состояния, вход 16 загрузки, адресные входы 17, вход 18 выбора, выходы выборки первой 19 и второй 20 страницы памяти. 1 ил.

Авторы

Даты

1991-08-30—Публикация

1988-11-21—Подача