Изобретение относится к автоматике и вычислительной технике и может быть использовано в микропроцессорных вычислительных системах.

Известны устррйства регенерации динамической памяти, в которых используется асинхронный режим обработки запросов обращений к памяти со стороны процессора. Эти устройства получили широкое распространение благодаря своей универсальности и независимости от типа вычислительной системы, в которой динамическая память применяется. Основными элементами таких устройств являются:двоичный счетчик,адресный коммутатор и схема арбитр. В схему - арбитр поступают сигналы запросов обращения к памяти и сигналы состояния памяти. На основании этих сигналов арбитр определяет последовательность обработки запросов и производит запуск циклов записи, чтения или регенерации памяти .

недостатком устройства являются большие потери времени.

Наиболее близким техническим решением к изобретению -является устройство, в котором в качестве арбитра применяется встроенный в микропроцессор (МП) типа К580ИК80 алгоритм обработки запросов обращений модуля прямого доступа к памяти (ПДП).

Устройство содержит триггер запроса и триггер коммутации, элемент ИЛИ-НЕ, первый и второй входы которого подключены к первой и второй шинам запроса соответственно, а выход элемента ИЛИ-НЕ соединен с информационным входом сдвигового

10 регистра, коммутатор, первый вход которого подключен к выходу счетчика адреса, и дешифратор, выхода которого соединены с первыми входами элементов ИЛИ, причем входы эле15ментов ИЛИ подключены к шинам выборки адреса памяти 2.

Недостатком асинхронного устройства регенерации динамической памяти является простой процессора во

20 время регенерации. Коэффициент потерь зависит от типа дингимической памяти, длительности цикла обращения к памяти, периода регенерации и определяется выражением;

25

-100%,

Ти

где NJ. - чйсЛо строк (столбцов) матрицы памяти;

длительность цикла обращения;

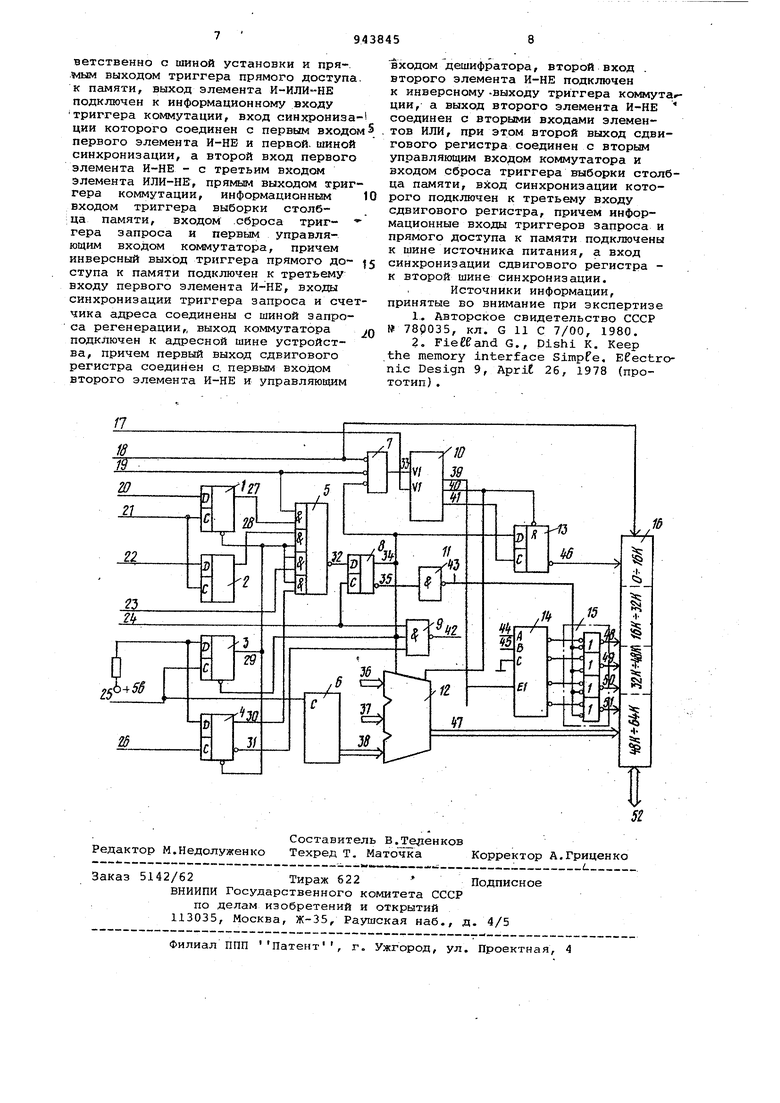

30 Т - период регенерации. Для динамической памяти типа К565РУЗА эти потери составляют 3,2% процессорного времени. В устройстве эти потери времени увеличиваются еще примерно вдвое, поскольку необходима синхронизация микропроцессора в режиме Захват шин . Невозможно также использование в микропроцессорной вычислительной системе модуля ПДП типа К580ИК57, так как шины Захват и Подтверждениз захвата МП заняты для целей регенерации памяти. Цель изобретения - повышение быстродействия устройства регенерации динамической памяти путем выполнения регенерации памйти в те- мо менты времени, когда МП находится в такте, не требующем обращения к ней. Таким тактом для МП типа К580ИК80 является четвертый такт цикла выборки команды, в котором МП занят ее дешифрацией. Поставленная цель достигается т что в устройство введены триггеры выборки команды останова, прямого д ступа к памяти и триггер выборки столбца памяти, элемент И-ИЛИ-НЕ, первый и второй элементы И-НЕ, при этом входы синхронизации триггеров выборки команды и останова подключены к шине строба, первый вход элемента И-ИЛИ-НЕ соединен с второй шиной запроса, второй и третий входы - с прямыми выходами триггеров выборки команды и останова соответственно, четвертый вход элемента И-ИЛИ-НЕи входы сброса триггеров выборки команды и прямого доступа к памяти подключены к прямому выходу триггера запроса, а пятый и шестой входы элемента И-ИЛИ-НЕ соединены соответственно с шиной установки и прямым выходом триггера прямого доступа к памяти, выход элемента ИИЛИ-НЕ подключен к информационному входу триггера коммутации, вход синхронизации которого соединен с первым входом первого элемента И-НЕ и первой шиной синхронизации, а второй вход первого элемента И-НЕ с третьим входом элемента ИЛИ-НЕ, прямым выходом триггера коммутации информационньом входом триггера выборки столбца памяти, входом сброса триггера запроса и первым управляющим входом коммутатора, причем инверсный выход триггера прямого доступа к памяти подключен к третьему входу первого элемента И-НЕ, входы синхронизации триггера запроса и счетчика адреса соединены с шиной запроса регенерации, выход коммутатора подключен к адресной шине уст ройства, причем первый выход сдвигового регистра соединен с первым входом второго элемента И-НЕ и управляющим входом дешифратора, второй вход второго элемента И-НЕ подключен к инверсному выходу триггера коммутации, а выход второго элемента И-НЕ соединен с вторыми входами элементов ИЛИ, при второй выход сдвигового регистра соединен со вторым управляющим входом коммутатора и входом сброса триггера выборки столбца памяти, вход синхронизации которого подключен к третьему выходу сдвигового регистра, причем информационные входы триггеров запроса и прямого доступа к памяти подключены к шине источника питания, а вход синхронизации сдвигового регистра - к второй шине синхронизации. На чертеже приведена функциональная Схема предлагаемого устройства. Устройство содержит триггеры выборки команды 1, останова 2, запроса регенерации 3, прямого доступа и памяти 4, коммутации 8 и выборки столбца памяти 13, элемент И-ИЛИ-НЕ 5, счетчик адреса 6, элемент ИЛИ-НЕ 7, первый и второй элементы И-НЕ 9 и И, сдвиговый регистр 10, коммутатор адресных шин 12, дешифратор 14, элемент-ИЛИ 15, динамическую память 16, первую и вторую шины синхронизации 24 и 17, первую и вторую шины запроса 18 и 19, шины данных микропроцессора 20 и 21, шины сброса, установки, и запроса регенерации 22, 23 и 25, шину Строб адреса модуля ПДП 26, шины выходов триггеров выборки команды, останова, запроса регенерации и модуля ПДП 2731, шины выхода элементов И-ИЛИ-НЕ, ИЛИ-НЕ 32 и 33, прямую и инверсную шины выхода триггера коммутации 34 и 35, адресные шины МП АО-Аб и А7-А13 36 и 37, выходные шины адресного счетчика 38, выходные шины сдвигового регистра 39-41, шины выхода первого и второго, элементов И-НЕ 42 и 43, старшие разряды адреса МП - 44 и 45, инверсный выход триггера выборки столбца 46, адресные шины памяти 47, шины выборки строки матрицы памяти 48-51 и шины данных 52. Рассмотрим работу устройства в то время, когда нет запроса регенерации памяти. В этом случае триггеры 1-4 сброшены и синхроимпульс первой шины синхронизации 24 (Ф2-ТТЛ) установит триггер коммутации 8 в неактивное единичное состояние. Сигналы обращения к памяти Запись 18 и Чтение 19 проходят через элемент ИЛИ-НЕ 7 и устанавливают высокий уровень напряжения на последовательном входе 33 сдвигового регистра 10. Высокочастотные синхроимпульсы второй шины синхронизации 17 (длительность такта не) сдвигают этот уровейь, который, появившись на шине 39, разрешает работу дешифратора блоков памяти 14, выходы которого в свою очередь, пройдя через элементы ИЛИ 15, стробируют и записывают мла.цшие разряды адреса МП АО-А6 (36) на внутренний регистр строки матрицы выбранного блока (сигнал RAS). Сигнал нулевого уровня напряжения, на шине 48 выбирают блок памят О-16К, на шине 49-16К-32К, на шине 50 - 32К-48К и на шине 51- 48К-64К. В следующем такте сдвигового регистра 10 единичный уровень появляется на шине 40 и переключает коммутатор адресных шин 12 таким образом, что адресные разряды МП А7-А13 (37) проходят на адресную шину-памяти 47. Положительный фронт на шине 41 установит триггер 13 в единичное состояни и на его выходе 46 появится сигнал, записывающий адресные разряды А7-А13 на внутренний регистр столбца матрицы памяти (сигнал CAS). После снятия МП сигналов запроса 18 и 19 сдвиговой регистр 10, триггер 13 и коммута тор 12 возвращаются в первоначальное состояние. Если на шине 25 появился сигнал запроса регенерации динамической памяти 16, то устанавливается в единич ное состояние триггер запроса 3, разрешив таким образом работу триггерам выборки команды 1 и прямого доступа к памяти 4, и увеличивается на единицу содержимое адресного счетчика 6. В очередном цикле выборк команды в первом такте цикла на шине 20 (шина данных Д5) МП устанавливает единичный уровень, который .сигналом строб 22 (Статус-строб) переносится на шину 27. Во втором и третьем такте этого цикла МП выдает сигнал запроса 1 Чтение который и-отрабатывается описанным спо собом. В четвертом такте цикла выбор ки команды сигнал Чтение сбрасывает ся и МП переходит к дешифрации выбранной команды. После сброса сигнала на шине 19 срабатывает элемент . И-ИЛИ-НЕ 5 и нулевой уровень напряжения на шине 32 переписывается поло жительным фронтом синхроимпульса шины 24 на шину 34, запуская таким образом снова цикл работы памяти и сбр сывая триггер запроса регенерации 3. Так как на шине 35 теперь высокий уровень напряжения, то при появлеНИИ высокого уровня и на выходе втор го триггера сдвигового регистра 39 срабатывает второй элемент И-НЕ 11, и сигнал выборки строки матрицы памяти, пройдя через элементы ИЛИ 15, Появляется одновременно на входах всех блоков памяти (шины 48-51). В этот момент времени кадресным шинам 47 коммутатор 12 подклгочает выходы 38 адресного счетчика 6. Сигнал выборки столбцов матрицы памяти 46 не включается, так как на информационнее входе триггера 13 установлен нулевой уровень напряжения. Вследствие того, что триггеры запроса 3 и выборки ксяланды 1 при срабатывании триггера коммутации 8 сбрасываются,, очередной положительный фронт импульса синхросерии на шине 24 возвращает в начальное состояние триггер коммутации 8, и цикл регенерации памяти на этом заканчивается. Помимо цикла выборки команды регенерация памяти разрешена также при подаче сигнала начальной установки 23 (Системный сброс ) и переходе МП в режим Останов, который фиксируется триггером 2. Если в микропроцессорной системе работает мо- дуль ПДП, то МП может находиться в режиме Захват. В таком случае цикл регенерации запускается сигналом Строб адреса (шина 26), выдаваемого модулем ПДП. Этот сигнал устанавливает в единичное состояние триггер 4, который задерживает на один такт (время регенерации памяти) импульсы первой синхросерии, поступающих к модулю ПДП по шине 42. Формула изобретения Устройство для регенерации динамической памяти, содержащее триггер запроса и триггер коммутации, элемент ИЛИ-НЕ, первый и второй входы которого подключены к первой и второй шинам запроса соответственно, а выход элемента ИЛИ-НЕ соединен с информационным входом сдвиго- вого регистра, коммутатор, первый вход которого подключен к вйходу счетчика адцзеса, и дешифратор, выходы которого соединены с первыми входами элементов ИЛИ, причем выходы элементов ИЛИ подключены к шинам выборки адреса, отличающеес я тем, что, с целью повышения быстродействия устройства, в него введены триггеры выборки команды, останова, прямого доступа к памяти и триггер выборки столбца памяти, элемент И-ИЛИ-НЕ, первый и второй элементы И-НЕ, при этом входы синхронизации триггеров выборки команды и останова подключены -к шине строба, первый вход элемента И-ИЛИНЕ соединен с второй шиной запроса, второй и третий входы - с прямыми выходами триггеров выборки команды и останова соответственно, четвертый вход элемента И-ИЛИ-НЕ и входы сброса триггеров выборки команды и прямого доступа к памяти подключены к прямому выходу триггера запроса, а пятый и шестой входы элемента И-ИЛИ-НЕ соединены соответственно с шиной установки и пря-. .мым выходом триггера прямого доступа к памяти, выход элемента И-ИЛИ-НЕ подключен к информационному входу триггера коммутации, вход синхронизации которого соединен с первым входом первого элемента И-НБ и первой, шиной синхронизации, а второй вход первого элемента И-НЕ - с третьим входом элемента ИЛИ-НЕ, прямым выходом триггера коммутации, информационным входом триггера выборки столб:ца памяти, входом .сброса триг- гера запроса и первым управляющим входом коммутатора, причем инверсный выход триггера прямого доступа к памяти подключен к третьему входу первого элемента И-НЕ, входы синхронизации триггера запроса и счетчика адреса соединены с шиной запроса регенерации,, выход коммутатора подключен к адресной шине устройства, причем первый выход сдвигового регистра соединен с. первым входом второго элемента И-НЕ и управляющим

входом дешифратора, второй вход . второго элемента И-НЕ подключен к инверсному -выходу триггера коммута ции, а выход второго элемента И-НЕ соединен с вторыми входами элементов ИЛИ, при этом второй выход сдвигового регистра соединен с вторым управляющим входом коммутатора и входом сброса триггера выборки столбца памяти, вход синхронизации которого подключен к третьему входу сдвигового регистра, причем информационные входы триггеров запроса и прямого доступа к памяти подключены к шине источника питания, а вход синхронизации сдвигового регистра к второй шине синхронизации.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 789035, кл. G 11 С 7/00, 1980.

2,FieК and G., plshi К. Keep

the memory interface SimpPe, Electronic Design 9, Aprit 26, 1978 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1981 |

|

SU1275453A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство сопряжения с памятью | 1985 |

|

SU1262515A1 |

| Запоминающее устройство | 1989 |

|

SU1695382A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для ввода информации от аналоговых датчиков | 1988 |

|

SU1578706A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

Авторы

Даты

1982-07-15—Публикация

1980-11-21—Подача