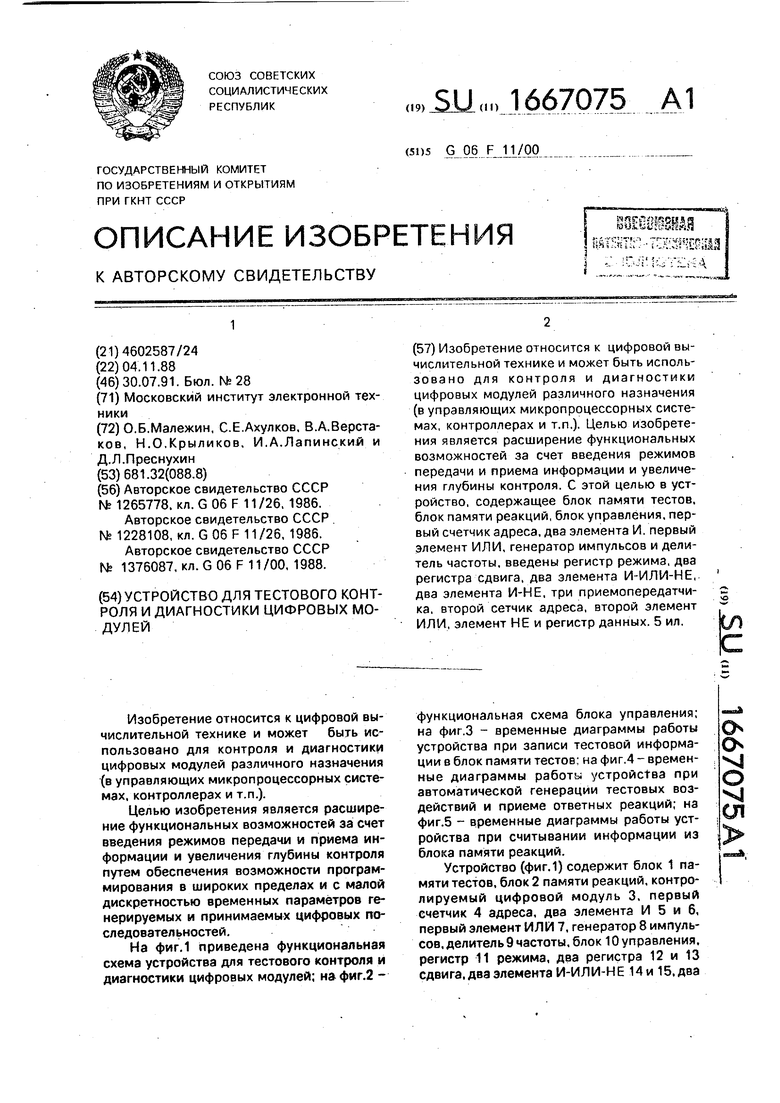

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностики цифровых модулей различного назначения (в управляющих микропроцессорных системах, контроллерах и т.п.).

Целью изобретения является расширение функциональных возможностей за счет введения режимов передачи и приема информации и увеличения глубины контроля путем обеспечения возможности программирования в широких пределах и с малой дискретностью временных параметров генерируемых и принимаемых цифровых последовательностей.

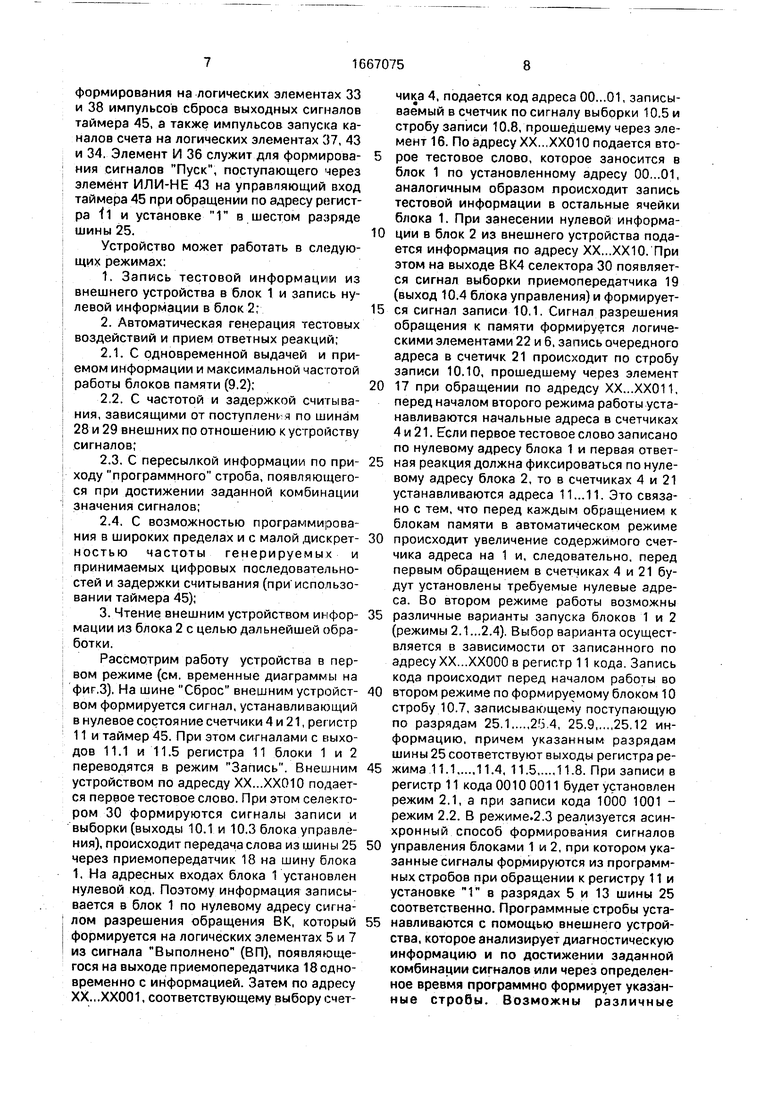

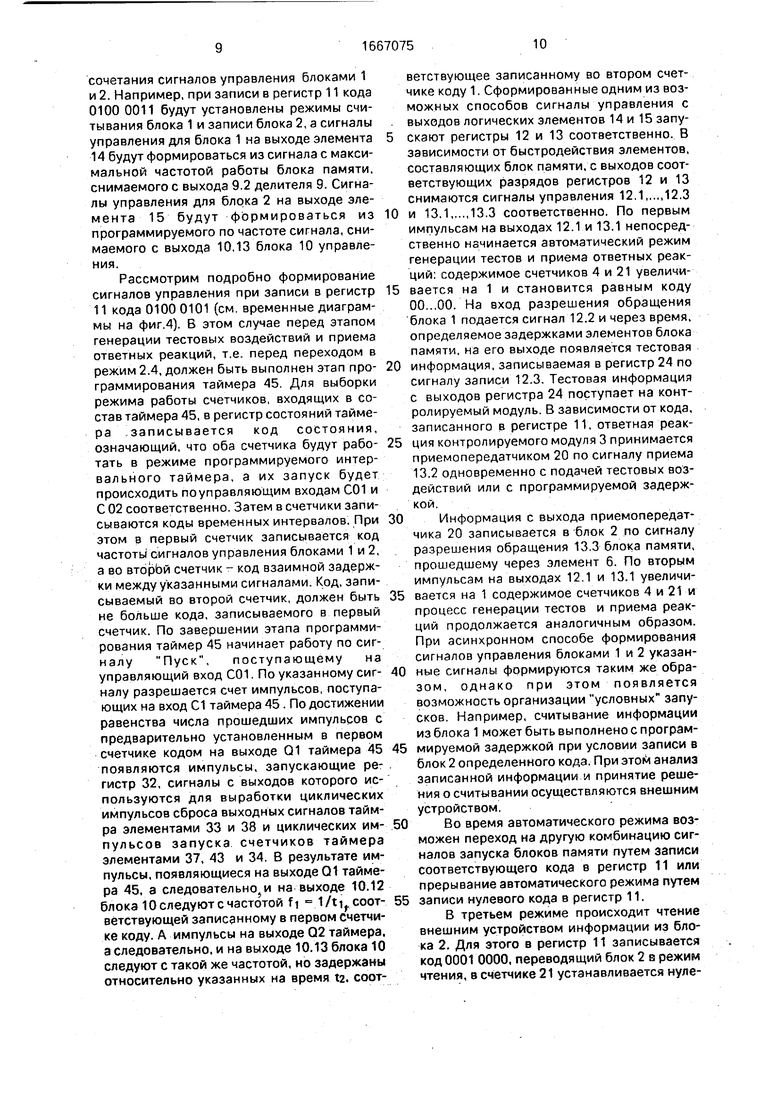

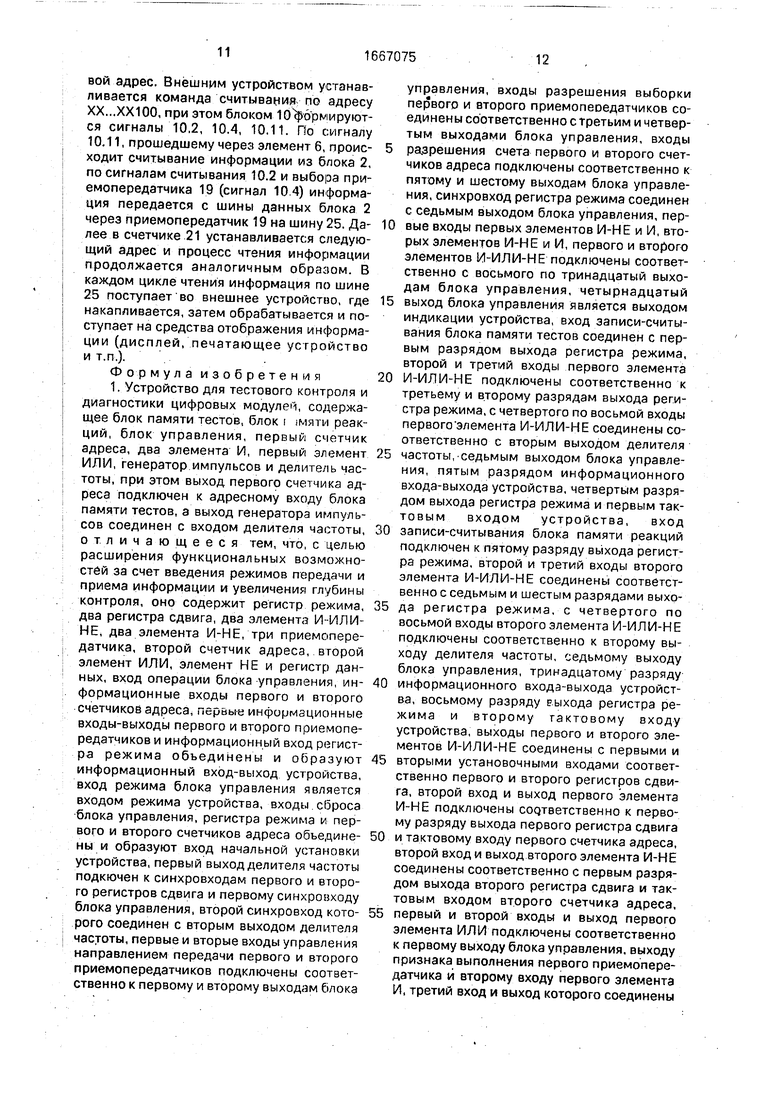

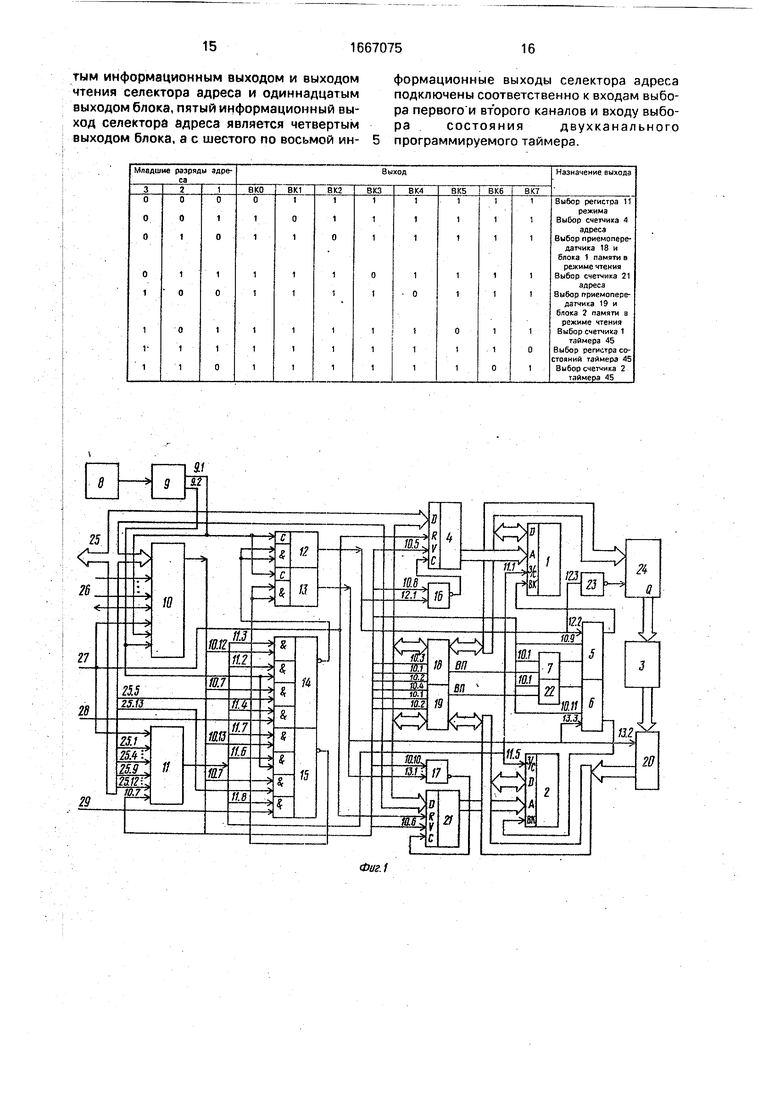

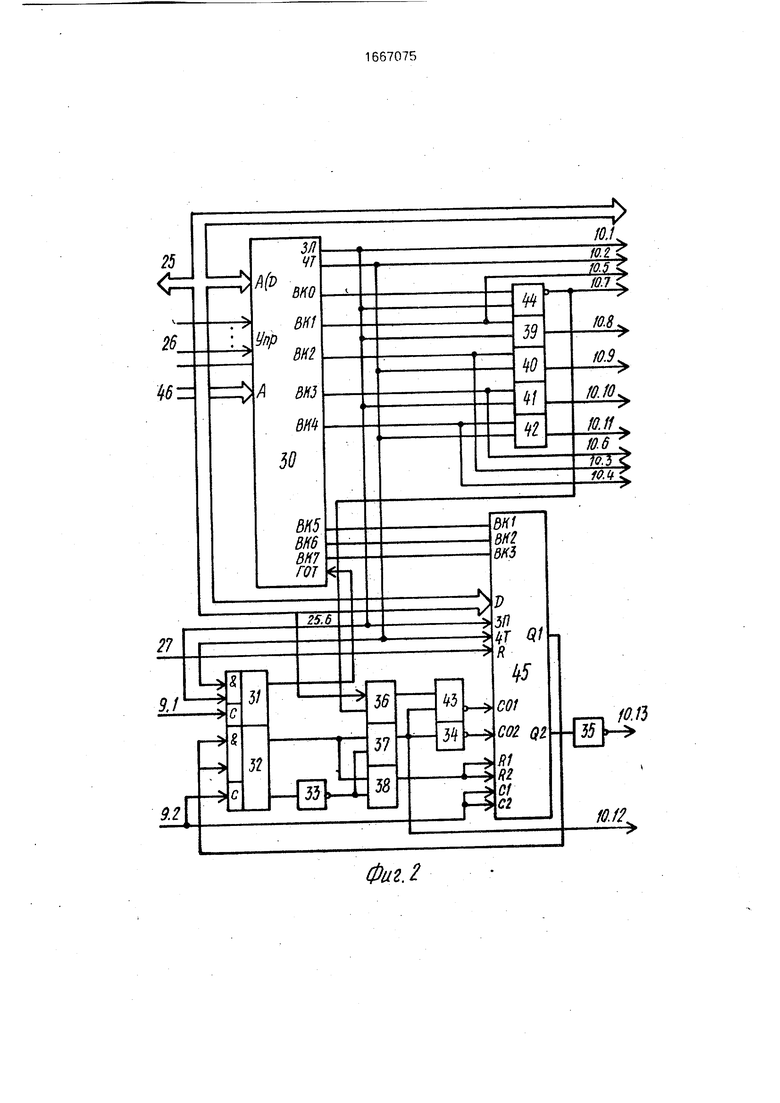

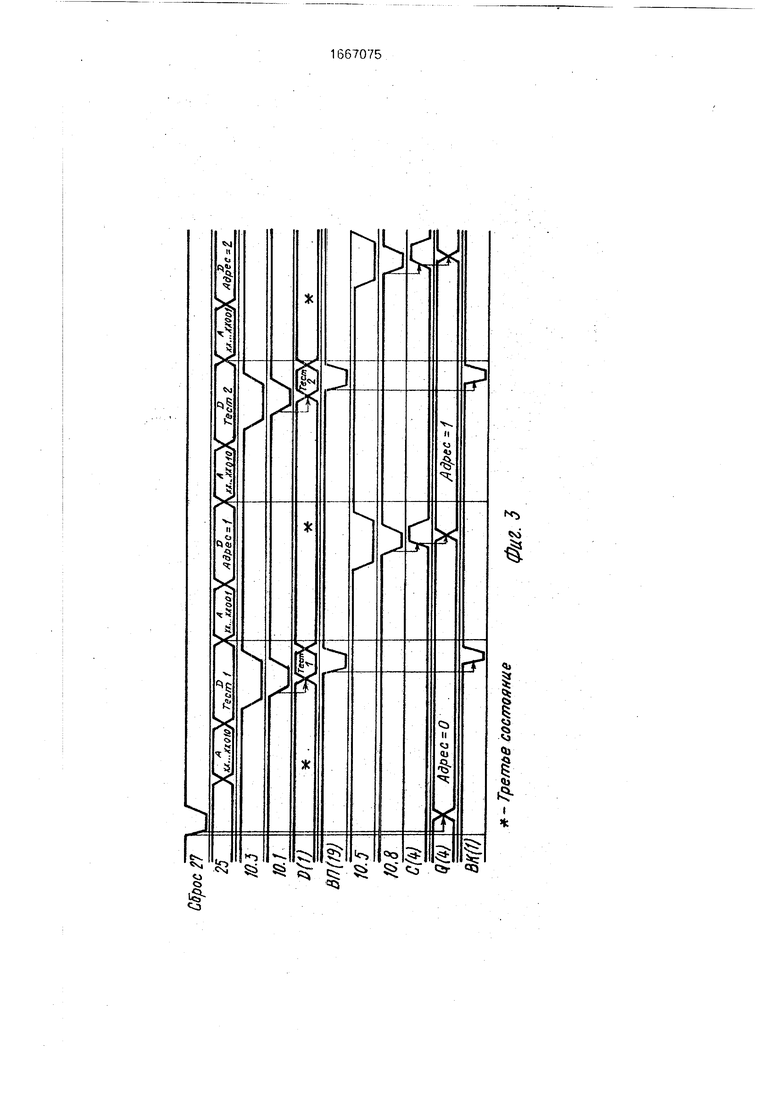

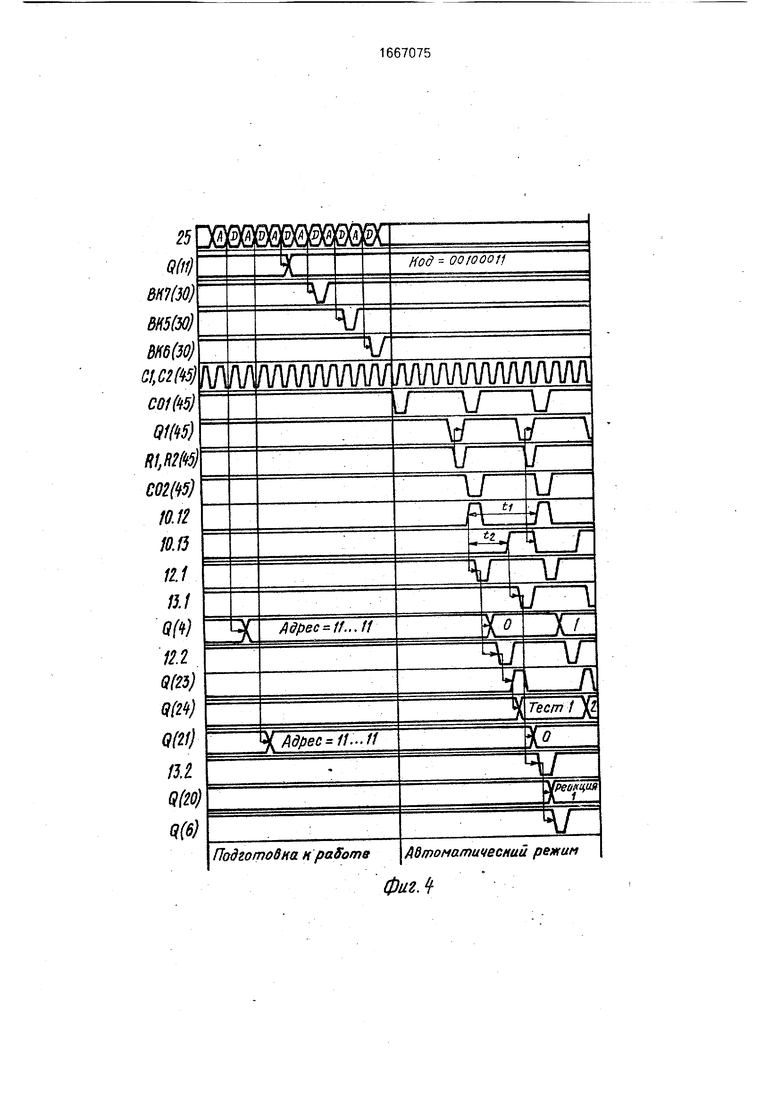

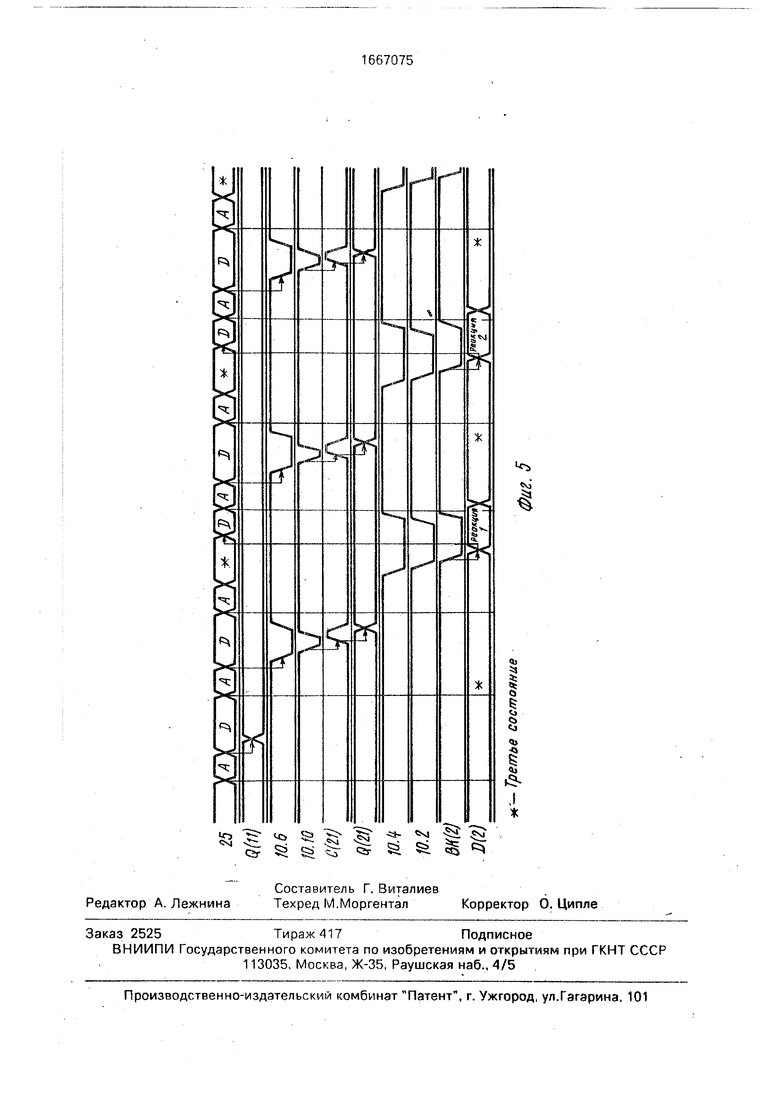

На фиг.1 приведена функциональная схема устройства для тестового контроля и диагностики цифровых модулей; на фиг.2 функциональная схема блока управления; на фиг.З - временные диаграммы работы устройства при записи тестовой информации в блок памяти тестов на фиг.4 - временные диаграммы работа устройства при автоматической генерации тестовых воздействий и приеме ответных реакций; на фиг.5 - временные диаграммы работы устройства при считывании информации из блока памяти реакций.

Устройство (фиг.1) содержит блок 1 памяти тестов, блок 2 памяти реакций, контролируемый цифровой модуль 3. первый счетчик 4 адреса, два элемента И 5 и 6. первый элемент ИЛИ 7, генератор 8 импульсов, делитель 9 частоты, блок 10 управления. регистр 11 режима, два регистра 12 и 13 сдвига, два элемента И-ИЛИ-НЕ 14 и 15, два

Os

О

3

vj СЛ

элемента И-НЕ 16 и 17, три приемопередатчика 18-20, второй счетчик 21 адреса, второй элемент ИЛИ 22, элемент НЕ 23, регистр 24 данных и имеет информационный вход-выход 25 адреса данных, вход 26 режима, вход 27 начальной установки Сброс, два тактовых входа 28 и 29 подачи внешних тактовых сигналов.

Блок 10 управления (фиг.2) содержит селектор 30 адреса, два регистра сдвига 31 и 32, три элемента НЕ 33-35, два элемента И 36 и 37, пять элементов ИЛИ 38-42, два элемента ИЛИ-НЕ 43 и 44, двухканальный программируемый таймер 45 и имеет шину 46 установки адреса.

Блок 1 памяти тестов предназначен для записи, хранения и формирования тестовой последовательности. Блок 2 памяти реакций служит для записи, хранения и считывания результатов контроля. Счетчики 4 и 21 адреса предназначены для формирования адресов блоков памяти 1 и 2 соответственно. Элементы И 5 и 6 служат для формирования сигналов разрешения обращения блоков 1 и 2 соответственно. Элементы ИЛИ 7 и 22 предназначены для формирования сигналов выборки блоков 1 и 2 соответственно в режиме записи. Генератор 8 импульсов служит для выдачи тактовых импульсов на делитель 9. Делитель 9 предназначен для формирования тактовых импульсов 9.1 и 9.2, синхронизирующих работу всего устройства.

Блок 10 управления служит для выработки сигналов, управляющих работой составных частей устройства. На выходах 10.1 и 10.2 формируются сигналы записи и считывания соответственно для указания направления передачи информации приемопередатчиками 18 и 19 формирования сигналов разрешения обращения блоков 1 и 2 режиме -записи. На выходах 10.3-10.6 формируются сигналы выборки приемопередатчиков 18 и 19 и счетчиков 4 и 21 адреса соответственно. На выходе 10.7 (выход элемента ИЛИ-НЕ 44) формируется строб записи информации в регистр 11. На выходах 10.8 и 10.10 (выходы элементов ИЛИ 39 и 41) формируются стробы записи информации в счетчики 4 и 21 адреса соответственно на выходах 10.9 и 10.11 (выходы элементов ИЛИ 40 и 42) формируются сигналы разрешения обращения блоков 1 и 2 соответственно в режиме чтения. На выходе 10.12 (выход элемента И 37) формируется сигнал, задающий частоту подачи тестовых воздействий на блок 1 при реализации варианта работы с таймером 45 режима автоматической генерации тестовых воздействий и приема ответных реакций.

На выходе 10.13 (выход элемента НЕ 35) формируется сигнал с той же частотой, что и на выходе 10.12, но задержанный относительно него и служащий для задания момен- тов съема диагностической информации блоком 2 при реализации варианта работы с таймером 45 режима автоматической генерации тестовых воздействий и приема ответных реакций.

Регистры 12 и 13 служат для формирования в соответствии с временными диаграммами обращения к блокам 1 и 2 следующих задержанных друг относительно друга групп сигналов:

5 увеличения на 1 содержимого счетчиков 4 и 21 соответственно (сигналы 12,1 и 13.1); разрешения обращения блоков 1 и 2 (сигналы 12.2 и 13.3 соответственно);

0 записи информации в регистр 24 и приема информации из приемопередатчика 20 с тремя устойчивыми состояниями на выходе (сигналы 12.3 и 13.2 соответственно). Логические элементы И-ИЛИ-НЕ 14 и 15

5 предназначены для формирования сигналов управления регистрами 12 и 13 сдвига в зависимости от режима работы. Указанные сигналы могут формироваться

из сигнала с максимальной частотой ра0 боты блоков памяти, снимаемого с выхода 9.2 делителя 9 частоты при установленных разрядах 11.2 и 11.6 регистра 11 режима соответственно;

из программируемых по частоте и вза5 имной задержке сигналов, снимаемых с выходов 10.12 и 10.13 блока 10 при установленных разрядах 11.3 и 11.7 регистра 11 режима соответственно;

из внешних по отношению к устройству

0 контроля сигналов 28 и Г:9 при установленных разрядах 11.4 и 11.Г регистра 11 режима соответственно;

из программных стробов при обращении к регистру 11 режима и одновременной

5 передаче по шине 25 кода, содержащего Г в разрядах 5 и 13 соответственно.

Логические элементы И-НЕ 16 и Услужат для формирования стробов записи или сигналов увеличении на 1 содержимого

0 счетчиков 4 и 21 соответственно. Для организации автоматического режима, когда од- новременно происходят считывание информации из блока 1и запись информации в блок 2, необходимы раздельные шины

5 данных блоков памяти, С этой целью в устройстве используются приемопередатчики 18 и 19 стремя устойчивыми состояниями на выходе. Приемопередатчик 18 передает информацию из общей шины 25 в шину данных блока 1 при подаче сигнала выборки 10.3 приемопередатчика и сигнала записи 10.1

или лиз шины данных блока 1 в общую шину

25при подаче сигнала выборки 10.3 и сигнала считывания 10.2. Приемопередатчик 19 передает информацию из общей шины 25 в шину данных блока 2 при подаче сигнала выборки 10.4 и сигнала записи 10.1 или из шины данных блока 2 в общую шину 25 при подаче сигнала выборки 10.4 и сигнала записи 10.1. или из шины данных блока 2 в общую шину 25 при подаче сигнала выборки 10.4 и сигнала считывания 10.2. Приемопередатчик 20 необходим для исключения вли- яния информации, снимаемой с контролируемого модуля 3, на информацию, передаваемую на шину данных блока 2 при процессе ее записи во внешнее устройство или считывания из него. Прошедшая через приемопередатчики 18, 19 и 20 информация сопровождается соответствующими сигналами Выполнено (ВП).

Регистр 24 данных служит для хранения тестовой информации, считанной из блока 1 и поступающей на контролируемый модуль 3. Двунаправленная шина 25 (адреса данных) предназначена для связи устройства для тестового контроля и диагностики - устройства контроля - с внешними устройствами, например с микроЭВМ, а также для связи составных частей устройства между собой. По шине 25 могут передаваться как адреса, так и данные, при этом передача адреса сопровождается стробом адреса, передающимся по шине 26 и поступающим на блок 10. Кроме указанного сигнала, по шине

26могут передаваться

сигнал записи при выполнении операции записи из внешнего устройства в устройство контроля;

сигнал чтения при выполнении операции чтения из устройства контроля во внешнее устройство;

сигнал ответа, передающийся из устройства контроля во внешнее устройство при завершении операции обмена с внешним устройством.

Шина 27 начальной установки Сброс служит для подачи сигнала, устанавливающего в исходное состояние счетчики 4 и 21, регистр 11 и таймер 45.

Шины 28 и 29 подачи внешних сигналов предназначены для реализации одного из вариантов запуска блоков 1 и 2 путем подачи по указанным шинам сигналов с требуемой частотой и задержкой считывания,

Шина 46 адреса, в простейшем случае выполненная в виде набора перемычек, соединенных определенным образом с шинами О и 1, присоединенная к входам программирования адреса селектора 30 адреса (А), предназначена для установки кода,

соответствующего старшим разрядам адреса устройства контроля, при совпадении адреса, приходящего из внешнего устройства, с установленным на шине 46 адресом, и в

зависимости от сигналов на шине 26 (Запись или Чтение) селектор 30 адреса вырабатывает сигналы записи (ЗП) или чтения (ЧТ), передающиеся низким уровнем, а в зависимости от младших разрядов поступающего адреса формирует сигнал выборки на

0 одном из восьми информационных выходов в соответствии с таблицей (выбранному выходу соответствует О в соответствующей графе таблицы).

Например, пусть внешним устройст5 вом устанавливается двоичный адрес ХХ...ХООО (где XX...XX соответствует разрядам, установленным на шине 46, и по шине 26 подается сигнал записи, при этом появляется импульс выборки на выходе ВКО и

0 сигнал записи на выходе ЗП селектора 30. В результате данные из шины 25 импульсом 10.7 с выхода элемента 44 запишутся в регстр 11. По завершении цикла записи или чтения устройство контроля должно изве5 стить об этом внешнее устройство. Для этого используется регистр 31. В зависимости от быстродействия используемых в устройстве контроля элементов с выхода соответствующего разряда регистра 31 на вход

0 готовности селектора 30 (ГОТ) поступает сигнал, свидетельствующий о завершении цикла записи или чтения. Получив сигнал готовности, селектор 30 устанавливает на шине 26 сигнал овета, означающий для

5 внешнего устройства окончание цикла обмена с устройством контроля.

Двухканальный программируемый таймер 45 предназначен для формирования программируемых по частоте и задержан0 ных друг относительно друга сигналов управления блоками 1 и 2, при этом каналы организованы на основе двоичных счетчиков. Первый счетчик может работать в режиме программируемого интервального

5 таймера и в режиме программируемого делителя частоты, а второй счетчик - в режиме программируемого интервального таймера. Оба счетчика могут запускаться по синхров0 ходам (С1. С2) или входам С01, С02) пуска. Запись кодов временных интервалов в оба счетчика происходит по сигналам записи ЗП и выбора каналов ВК5, В Кб соответственно, поступающим из селектора 30. Для выбора

5 режима работы таймера используется регистр состояний, запись в который происходит при поступлении из селектора 30 сигналов записи ЗП и выбора состояния ВК7. С первого и второго выходов регистра 32 снимаются сигналы, которые служат для

формирования на логических элементах 33 и 38 импульсов сброса выходных сигналов таймера 45, а также импульсов запуска каналов счета на логических элементах 37, 43 и 34. Элемент И 36 служит для формирования сигналов Пуск, поступающего через элемент ИЛИ-НЕ 43 на управпяющий вход таймера 45 при обращении по адресу регистра tl и установке Г в шестом разряде шины 25.

Устройство может работать в следующих режимах:

1.Запись тестовой информации из внешнего устройства в блок 1 и запись нулевой информации в блок 2;

2.Автоматическая генерация тестовых воздействий и прием ответных реакций;

2.1.С одновременной выдачей и приемом информации и максимальной частотой работы блоков памяти (9.2):

2.2.С частотой и задержкой считывания, зависящими от поступлет по шинам 28 и 29 внешних по отношению к устройству сигналов;

2.3.С пересылкой информации по приходу программного строба, появляющегося при достижении заданной комбинации значения сигналов;

2.4.С возможностью программирования в широких пределах и с малой дискрет- ностью частоты генерируемых и принимаемых цифровых последовательностей и задержки считывания (при использовании таймера 45);

3.Чтение внешним устройством информации из блока 2 с целью дальнейшей обработки.

Рассмотрим работу устройства в первом режиме (см. временные диаграммы на фиг.З). На шине Сброс внешним устройством формируется сигнал, устанавливающий в нулевое состояние счетчики 4 и 21, регистр 11 и таймер 45. При этом сигналами с выходов 11.1 и 11.5 регистра 11 блоки 1 и 2 переводятся в режим Запись. Внешним устройством по адресду ХХ...ХХ010 подается первое тестовое слово. При этом селектором 30 формируются сигналы записи и выборки (выходы 10.1 и 10.3 блока управления), происходит передача слова из шины 25 через приемопередатчик 18 на шину блока 1. На адресных входах блока 1 установлен нулевой код. Поэтому информация записывается в блок 1 по нулевому адресу сигналом разрешения обращения ВК, который формируется на логических элементах 5 и 7 из сигнала Выполнено (ВП), появляющегося на выходе приемопередатчика 18 одновременно с информацией. Затем по адресу ХХ...ХХ001, соответствующему выбору счетчика 4, подается код адреса 00...01, записываемый в счетчик по сигналу выборки 10.5 и стробу записи 10,8, прошедшему через элемент 16. По адресу ХХ...ХХ010 подается второе тестовое слово, которое заносится в блок 1 по установленному адресу 00...01, аналогичным образом происходит запись тестовой информации в остальные ячейки блока 1. При занесении нулевой информа0 ции в блок 2 из внешнего устройства подается информация по адресу ХХ...ХХ10. При этом на выходе ВК4 селектора 30 появляется сигнал выборки приемопередатчика 19 (выход 10.4 блока управления) и формирует5 ся сигнал записи 10.1. Сигнал разрешения обращения к памяти формируется логическими элементами 22 и 6, запись очередного адреса в счетичк 21 происходит по стробу записи 10.10, прошедшему через элемент

0 17 при обращении по адредсу ХХ...ХХ011, перед началом второго режима работы устанавливаются начальные адреса в счетчиках 4 и 21. Если первое тестовое слово записано по нулевому адресу блока 1 и первая ответ5 ная реакция должна фиксироваться по нулевому адресу блока 2, то в счетчиках 4 и 21 устанавливаются адреса 11...11. Это связано с тем, что перед каждым обращением к блокам памяти в автоматическом режиме

0 происходит увеличение содержимого счетчика адреса на 1 и, следовательно, перед первым обращением в счетчиках 4 и 21 будут установлены требуемые нулевые адреса. Во втором режиме работы возможны

5 различные варианты запуска блоков 1 и 2 (режимы 2.1...2.4). Выбор варианта осуществляется в зависимости от записанного по адресу ХХ...ХХООО в регистр 11 кода. Запись кода происходит перед началом работы во

0 втором режиме по формируемому блоком 10 стробу 10.7, записывающему поступающую по разрядам 25.12 5 4, 25.925.12 информацию, причем указанным разрядам шины 25 соответствуют выходы регистра ре5 жима 11.111.4, 11.511.8. При записи в

регистр 11 кода 0010 0011 будет установлен режим 2.1, а при записи кода 1000 1001 - режим 2.2. В режиме.2.3 реализуется асинхронный способ формирования сигналов

0 управления блоками 1 и 2, при котором указанные сигналы формируются из программных стробов при обращении к регистру 11 и установке 1 в разрядах 5 и 13 шины 25 соответственно. Программные стробы уста5 навливаются с помощью внешнего устройства, которое анализирует диагностическую информацию и по достижении заданной комбинации сигналов или через определенное вревмя программно формирует указанные стробы. Возможны различные

сочетания сигналов управления блоками 1 и 2. Например, при записи в регистр 11 кода 0100 0011 будут установлены режимы считывания блока 1 и записи блока 2, а сигналы управления для блока 1 на выходе элемента 14 будут формироваться из сигнала с максимальной частотой работы блока памяти, снимаемого с выхода 9,2 делителя 9. Сигналы управления для блока 2 на выходе элемента 15 будут формироваться из программируемого по частоте сигнала, снимаемого с выхода 10.13 блока 10 управления.

Рассмотрим подробно формирование сигналов управления при записи в регистр 11 кода 0100 0101 (см. временные диаграммы на фиг.А). Б этом случае перед этапом генерации тестовых воздействий и приема ответных реакций, т.е. перед переходом в режим 2.4, должен быть выполнен этап про- граммирования таймера 45. Для выборки режима работы счетчиков, входящих в состав таймера 45, в регистр состояний таймера записывается код состояния, означающий, что оба счетчика будут рабо- тать в режиме программируемого интервального таймера, а их запуск будет происходить поуправляющим входам С01 и С 02 соответственно. Затем в счетчики записываются коды временных интервалов. При этом в первый счетчик записывается код частоты сигналов управления блоками 1 и 2, а во второй счетчик - код взаимной задержки между указанными сигналами. Код, записываемый во второй счетчик, должен быть не больше кода, записываемого в первый счетчик. По завершении этапа программирования таймер 45 начинает работу по сигналу Пуск, поступающему на управляющий вход С01. По указанному сиг- налу разрешается счет импульсов, поступающих на вход С1 таймера 45 . По достижении равенства числа прошедших импульсов с предварительно установленным в первом счетчике кодом на выходе Q1 таймера 45 появляются импульсы, запускающие регистр 32, сигналы с выходов которого используются для выработки циклических импульсов сброса выходных сигналов тайм- ра элементами 33 и 38 и циклических им- пульсов запуска счетчиков таймера элементами 37, 43 и 34. В результате импульсы, появляющиеся на выходе Q1 таймера 45, а следовательно и на выходе 10.12 блока 10 следу ют с частотой fi 1/ti COOT- ветствующей записанному в первом счетчике коду. А импульсы на выходе Q2 таймера, а следовательно, и на выходе 10.13 блока 10 следуют с такой же частотой, но задержаны относительно указанных на время t2. соответствующее записанному во втором счетчике коду 1. Сформированные одним из возможных способов сигналы управления с выходов логических элементов 14 и 15 запускают регистры 12 и 13 соответственно. В зависимости от быстродействия элементов, составляющих блок памяти, с выходов соответствующих разрядов регистров 12 и 13 снимаются сигналы управления 12.1,..,,12.3

и 13.113.3 соответственно. По первым

импульсам на выходах 12.1 и 13.1 непосредственно начинается автоматический режим генерации тестов и приема ответных реакций: содержимое счетчиков 4 и 21 увеличивается на 1 и становится равным коду 00...00. На вход разрешения обращения блока 1 подается сигнал 12.2 и через время, определяемое задержками элементов блока памяти, на его выходе появляется тестовая информация, записываемая в регистр 24 по сигналу записи 12.3. Тестовая информация с выходов регистра 24 поступает на контролируемый модуль. В зависимости от кода, записанного в регистре 11. ответная реакция контролируемого модуля 3 принимается приемопередатчиком 20 по сигналу приема 13.2 одновременно с подачей тестовых воздействий или с программируемой задержкой.

Информация с выхода приемопередатчика 20 записывается в блок 2 по сигналу разрешения обращения 13.3 блока памяти, прошедшему через элемент 6. По вторым импульсам на выходах 12.1 и 13.1 увеличивается на 1 содержимое счетчиков 4 и 21 и процесс генерации тестов и приема реакций продолжается аналогичным образом. При асинхронном способе формирования сигналов управления блоками 1 и 2 указанные сигналы формируются таким же образом, однако при этом появляется возможность организации условных запусков. Например, считывание информации из блока 1 может быть выполнено с программируемой задержкой при условии записи в блок 2 определенного кода. При этом анализ записанной информации и принятие решения о считывании осуществляются внешним устройством.

Во время автоматического режима возможен переход на другую комбинацию сигналов запуска блоков памяти путем записи соответствующего кода в регистр 11 или прерывание автоматического режима путем записи нулевого кода в регистр 11.

В третьем режиме происходит чтение внешним устройством информации из блока 2. Для этого в регистр 11 записывается код 0001 0000, переводящий блок 2 в режим чтения, в счетчике 21 устанавливается нулевой адрес. Внешним устройством устанавливается команда считывания по адресу ХХ...ХХ100, при этом блоком Ю ормируют- ся сигналы 10.2, 10.4, 10.11. По сигналу 10.11, прошедшему через элемент 6, происходит считывание информации из блока 2, по сигналам считывания 10.2 и выбора приемопередатчика 19 (сигнал 104) информация передается с шины данных блока 2 через приемопередатчик 19 на шину 25. Далее в счетчике 21 устанавливается следующий адрес и процесс чтения информации продолжается аналогичным образом. В каждом цикле чтения информация по шине 25 поступает во внешнее устройство, где накапливается, затем обрабатывается и поступает на средства отображения информации (дисплей, печатающее устройство и т.п.).

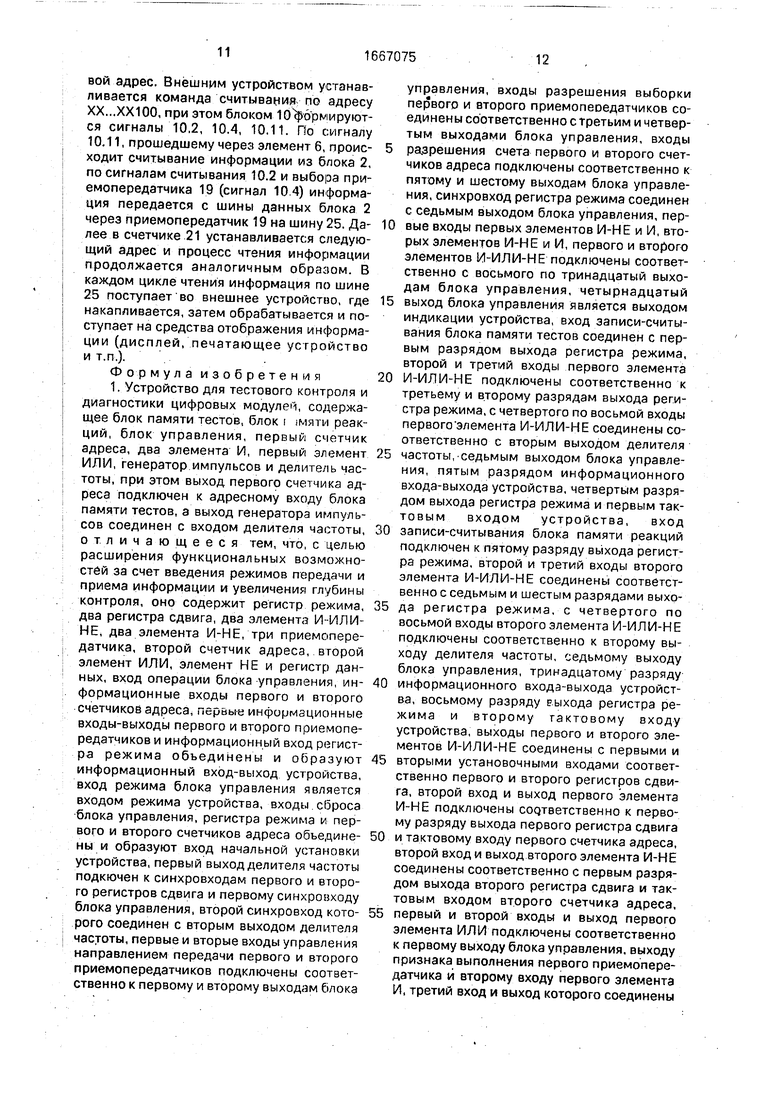

Формула изобретения 1. Устройство для тестового контроля и диагностики цифровых модулрй, содержащее блок памяти тестов, блок г ,мяти реакций, блок управления, первый счетчик адреса, два элемента И, первый элемент ИЛИ, генератор импульсов и делитель частоты, при этом выход первого счетчика адреса подключен к адресному входу блока памяти тестов, а выход генератора импульсов соединен с входом делителя частоты, отличающееся тем, что, с целью расширения функциональных возможностей за счет введения режимов передачи и приема информации и увеличения глубины контроля, оно содержит регистр режима, два регистра сдвига, два элемента И-ИЛИ- НЕ, два элемента И-НЕ, три приемопередатчика, второй счетчик адреса, второй элемент ИЛИ, элемент НЕ и регистр данных, вход операции блока управления, информационные входы первого и второго счетчиков адреса, первые информационные входы-выходы первого и второго приемопередатчиков и информационный вход регистра режима обьединены и образуют информационный вход-выход устройства, вход режима блока управления является входом режима устройства, входы сброса блока управления, регистра режима и первого и второго счетчиков адреса обьединены и образуют вход начальной установки устройства, первый выход делителя частоты подкючен к синхровходам первого и второго регистров сдвига и первому синхровходу блока управления, второй синхровход которого соединен с вторым выходом делителя частоты, первые и вторые входы управления направлением передачи первого и второго приемопередатчиков подключены соответственно к первому и второму выходам блока

управления, входы разрешения выборки первого и второго приемопеоедатчиков соединены соответственно с третьим и четвертым выходами блока управления, входы

разрешения счета первого и второго счетчиков адреса подключены соответственно к пятому и шестому выходам блока управления, синхровход регистра режима соединен с седьмым выходом блока управления, пер0 вые входы первых элементов И-НЕ и И, вторых элементов И-НЕ и И, первого и второго элементов И-ИЛИ-НЕ подключены соответственно с восьмого по тринадцатый выходам блока управления, четырнадцатый

5 выход блока управления является выходом индикации устройства, вход записи-считывания блока памяти тестов соединен с первым разрядом выхода регистра режима, второй и третий входы первого элемента

0 И-ИЛИ-НЕ подключены соответственно к третьему и второму разрядам выхода регистра режима, с четвертого по восьмой входы первого элемента И-ИЛИ-НЕ соединены соответственно с вторым выходом делителя

5 частоты, седьмым выходом блока управления, пятым разрядом информационного входа-выхода устройства, четвертым разрядом выхода регистра режима и первым так- товым входом устройства, вход

0 записи-считывания блока памяти реакций подключен к пятому разряду выхода регистра режима, второй и третий входы второго элемента И-ИЛИ-НЕ соединены соответственное седьмым и шестым разрядами выхо5 да регистра режима, с четвертого по восьмой входы второго элемента И-ИЛИ-НЕ подключены соответственно к второму выходу делителя частоты, седьмому выходу блока управления, тринадцатому разряду

0 информационного входа-выхода устройства, восьмому разряду еыхода регистра режима и второму тактовому входу устройства, выходы первого и второго элементов И-ИЛИ-НЕ соединены с первыми и

5 вторыми установочными входами соответственно первого и второго регистров сдвига, второй вход и выход первого элемента И-НЕ подключены соответственно к первому разряду выхода первого регистра сдвига

0 и тактовому входу первого счетчика адреса, второй вход и выход второго элемента И-НЕ соединены соответственно с первым разрядом выхода второго регистра сдвига и тактовым входом второго счетчика адреса,

5 первый и второй входы и выход первого элемента ИЛИ подключены соответственно к первому выходу блока управления, выходу признака выполнения первого приемопередатчика и второму входу первого элемента И, третий вход и выход которого соединены

соответственно с вторым разрядом выхода первого регистра сдвига и входом разрешения обращения блока памяти тестов, информационный вход-выход которого подключен к второму информационному входу-выходу первого приемопередатчика и информационному входу регистра данных, вход и выход элемента НЕ соединены соответственно с третьим разрядом выхода первого регис гра сдвига и синхровходом регистра данных, выход которого является выходом устройства для подключения к входу контролируемого цифрового модуля, первый и второй входы и выход второго элемента ИЛИ подключены соответственно к первому выходу блока управления, выходу признака выполнения второго приемопередатчика и второму входу второго элемента И, управляющий вход и выход третьего приемопередатчика соединены соответственно с вторым разрядом выхода второго регистра сдвига и вторым информационным входом- выходом второго приемопередатчика, вход третьего приемопередатчика является входом устройства для подключения к выходу контролируемого цифрового модуля, третий вход и выход второго элемента И подключены соответственно к третьему разряду выхода второго регистра сдвига и входу разрешения обращения блока памяти реакций, адресный вход и информационный вход-выход которого соединены соответственно с выходом второго счетчика адреса и вторым информационным входом-выходом второго приемопередатчика.

2. Устройство поп.1,отличающее- с я тем, что блок управления содержит селектор адреса, вда регистра сдвига, три элемента НЕ, два элемента И, пять элементов ИЛИ, два элемента ИЛИ-НЕ и двухканаль- ный программируемый таймер, информационный вход которого соединен с входом операции блока, управляющий вход, первый и второй информационные входы и вход готовности селектора адреса подключены соответственно к входу режима блока ; входу операции блока, шине установки адреса блока и выходу первого регистра сдвига, выход записи и выход чтения селектора адреса соединены соответственно с входами записи и чтения двухканального программируемого таймера, первым и вторым установочными входами первого регистра сдвига и являются первым и вторым выходами блока, синхровход первого регистра сдвига является первым сичхровходом блока, синхровход второго регистра сдвига под- ключен к второму синхровходу блока, который, кроме того, соединен с первым и вторым синхровходами двухканального

программируемого таймера, первый информационный выход которого подключен к первому и второму установочным входам второго регистра сдвига, первый и второй

входы и выход первого элемента ИЛИ-НЕ соединены соответственно с выходами первого и второго элементов И и первым входомпускадвухканальногопрограммируемого таймера, первый и вто0 рой входы первого элемента И подключены соответственно к шестому разряду входа опепации блока и выходу второго элемента ИЛИ-НЕ, первый и второй входы второго элемента И соединены соответственно с

5 первым выходом второго регистра сдвига и выходом первого элемента НЕ, вход которого подключен к второму выходу второго регистра сдвига, первый и второй входы и выход первого элемента ИЛИ соединены со0 ответст венно с первым выходом первого регистра сдвига, выходом первого элемента НЕ и входами сброса первого и второго каналов двухканального программируемого таймера, вход общего сброса которого явля5 ется входом сброса блока, выход второго элемента И является двенадцатым выходом блока и подключен к входу второго элемента НЕ, выход которого соединен с вторым входом пуска двухканального программируе0 мого таймера, второй информационный выход которого подключен к входу третьего элемента НЕ, выход которого является тринадцатым выходом блока, выход признака адреса селектора адреса является четыр5 нлдцатым выходом блока, первый и второй входы и выход второго элемента ИЛИ-НЕ соединены соответственно с первым информационным выходом и выходом записи селектора адреса и седьмым выходом блока,

0 первый и второй входы и выход второго элемента ИЛИ подключены соответственно к второму информационному выходу и выходу записи селектора адреса и восьмому выходу блока, второй информационный выход се5 лектора адреса является пятым выходом блока, первый и второй входы и выход третьего элемента ИЛИ соединены соответственно с третьим информационным выходом и выходом чтения селектора адреса и девя0 тым выходом блока, третий информационный выход селектора адреса является третьим выходом блока, первый и второй входы и выход четвертого элемента ИЛИ подключены соответственно к четвертому

5 информационному выходу и выходу записи селектора адреса и десятому выходу блока, четвертый информационный выход селектора адреса является шестым выходом блока, первый и второй входы и выход пятого элемента ИЛИ соединены соответственно с пятмм информационным выходом и выходом чтения селектора адреса и одиннадцатым выходом блока, пятый информационный выход селектора адреса является четвертым выходом блока, а с шестого по восьмой ин-

формационные выходы селектора адреса подключены соответственно к входам выбора первого и второго каналов и входу выборасостояниядвухканальногопрограммируемого таймера.

Фиг. 2

3®0®00(

v

Hod OOfQOOH

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Система для контроля больших интегральных схем | 1988 |

|

SU1647569A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для сопряжения ЦВМ с линиями связи | 1986 |

|

SU1462328A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для формирования тестов памяти | 1989 |

|

SU1711235A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностики цифровых модулей различного назначения (в управляющих микропроцессорных системах, контроллерах и т. п.). Целью изобретения является расширение функциональных возможностей за счет введения режимов передачи и приема информации и увеличения глубины контроля. С этой целью в устройство, содержащее блок памяти тестов, блок памяти реакций, блок управления, первый счетчик адреса, два элемента И, первый элемент ИЛИ, генератор импульсов и делитель частоты, введены регистр режима, два регистра сдвига, два элемента И - ИЛИ - НЕ, два элемента И - НЕ, три приемопередатчика, второй счетчик адреса, второй элемент ИЛИ, элемент НЕ и регистр данных. 5 ил.

Адрес //...//

Ч( Адрес f)..Т/Г

Подготовка н работе

/W AA/WWIAA/IA

У

V

и

и

t/

л.

п г

и

и

Л

о I X /

ЛГ

Л

У

Гее/77 Г$

Автоматический режим

фигЛ

€

ь

ч

$

о

В з

ъ

.

,1

5

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1988-11-04—Подача