(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1280454A1 |

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Запоминающее устройство | 1980 |

|

SU911623A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Устройство автоматического контроля веса материала в бункерах | 1985 |

|

SU1255870A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повышение достоверности работы. Запоминающее устройство содержит счетчик, элементы И, элементы ИЛИ, триггеры, элементы задержки, инверторы, регистр сдвига, схемы сравнения, дополнительные регистры, сумматор, регистр адреса, шину тактовых импульсов, шину начальной установки, шину записи, адресную шину, вход задания тестового режима, первый и второй выходы устройства, сигнальный выход устройства. В устройстве появляется возможность проконтролировать всю хранящуюся в регистре сдвига информацию, а также процесс выполнения операции сдвига. 2 ил.

Изобретение относится к автоматике и вычислительной технике и касается усовершенствования устройства по авт. св. № 1280454.

Цель изобретения - повышение достоверности работы.

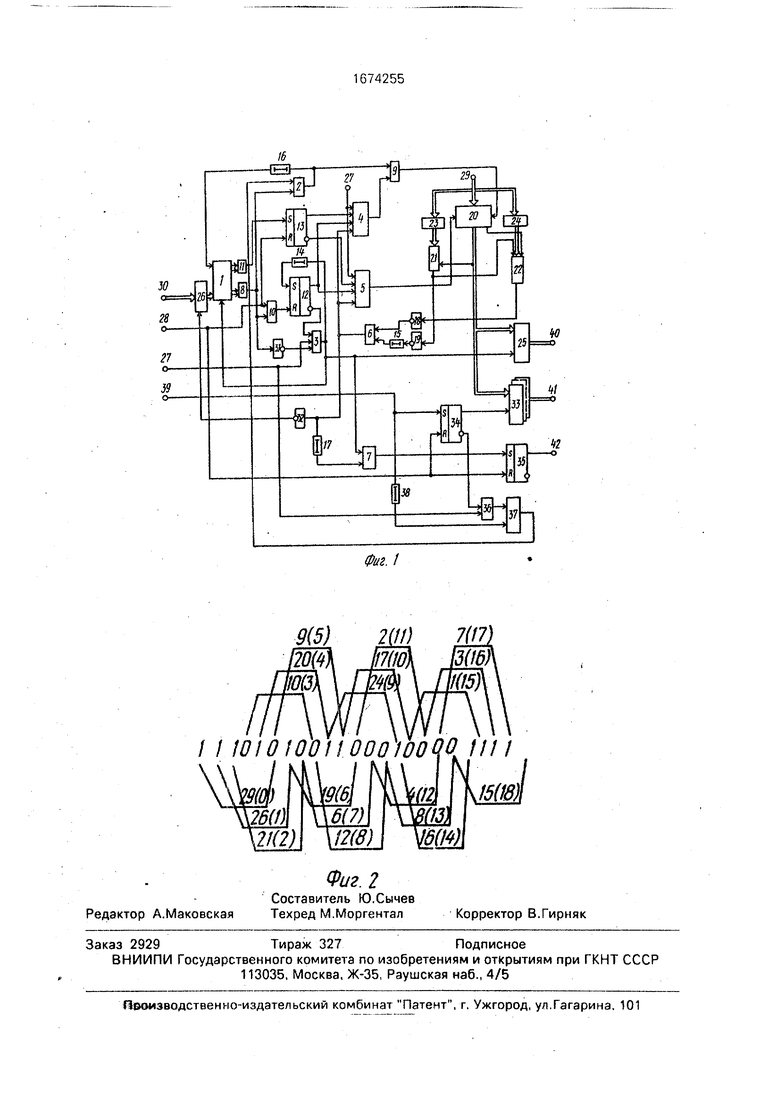

На фиг.1 приведена функциональная схема запоминающего устройства; на фиг.2 - пример сжатой последовательности.

На схеме (фиг.1) обозначены: счетчик 1, элементы И 2-7, элементы ИЛИ 8-11. триггеры 12-13, элементы 14-17 задержки, инверторы 18-19. регистр 20 сдвига, схемы 21-22 сравнения, дополнительные регистры 23-24, сумматор 25, регистр 26 адреса, шина 27 тактовых импульсов, шина 28 начальной установки, шина 29 записи, адресная шина 30, инверторы 31-32, группа элементов И 33, триггеры 34-35, элемент И 36, элемент ИЛИ 37, элемент 38 задержки, вход 39 задания тестового режима, первый

40 и второй 41 выходы устройства, сигнальный выход 42 устройства.

Устройство может работать в двух режимах - автоматическом и тестовом. В автоматическом режиме предлагаемое устройство работает следующим образом.

По сигналу Начальная установка по шине 28 устанавливаются в нулевое состояние триггеры 13, 12 и триггеры 34,35. Адрес числа записывается в регистр 26 и поступает на счетчик 1. Единичные выходы всех разрядов счетчика Т подключены к входам элемента ИЛИ 8, а разряды с К-го по самый старший - к входам элемента ИЛИ 11. Единичный сигнал на выходе элемента ИЛИ 11 появится тогда, когда содержимое счетчика 1 будет больше 1/2, а на выходе элемента ИЛИ 8 - когда адрес в счетчике 1 не равен нулю. Сигнал с элемента ИЛИ 11 переводит триггер 13 в единичное состояние, а единичный сигнал с выхода элемента ИЛИ 8 через

О

ю

СП

ел

ю

элемент ИЛИ 10 подтверждает нулевое со- стояние триггера 12, открывает по одному входу элемент И 2 и поступает на инвертор 31, закрывая по одному из входов элемент И 3. Находящийся в нулевом состоянии триггер 34 единичным сигналом с нулевого выхода открывает по одному из входов элемент И 36. Тактовые импульсы с выхода 27 проходят через открытый элемент И 36, элемент ИЛИ 37 и через открытый элемент И 2, воздействуя на элемент И Л И 9 и элемент 16 задержки. По первому тактовому импульсу (ТИ), снимаемому с элемента ИЛИ 9, с одер- жимое регистра 20 сдвига сдвигается на один разряд влево (сдвиг по кольцу), а пер- вый ТИ, задержанный в элементе 16 задержки на время, равное времени срабатывания одного триггера регистра 20 сдвига, уменьшает содержимое счетчика 1 на единицу. В регистре 20 информация хранится в сжатом виде, заносится в него пек шине 29 записи. В качестве адреса числа используется его номер в сжатой последовательности. Так, например, в устройстве хранится сжатая последовательность из19следующихчисел:

1,2,3,4,6,7,8,9,10,12,16,17,19,20,21,24,26,15, 29{фиг.20). Упаковка чисел в сжатую последовательность осуществляется при помощи ЭВМ по специальной программе.

При занесении сжатой последователь- мости в сдвиговый регистр 20 одновременно в дополнительный регистр 23 записывается число, соответствующее нулевому адресу в последовательности (11101), а в регистр 24 - младшие разряды сжатой информации.

Пусть на счетчик 1 поступает адрес 01010, тогда после первого сдвига содержимое регистра 20 сдвига станет

1101010010001000011111

(сдвиги по кольцу в обе стороны), а содержимое счетчика - 01001. После первого сдвига на схеме 21 сравнения осуществляется сравнение содержимого старших разрядов (в нашем случае 11()10)ссодержимым регистра 23 - эти значения не равны. Следовательно, на выходе схемы 21 сравнения будет код нуля, а на выходе инвертора 19 - единицы. Однако элемент ы И 4 и 5 закрыты, так как триггер 12 находится в нулевом со- стоянии. Аналогичные действия происходят при поступлении на вход элемента И 36 до 10-го ТИ. Содержимое сдвигового регистра 20 сдвигается при этом на 10 разрядов влево и становится равным

10001000011111110101001, а содержимое счетчика 1 - нулю.

Это признак конца поиска нужной информации. Выдача найденного из сдвигового регистра 20 осуществляется следующим образом.

Нулевой сигнал с выхода элемента ИЛИ

8закрывает элемент И 2, прекращая дальнейший сдвиг последовательности в регистре 20 сдвига, и приводит к образованию единичного сигнала на выходе инвертора 31. Так как триггер 12 в нулевом состоянии, то по 11 -му ТИ на выходе элемента ИЗ образуется единичный сигнал, по которому осуществляется выдача найденного числа 10001 из пяти старших разрядов сдвигового регистра 20 на сумматор 25. Этот же сигнал с элемента И 3 через элемент 14 задержки устанавливает триггер 12 в единичное состояние. Этим самым дается разрешение на возврат сжатой последовательности в регистре 20 сдвига в исходное состояние. Для этой цели служат элементы И 4,5, инвертор 19, схема 21 сравнения и триггер 13. Триггер 13 указывает направление сдвига сжатой последовательности для возвращения ее в исходное состояние кратчайшим путем, В частности, если триггер 13 в нулевом состоянии, то ТИ проходят через элемент И 5 и сдвиг выполняется слева направо по кольцу; если триггер 13 в единичном состоянии, то ТИ поступают на сдвиговый регистр 20 через открытый элемент И 4, элемент ИЛИ

9и сдвиг осуществляется справа налево тоже по кольцу. В обоих случаях сдвиг продолжается до тех пор, пока в старших разрядах регистра 20 сдвига не окажется число с нулевым адресом. А так как такое же число хранится в регистре 23, то на выходе схемы 21 сравнения появится единичный сигнал, а на выходе инвертора 19 - код нуля. Совпадение старших разрядов последовательности и информации в регистре 23 свидетельствует о том, что сжатая информация возвращена в исходное состояние, и можно утверждать, что в старших разрядах переписана правильно. Проверка остальных разрядов последовательности осуществляется при помощи регистра 24 и схемы 22 сравнения. Единичный сигнал со схемы 21 сравнения разрешает работу схемы 22 сравнения. Если разряды совпадают, то на выходе схемы 22 сравнения появляется единичный сигнал, который через инвертор 18 поступает на вход элемента И 6, на второй вход через элемент 15 задержки подается код нуля. С выхода элемента И 6 выдается сигнал, который запрещает работу элементов И 4, 5, т.е. прекращает сдвиг сжатой последовательности в регистре 20 сдвига. Одновременно запрещающий сигнал через элемент 17 задержки поступает на второй вход элемента И 7, а с его выхода - на первый вход блока визуального контроля

сжатой информации, где подтверждает нулевое состояние триггера 35, которое индицируется, показывая верность информации в регистре 20. Кроме того, код нуля с выхода элемента И 6 через элемент НЕ 32 поступает на второй вход регистра 26 адреса, разрешая запись очередного адреса. Таким образом, регистр 26 обеспечивает временную синхронизацию работы элементов запоминающего устройства с работой системы, обеспечивающей выработку адреса и выдачу его в счетчик 1,

Как следствие искажения информации в регистре 20 сдвига может возникнуть ситуация, когда сравнения кодов в схемах 21 и 22 сравнения не произойдет, т.е. не выработаются единичные сигналы на выходах схем 21 и 22 сравнения. При этом высокий потенциал на втором входе элемента И 7 разрешает прохождение через него единичного сигнала с выхода элемента И 3 при нулевом адресе счетчика. Единичный сигнал поступает на вход триггера 35, устанавливая его в единичное состояние, которое индицируется на схеме индикации, показывая наличие ошибки в сжатой последовательности. Для определения этой ошибки служит тестовый режим устройства. Тестовый режим запускается синхроимпульсом, поступающим на вход 39. Этот единичный сигнал устанавливает триггер 34 в единичное состояние, тем самым закрывая элемент И 36. Одновременно с этим единичный сигнал с входа 39 поступает через элемент 38 задержки, служащий для задержки сигнала на время срабатывания триггера 34, на вход элемента ИЛИ 37 и с его выхода - на вход элемента И 2, а единичный сигнал с триггера 34 - на вход элементов И 33, подключая выход регистра 20 сдвига для визуального контроля с выхода 41.

С приходом импульса на вход элемента И 2 вновь осуществляется сдвиг кода в регистре 20.

По следующему синхроимпульсу последовательность, хранящаяся в сдвиговом регистре 20, сдвигается еще на один разряд и т.д. При этом содержимое регистра 20 индицируется, так как единичное состояниетриггера 34 открывает элементы И 33, на вторые входы которых поступают соответствующие им разряды регистра 20 сдвига.

Таким образом появляется возможность проконтролировать всю хранящуюся

в регистре 20 сдвига информацию, а также процесс выполнения операции сдвига. Формула изобретения Запоминающее устройство по авт. св. № 1280454, отличающееся тем, что, с

целью повышения достоверности в работе, в него введены группа элементов И, одни входы которой соединены с выходами регистра сдвига, выходы группы элементов И являются вторыми выходами устройства,

третий триггер, вход установки в единичное состояние которого соединен с входом пятого элемента задержки и является входом задания тестового режимэ устройства, прямой выход третьего триггера соединен с

другим входом группы элементов И, четвертый элемент задержки, вход которого соединен с выходом пятого элемента И, шестой элемент И, входы которого соединены соответственно с выходом второго элемента И и

четвертого элемента задержки, четвертый триггер, вход установки в единичное состояние которого соединен с выходом шестого элемента И, прямой выход четвертого триггера является сигнальным выходом устройства, седьмой элемент И, один вход которого соединен с тактирующим входом устройства, другой вход - с инверсным выходом третьего триггера, пятый элемент ИЛИ, входы которого соединены соответственно с выходами седьмого элемента И и пятого элемента задержки, выход пятого элемента ИЛИ соединен с другим входом первого элемента И.

/ 1 W10100110DOWOW ////

| Запоминающее устройство | 1985 |

|

SU1280454A1 |

Авторы

Даты

1991-08-30—Публикация

1989-07-26—Подача