(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Запоминающее устройство | 1985 |

|

SU1280454A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

| Запоминающее устройство | 1989 |

|

SU1674255A2 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство контроля веса материала в бункерах | 1980 |

|

SU972243A1 |

| Цифровой фазометр | 1988 |

|

SU1511706A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

I

Изобретение относится к вычислительной технике, а точнее к запоминающим устройствам, и может быть использовано для хранения информации в цифровой форме.

Известно запоминающее устройство для хранения цифровой информации, состоящее из сдвигового регистра, вход которого подключен к входному каскаду, а выход - к выходному каскаду устройства, каскада регенерации, вход которого соединен с выходным каскадом, а выход - с входным 1.

Однако такие запоминающие устройства имеют больщое количество оборудования, сложную схему и малую информационную емкость.

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство, которое содержит регистры сдвига, одни входы которых подключены к полусумматорам, а выходы - к выходной логической схеме, дополнительный «регистр сдвига, первый вход которого соединен с первой управляющей щиной и с одним из входов триггера, другой вход триггера подключен к выходу дополнительного регистра, элемент И, один вход которого соединен со второй управляющей щиной и вторым входом дополнительного регистра, другой вход схемы И подключен к выходу триггера, а выход элемента И - к другим входам основных регистров сдвига 2.

Известное запоминающее устройство имеет большое количество оборудования, в особенности регистров, и малую информационную емкость, так как каждый элемент памяти сдвиговых регистров хранит двоичную цифру только одного числа.

Цель изобретения. - повышение информационной емкости устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее регистр сдвига, выход которого соединен с одним из входов выходного блока, триггер управления, первый элемент И, щину тактовых импульсов, соединенную с первым входом первого элемента И, второй вход которого соединен с одним из выходов триггера управления, щину записи информации, соединенную со входом регистра хранения информации и с одним из входов регистра сдвига шину сброса и адресную щину, введены блок сравнения, два элемента задержки, второй и третий элементы И, три элемента ИЛИ,

два инвертора и счётчик, один из входов которого подключен к адресной шине, а другой вход - к выходу первого элемента задержки, выход счетчика соединен со входом первого элемента ИЛИ, выход которого подсоединен ко входу первого инвертора, к одному из входов второго элемента ИЛИ и к одному из входов второго элемента И, другой вход второго элемента ИЛИ соединен с шиной сброса, выход первого инвертора подключен к третьему входу первого элемента И, выход которого соединен с другим входом выходного блока и с входом второго элемента задержки, выход второго элемента ИЛИ подсоединен к одному из входов триггера управления, другой вход которого соединен с выходом второго элемента задержки, другой выход триггера управления подключен к первому входу третьего элемента И, второй вход которого соединен с выходом второго инвертора, вход второго инвертора подсоединен к выходу блока сравнения, один из входов которого соединен с выходом регистра сдвига, другой вход блока сравнения подключен к выходу регистра хранения информации, другой вход регистра сдвига соединен с выходом третьего элемента ИЛИ, один из входов которого подсоединен к выходу второго элемента И и ко входу первого элемента задержки, другой вход третьего элемента ИЛИ подключен к выходу третьего элемента И, третий вход третьего элемента И и другой вход второго элемента И соединены с шиной тактовых импульсов.

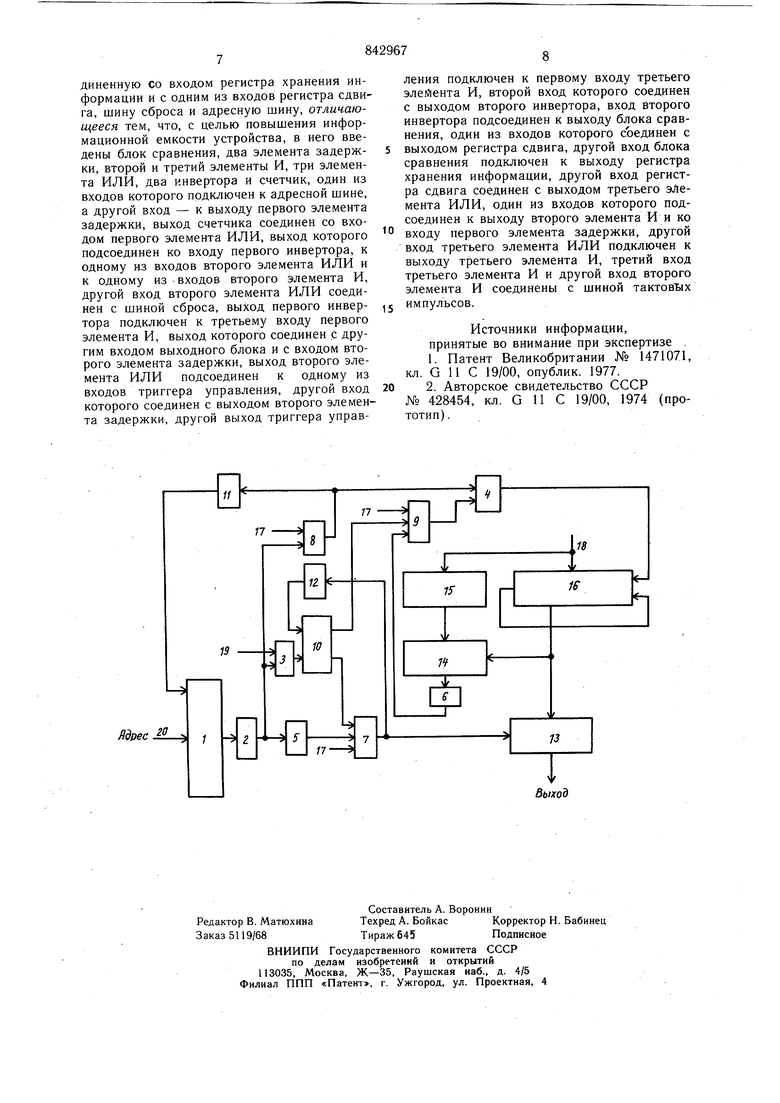

На чертеже изображена функциональная схема предлагаемого устройства.

Запоминаюш,ее устройство содержит счетчик 1, элементы ИЛИ 2-4, инверторы 5 и 6, элементы И 7-9, триггер 10 управления, элементы 11 и 12 задержки, выходной блок 13, блок 14 сравнения, регистр 15 хранения информации, регистр 16 сдвига, шину 17 тактовых импульсов, шину 18 записи информации, шину 19 сброса, адресную шину 20.

Устройство работает следующим образом.

Адресный сигнал поступает на счетчик 1. Перед началом работы триггер 10 по сигналу сброса (шина 19) устанавливается в нулевое состояние.

Если адрес в счетчике 1 не равен нулю, то на выходе элемента ИЛИ 2 появляется единичный сигнал, который через элемент ИЛИ 3 подтверждает нулевое состояние триггера 10, открывает по одному из входов элемента И 8 и после прохождения через инвертор 5 закрывает по одному из входов элемент И 7. Тактовые импульсы (ТИ) с шины 17 проходят через открытый элемент И 8, воздействуя на элемент ИЛИ 4 и элемент 11 задержки. В частности, первый тактовый импульс, снимаемый с выхода элемента 4, сдвигает содержимое регистра 16 на один разряд влево, а задержанный элементом 11 на время, равное времени срабатывания триггера регистра 16 сдвига, уменьшает содержимое счетчика 1 на единицу. В регистре 16 исходная информация хранится в сжатом виде. Например, если уст5 ройство хранит шестнадцать четырехразрядных чисел, то в регистре 16 записывается одна из следующих шестнадцати последовательностей:

С| 000111 1010110010; С2 000 110 101 1110010; Са 000111 101 1001010; С 4 000110111 1001010; Cj 000101 111001 1010; С 000111 100101 1010; C-f 000101 100111 1010; 5€« 0001100101111010;

Се 000101 1110100110; Cto 000100111 101 ОНО; С„ 000 100 111 1010110; 0,4 000101001 1110110; С« 000101 101001 1110; 0С,4 000110100101 1110;

Cis 000100110101 1110; Ci6 000101001 101 1110;. В общем случае количество К всевозможных неповторяющихся последовательностей, 5 которые могут быть получены при хранении п-разряднь1х чисел, определяется соотношением К 2 -л. В каждой вышеприведенной последовательности содержатся все шестнадцать четырехразрядных чисел. Предположим, что в регистр 16 по шине 18 записана первая последовательность GI. В последовательности Cj эти числа располагаются в следующем порядке: 1, 3, 7, 15, 14, 13, 10, 5, 11, 6, 12, 9, 2. Три последних числа 4, 8, О будут получены в процессе сдвига поJ следовательности С влево, т.е. в результате последовательного перемещения трех нулей из старших разрядов в младшие разряды последовательности. Одновременно с занесением сжатой последовательности в регистр 16 в регистр 15 записывается число, 0 соответствующее нулевому номеру в последовательности числом является 0001. Сжатые последовательности могут содержать не все п-разрядные числа (слова), если запоминающее устройство предназначено для хранения ограниченного числа слов. При хранении чисел в сжатом виде в качестве адреса числа используется его в последовательности. Нумерация чисел в последовательности С, ведется справа налево. Предположим, что на счетчик 1 поступает адрес (номер числа последоватальности) ОНО. Этому адресу в последовательности С соответствует число 1010. Следовательно, в результате действия первого тактового импульса последовательность С в регистре 16 сдвига сдвигается на один разряд влево (сдвиг по кольцу, т.е. выталкиваемый старший разряд занимает место младшего разряда) и имеет вид .

Cf 001 1110101100100, а содержимое счетчика I становится равным 0101. После сдвига в блоке 14 сравнения осуществляется сравнение содержимого п-старших разрядов регистра 16 сдвига (в нашем случае ООП) с содержимым регистра 15 (равным 0001). При равенстве значений блок 14 сравнения формирует единичный сигнал, а на выходе инвертора 6 - сигнал равный нулю, поэтому элемент И 9 по одному из входов будет закрыт. После 1-го сдвига эти значения неравны, на выходе инвертора 6-код 1, но элемент И 9 закрыт по 2-му входу, так как триггер 10 обнулен. Аналогичные действия осуществляются при поступлении на вход элемента И 8 (щина 17) второго, третьего и т.д. тактовых импульсов. После щестого тактового импульса исходная сжатая последовательность С в регистае 16 сдвигается на шесть разрядов влево Q 1010110010090111 (верхний индекс в С равный 6 показывает количество выполненных сдвигов). В п-старших разрядах регистра 16 оказывается искомое число 1010, ему соответствует номер (адрес) в исходной последовательности € равный ОНО, а содержимое счетчика 1 станет равным нулю. Нулевое содержимое счетчика 1 является признаком конца поиска нужного числа в регистре 16. Выдача найденного числа из запоминающего устройства осуществляется следующим образом. Нулевой сигнал с элемента ИЛИ 2 закрывает элемент И 8 и приводит к образованию единичного сигнала на выходе инвертора 5. Так как триггер 10 обнулен, то по очередному (седьмому) тактовому импульсу на выходе элемента И 7 образуется единичный сигнал, по которому осуществляется выдача найденного числа 1010 из старщих разрядов регистра 16 через выходной блок 13. Этот же сигнал элемента И 7 через элемент 12 задержки устанавливает триггер 10 управления в единнчное состояние. Этим самым дается разрешение на возвращение сжатой числовой последовательности в регистре 16 в исходное состояние. Для этой цели служат блок 14 сравнения, инвертор 6 и элемент И 9. Ввиду того, что содержимое регистра 15 (равное 0001) не равно содержимому п-старшим разрядам в регистре 16, то на выходе блока 14 сравнения формируется код нуля (нулевой сигнал), а на выходе инвертора 6 - код единицы (единичный сигнал), поэтому очередные тактовые импульсы, поступающие по щине 17, проходят только через открытый элемент И 9 (элементы И 8 и 7 закрыты) и элемент ИЛИ 4, под действием которых содержимое регистра 16 сдвига сдвигается влево до тех пор, пока в старщих его разрядах не оказывается число, равное содержимому регистра 15 (в нащем случае 0001), т.е. пока числовая последовательность не займет свое исходное положение. Таким образом, дополнительное количество сдвигов I необходимое для возвращения числовой последовательности в исходное состояние, определяется выражением I m - Л где m - количество триггеров (запоминающих элементов) в регистре 16, et -абсолютное значение номера (адреса) в последовательности. Очевидно, что для хранения 16-ти четырехразрядных чисел требуется 16 запоминающих элементов (триггеров). Их количество m определяется соотнощением m N, где N -- количество хранимых чисел в запоминающем устройстве. При обычном способе хранения этих же чисел пotpeбyeтcя 64 запоминающих элемента (триггера), так как m N-n 16-4 64, где п - разрядность хранимых чисел. Сравнительная оценка предлагаемого и известных запоминающих устройств по количеству запоминающих элементов (триггеров) в зависимости от объема Памяти приведена в таблице. Введение в предлагаемое устройство блока сравнения, счетчика, элементов ИЛИ, элементов И, инверторов, элементов задержки и сжатого способа хранения информации дает возможность значительно сократить объем оборудования, в особенности запоминающих элементов (триггеров), а следоваельно, увеличить его информационную емкость, надежность и снизить стоимость. Формула изобретения Запоминающее устройство, содержащее егистр сдвига, выход которого соединен с дним из входов выходного блока, триггер правления, первый элемент И, шину тактоых импульсов, соединенную с первым вхоом первого элемента И, второй вход котоого соединен с одним из выходов триггера правления, шину записи информации, соединенную со входом регистра хранения информации и с одним из входов регистра сдвига, шину сброса и адресную шину, отличающееся тем, что, с целью повышения информационной емкости устройства, в него введены блок сравнения, два элемента задержки, второй и третий элементы И, три элемента ИЛИ, два инвертора и счетчик, один из входов которого подключен к адресной шине, а другой вход - к выходу первого элемента задержки, выход счетчика соединен со входом первого элемента ИЛИ, выход которого подсоединен ко входу первого инвертора, к одному из входов второго элемента ИЛИ и к одному из входов второго элемента И, другой вход второго элемента ИЛИ соединен с шиной сброса, выход первого инвертора подключен к третьему входу первого элемента И, выход которого соединен с другим входом выходного блока и с входом второго элемента задержки, выход второго элемента ИЛИ подсоединен к одному из входов триггера управления, другой вход которого соединен с выходом второго элемента задержки, другой выход триггера управЯдрес М.

ления подключен к первому входу третьего эле1йента И, второй вход которого соединен с выходом второго инвертора, вход второго инвертора подсоединен к выходу блока сравнения, один из входов которого соединен с выходом регистра сдвига, другой вход блока сравнения подключен к выходу регистра хранения информации, другой вход регистра сдвига соединен с выходом третьего элемента ИЛИ, один из входов которого подсоединен к выходу второго элемента И и ко входу первого элемента задержки, другой вход третьего элемента ИЛИ подключен к выходу третьего элемента И, третий вход третьего элемента И и другой вход второго элемента И соединены с шиной тактовЪ1х импульсов.

Источники информации, принятые во внимание при экспертизе . 1. Патент Великобритании № 1471071, кл. G 11 С 19/00, опублик. 1977. 2. Авторское свидетельство СССР

№ 428454, кл. G 11 С 19/00, 1974 (прототип).

Авторы

Даты

1981-06-30—Публикация

1979-07-11—Подача