И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Преобразователь кодов | 1988 |

|

SU1566487A1 |

| Преобразователь кодов | 1989 |

|

SU1599916A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Преобразователь кодов | 1988 |

|

SU1649675A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1411995A1 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

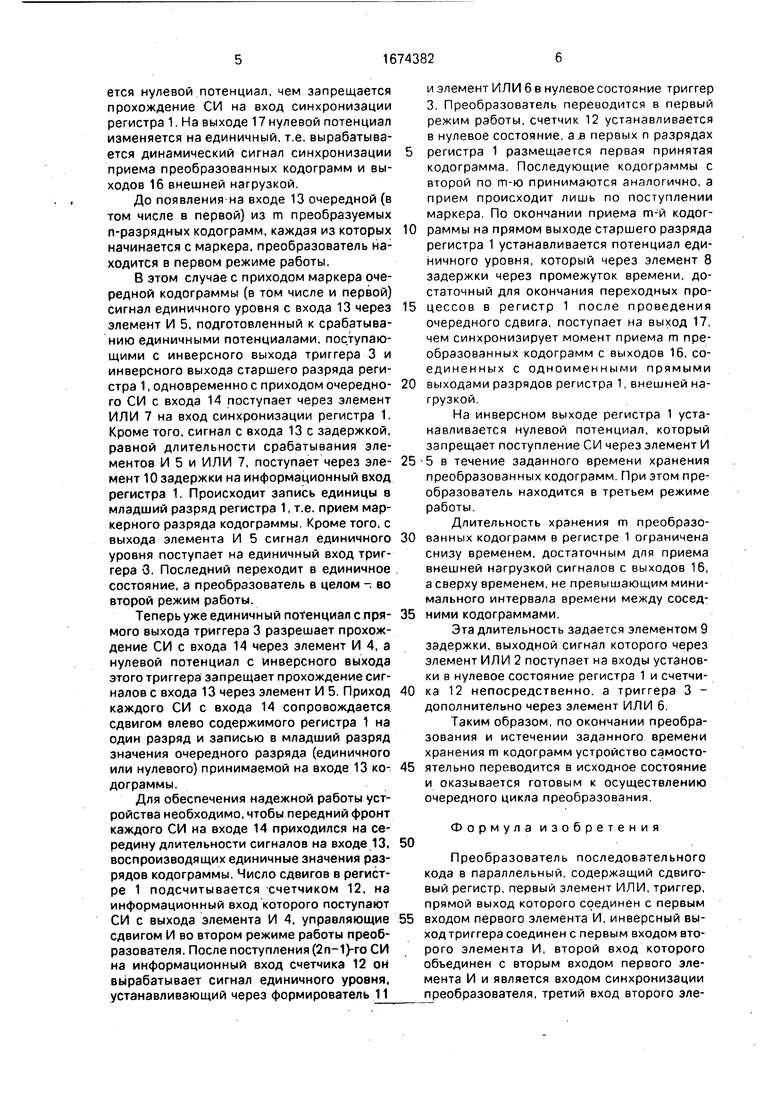

Изобретение относится к вычислительной технике и может найти применение в системах передачи данных по цифровым каналам, например для решения задач коммивояжера. Изобретение позволяет сохранять все разряды кодограммы, в том числе и маркерный разряд, за счет чего обеспечивается расширение области применения преобразователя. Преобразователь последовательного кода в параллельный содержит сдвиговый регистр 1, элементы ИЛИ 2, 6 и 7, триггер 3, элементы И 4 и 5, элементы 8 - 10 задержки, формирователь 11 импульсов и счетчик 12 импульсов. 1 ил.

0

ON СО 00

ю

Изобретение относится к вычислительной технике и может найти применение в системах передачи данных по цифровым каналам, например для решения задач коммивояжера.

Целью изобретения является расширение области применения преобразователя за счет обеспечения сохранности маркерного разряда в каждой из преобразуемых кодограмм.

На чертеже представлена функциональная схема преобразователя.

Преобразователь последовательного кода в параллельный содержит сдвиговый регистр 1, первый элемент ИЛИ 2, триггер 3, первый и второй элементы И 4 и 5, второй и третий элементы ИЛИ 6 и 7, первый - третий элементы 8-10 задержки, формирователь 11 импульсов и счетчик 12 импульсов, информационный вход 13, вход 14 синхронизации и вход 15 запуска, информационный выход 16 и выход 17 синхронизации.

Регистр 1 предназначен для преобразования каждой из n-разрядных кодограмм из последовательного кода в параллельный и их хранения в течение заданного времени. Триггер 3 предназначен для организации работы преобразователя в каждом из трех возможных режимов работы.

Счетчик 12 предназначен для фиксации момента окончания преобразования очередной кодограммы. Элемент 10 задержки предназначен для обеспечения надежной записи кодограммы в регистр 1. Элемент 8 задержки предназначен для синхронизации приема преобразованных кодограмм и времени окончания переходных процессов в регистре 1. Элемент 9 задержки предназначен для задания интервала времени, в течение которого m преобразованных ко; дограмм должны храниться в регистре 1.

Элемент И 5 предназначен для обеспечения синхронизации приема маркера, а элемент И 4 - для обеспечения синхронизации приема остальных разрядов кодограммы. Формирователь 11 импульсов предназначен для преобразования кратковременного выходного сигнала счетчика 12 в сигнал, достаточный по времени для установления триггера 3 в единичное состояние. Элемент ИЛИ 2 предназначен для обеспечения установки устройства в исходное состояние сигналом запуска или сигналом с выхода элемента 9 задержки, воспроизводимым по окончании преобразования т-й кодограммы. Элемент ИЛИ 7 предназначен для обеспечения синхронизации регистра 1 в первом или втором режиме работы преобразователя синхронизирующими импульсами, поступающими с входа 14. Элемент ИЛИ 6 предназначен для обеспечения установки в нулевое состояние триггера 3 сигна- лом запуска или сигналом с выхода

элемента 9 задержки.

Преобразователь работает следующим образом.

В исходном состоянии преобразователя регистр 1, триггер 3 и счетчик 12 находят0 ся в нулевом состоянии. На выходах 16 и выходе 17 устанавливается нулевой потенциал. На прямом выходе триггера 3 - единичный потенциал, который разрешает прохождение сигналов через элемент И 5.

5 На инверсном выходе старшего разряда регистра 1 устанавливается единичный потенциал, который разрешает прохождение СИ через элемент И 5. На выходе счетчика 12 - нулевой потенциал, который не способен

0 запустить формирователь 11

Работа преобразователя начинается с подачи на вход 15 сигнала запуска единичного уровня, длительность которого достаточна для установки преобразователя в

5 исходное состояние. Этот сигнал через элемент ИЛИ 2 поступает на входы установки в нулевое состояние регистра 1 и счетчика 12 непосредственно, а триггера 3 - дополнительно через элемент ИЛИ 6. По окончании

0 его действия на входы 14 и 15 могут подаваться сигналы единичного уровня. Преобразователь может работать в одном из трех режимов работы: режиме ожидания и приема маркера (первый), режиме приема ин5 формационных разрядов кодограммы (второй), режиме хранения кодограмм (третий).

Первый режим работы преобразователя имеет место при нахождении триггера 3 в

0 единичном состоянии и наличии единичного потенциала на инверсном выходе старшего разряда регистра 1.

В этом режиме никакая последовательность сигналов нулевого уровня с входа 13

5 преобразователем не воспринимается. Только с приходом маркера в младший разряд регистра 1 записывается единица.

Второй режим работы преобразователя отличается от первого тем, что триггер 3

0 находится в единичном состоянии. В этом режиме происходит запись каждого разряда принимаемой кодограммы независимо от его значения (нулевого или единичного) в регистр 1.

5 Третий режим работы преобразователя имеет место по окончании записи m-й кодограммы в регистр 1.

В этом режиме триггер 3 находится в нулевом состоянии, на инверсном выходе старшего разряда регистра 1 устанавливается нулевой потенциал, чем запрещается прохождение СИ на вход синхронизации регистра 1. На выходе 17 нулевой потенциал изменяется на единичный, т.е. вырабатывается динамический сигнал синхронизации приема преобразованных кодограмм и выходов 16 внешней нагрузкой.

До появления на входе 13 очередной (в том числе в первой) из m преобразуемых n-разрядных кодограмм, каждая из которых начинается с маркера, преобразователь находится в первом режиме работы.

В этом случае с приходом маркера очередной кодограммы (в том числе и первой) сигнал единичного уровня с входа 13 через элемент И 5, подготовленный к срабатыванию единичными потенциалами, поступающими с инверсного выхода триггера 3 и инверсного выхода старшего разряда регистра 1, одновременно с приходом очередного СИ с входа 14 поступает через элемент ИЛИ 7 на вход синхронизации регистра 1. Кроме того, сигнал с входа 13 с задержкой. равной длительности срабатывания элементов И 5 и ИЛИ 7, поступает через элемент 10 задержки на информационный вход регистра 1. Происходит запись единицы в младший разряд регистра 1. т.е. прием маркерного разряда кодограммы. Кроме того, с выхода элемента И 5 сигнал единичного уровня поступает на единичный вход триггера 3. Последний переходит в единичное состояние, а преобразователь в целом - во второй режим работы.

Теперь уже единичный потенциал с прямого выхода триггера 3 разрешает прохождение СИ с входа 14 через элемент И 4, а нулевой потенциал с инверсного выхода этого триггера запрещает прохождение сигналов с входа 13 через элемент И 5. Приход каждого СИ с входа 14 сопровождается сдвигом влево содержимого регистра 1 на один разряд и записью в младший разряд значения очередного разряда (единичного или нулевого) принимаемой на входе 13 кодограммы.

Для обеспечения надежной работы устройства необходимо, чтобы передний фронт каждого СИ на входе 14 приходился на середину длительности сигналов на входе 13, воспроизводящих единичные значения разрядов кодограммы. Число сдвигов в регистре 1 подсчитывается счетчиком 12, на информационный вход которого поступают СИ с выхода элемента И 4, управляющие сдвигом И во втором режиме работы преобразователя. После поступления (2п-1)-го СИ на информационный вход счетчика 12 он вырабатывает сигнал единичного уровня, устанавливающий через формирователь 11

и элемент ИЛИ 6 в нулевоесостояние триггер 3. Преобразователь переиодится в первый режим работы, счегчик 12 устанавливается в нулевое состояние, а в первых п разрядах 5 регистра 1 размещается первая принятая кодограмма. Последующие кодограммы с второй по m-ю принимаются аналогично, а прием происходит лишь по поступлении маркера. По окончании приема m-й кодог- 0 раммы на прямом выходе старшего разряда регистра 1 устанавливается потенциал единичного уровня, который через элемент 8 задержки через промежуток времени, достаточный для окончания переходных про5 цессов в регистр 1 после проведения очередного сдвига, поступает на выход 17, чем синхронизирует момент приема m преобразованных кодограмм с выходов 16. соединенных с одноименными прямыми

0 выходами разрядов регистра 1, внешней нагрузкой.

На инверсном выходе регистра 1 устанавливается нулевой потенциал, который запрещает поступление СИ через элемент И

5 5 в течение заданного времени хранения преобразованных кодограмм. При этом преобразователь находится в третьем режиме работы.

Длительность хранения m преобразо0 ванных кодограмм в регистре 1 ограничена снизу временем, достаточным для приема внешней нагрузкой сигналов с выходов 16, а сверху временем, не превышающим минимального интервала времени между сосед5 ними кодограммами.

Эта длительность задается элементом 9 задержки, выходной сигнал которого через элемент ИЛИ 2 поступает на входы установки в нулевое состояние регистра 1 и счетчи0 ка 12 непосредственно, а триггера 3 - дополнительно через элемент ИЛИ 6.

Таким образом, по окончании преобразования и истечении заданного времени хранения m кодограмм устройство самосто5 ятельно переводится в исходное состояние и оказывается готовым к осуществлению очередного цикла преобразования.

50

Формула изобретения

Преобразователь последовательного кода в параллельный, содержащий сдвиговый регистр, первый элемент ИЛИ. триггер, прямой выход которого соединен с первым 5 входом первого элемента И, инверсный выход триггера соединен с первым входом второго элемента И, второй вход которого объединен с вторым входом первого элемента И и является входом синхронизации преобразователя, третий вход второго элемента И является информационным входом преобразователя, прямые выходы разрядов сдвигового регистра являются информационным выходом преобразователя, о т л и ч а ю- щ и и с я тем, что, с целью расширения области применения преобразователя за счет обеспечения сохранности маркерного разряда в каждой из преобразуемы кодограмм, в преобразователь введены второй и третий элементы ИЛИ, элементы задержки, формирователь импульсов и счетчик импульсов, выход которого через формирователь импульсов соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом триггера, выход первого элемента И соединен с информационным входом счетчика импульсов и с первым входом третьего элемента ИЛИ, выход которого соединен с входом синхронизации сдвигового регистра, инверсный выход

ст;эршего разряда которого соединен с четвертым входом второго элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ и с вторым входом триггера, входы первого и второго элементов задержки объединены и подключены к прямому выходу старшего разряда сдвигового регистра, выход первого элемента задержки является выходом синхронизации преобразователя, выход второго элемента задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен с установочными входами счетчика импульсов и сдвигового регистра и с вторым входом второго элемента ИЛИ, выход третьего элемента задержки соединен с информационным входом сдвигового регистра, вход третьего элемента задержки объединен с третьим входом второго элемента И. второй вход первого элемента ИЛИ является входом запуска преобразователя.

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь последовательногоКОдА B пАРАллЕльНый | 1979 |

|

SU851396A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-30—Публикация

1988-08-08—Подача