СП

;о

:о со

31

Изобретение относится к автоматик и вычислительной технике и может быт использовано при построении преобразователей, входящих в состав блоков сопряжения цифровых устройств с каналами связи. .

Цель изобретения - повышение быстродействия преобразователя за счет сокращения длины маркера конца кодограммы.

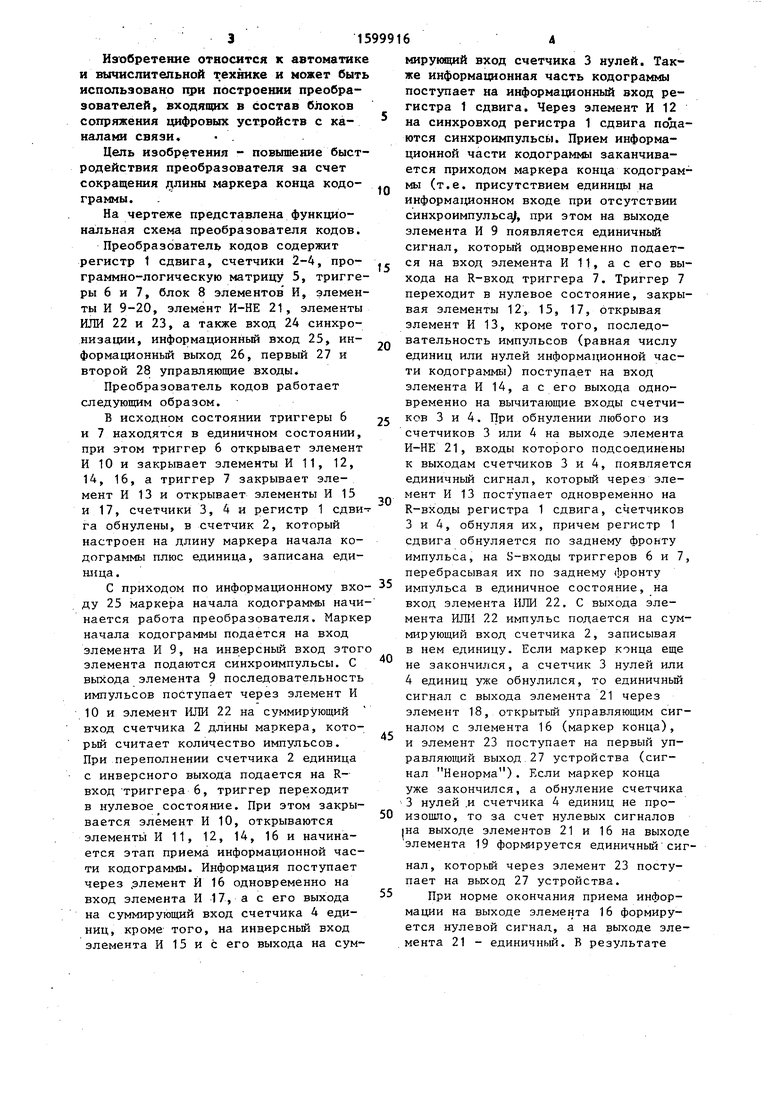

На чертеже представлена функциональная схема преобразователя кодов.

Преобразователь кодов содержит регистр 1 сдвига, счетчики 2-4, программно-логическую матрицу 5, триггеры 6 и 7, блок 8 элементов И, элементы И 9-20, элемент И-НЕ 21, элементы ИЛИ 22 и 23, а также вход 24 синхронизации, информационный вход 25, информационный выход 26, первый 27 и второй 28 управляющие входы.

Преобразователь кодов работает следующим образом.

В исходном состоянии триггеры 6 и 7 находятся в единичном состоянии, при этом триггер 6 открывает элемент И 10 и закрывает элементы И 11, 12, 14, 16, а триггер 7 закрывает элемент И 13 и открывает элементы И 15 и 17, счетчики 3, 4 и регистр 1 сдвига обнулены, в счетчик 2, который настроен на длину маркера начала кодограммы плюс единица, записана единица .

С приходом по информационному вхо ду 25 маркера начала кодограммы начи нается работа преобразователя. Марке начала кодограммы подается на вход элемента И 9, на инверсный вход этог элемента подаются синхроимпульсы. С выхода элемента 9 последовательность импульсов поступает через элемент И 10 и элемент ИЛИ 22 на суммирующий вход счетчика 2 длины маркера, который считает количество импульсов. При переполнении счетчика 2 единица с инверсного выхода подается на R- вход триггера 6, триггер переходит в нулевое состояние. При этом закрывается элемент И 10, открываются элементы И 11, 12, 14, 16 и начинается этап приема информационной части кодограммы. Информация поступает через .элемент И 16 одновременно на вход элемента И 17, а с его выхода на суммирующий вход счетчика 4 единиц, кроме того, на инверсньй вход элемента И 15 и с его выхода на сум

0

5

0

5

916

5

0

0

45

50

55

А

мирукиций вход счетчика 3 нулей. Также информационная часть кодограммы поступает на информационный вход регистра 1 сдвига. Через злемент И 12 на синхровход регистра 1 сдвига подаются синхроимпульсы. Прием информационной части кодограммы заканчивается приходом маркера конца кодограммы (т.е. присутствием единицы на информатдюнном входе при отсутствии синхроимпульса, при этом на выходе элемента И 9 появляется единичньй сигнал, который одновременно подается на вход элемента И 11, ас его выхода на R-вход триггера 7. Триггер 7 переходит в нулевое состояние, закрывая элементы 12, 15, 17, открывая элемент И 13, кроме того, последовательность импульсов (равная числу единиц или нулей информационной части кодограммы) поступает на вход элемента И 14, ас его выхода одновременно на вычитающие входы счетчиков 3 и 4. При обнулении любого из счетчиков 3 или 4 на выходе элемента И-НЕ 21, входы которого подсоединены к выходам счетчиков 3 и 4, появляется единичньй сигнал, который через элемент И 13 поступает одновременно на R-входы регистра 1 сдвига, счетчиков

3и 4, обнуляя их, причем регистр 1 сдвига обнуляется по заднему фронту импульса, на S-входы триггеров 6 и 7, перебрасывая их по заднему фронту импульса в единичное состояние, на вход элемента ИЛИ 22. С выхода элемента ИЛИ 22 импульс подается на суммирующий вход счетчика 2, записывая

в нем единицу. Если маркер конца еще не закончился, а счетчик 3 нулей или

4единиц уже обнулился, то единичньй сигнал с выхода элемента 21 через элемент 18, открытьй управляющим сигналом с элемента 16 (маркер конца),

и элемент 23 поступает на первый управляющий выход 27 устройства (сигнал Ненорма). Если маркер конца уже закончился, а обнуление счетчика 3 нулей .и счетчика 4 единиц не произошло, то за счет нулевых сигналов 1на выходе элементов 21 и 16 на выходе элемента 19 формируется единичньй сигнал, которьй через элемент 23 поступает на выход 27 устройства.

При норме окончания приема информации на выходе элемента 16 формируется нулевой сигнал, а на выходе элемента 21 - единичньй. В результате

а выходе элемента 20 формируется единичный сигнал, который поступает а второй управлянидий выход 28 устойства (Норма)i

ормула изобретения

1

Преобразователь кодов, содержащий регистр сдвига, выходы разрядов которого соединены с соответствующими первыми входами блока элементов И, выходы которого соединены с соответствующими входами программно-логической матрицы, выходы которой являются информационными выходами преобразователя, первый элемент И, выход которого соединен с первым входом первого элемента ИЛИ, второй элемент И, выход которого соединен с R-входон первого триггера, прямой выход которого соединен с первым прямым входом третьего элемента И и первым входом четвертого элемента И, выход которого соединен с С-входом регистра сдвига, пятый элемент И, инверсньй вход которого и второй вход четвертого элемента И объединены и являются входом синхронизации преобразователя, прямой вход пятого элемента И объединен с первым входом шестого элемента И и является информационным входом преобразователя, седьмой и восьмой элементы И, выходы которых соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого является первым управляющим выходом преобразователя, девятый элемент И и первый и второй счетчики, о тл.и ч а ющи и с я тем, что, с целью повышения быстродействия преобразователя, в него введены десятый- двенадцатый элементы И, элемент И-НЕ, третий счетчик и второй триггер, инверсньй выход которого соединен с первыми входами второго и девятого элементов И, третьим входом четверто0

5 -0

5

0

5

0

5

ГО элемента И и вторым входом шестого элемента И, выход которого соединен с V-входом регистра сдвига, инверсным -входом третьего элемента И, первыми входами седьмого и десятого элементов И и с первым инверсным входом восьмого элемента И, выход пятого элемента И соединен с первым входом первого элемента И, инверсным входом одиннадцатого элемента И и вторыми входами второго и девятого элементов И, выход девятого элемента И соединен с вычитающими входами первого и второго счетчиков, выходы которых соединены соответственно с первым и вторым входами элемента И-НЁ, выход которого соединен с вторыми входами блока элементов И и седьмого элемента И, прямым входом двенадцатого элемента И, вторым инверсным входом восьмого элемента И и прямым входом одиннадцатого элемента И, выход которого соединен с R-входами регистра сдвига, первого и второго счетчиков, S-входа- ми первого и второго триггеров и вторым входом первого элемента ИЛИ, выход которого соединен с суммирующим входом третьего счетчика, инверсный выход которого соединен с R-входом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, второй прямой вход третьего элемента И и второй вход десятого элемента И подключены к входу синхронизации преобразователя, третий вход десятого элемента И подключен к прямому выходу первого триггера, выходы третьего и десятого элементов И соединены с суммирующими входами соответственно первого и второго счетчиков, выход второго элемента ИЛИ соединен с инверсным входом двенадцатого элемента И, выход которого является вторым управляющим выходом преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1990 |

|

SU1809540A1 |

| Преобразователь кодов | 1988 |

|

SU1649675A1 |

| Преобразователь кодов | 1988 |

|

SU1566487A1 |

| Преобразователь кодов | 1984 |

|

SU1229967A1 |

| Устройство для преобразования кодов | 1990 |

|

SU1809539A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для моделирования процесса передачи информации | 1989 |

|

SU1777149A1 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1674382A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей, входящих в состав блоков сопряжения цифровых устройств с каналами связи. Цель изобретения - повышение быстродействия. Преобразователь содержит регистр 1 сдвига, счетчики 2-4, программно-логическую матрицу 5, триггеры 6, 7, блок 8 элементов И, элементы И 9-20, элемент И-НЕ 21, элементы ИЛИ 22, 23. 1 ил.

| Авторское свидетельство СССР | |||

| -1385995, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-15—Публикация

1989-01-03—Подача