СВЯЗИ регистров со схемой обработки (до 7 байтных связей) коммутатор входа, специальные микропрнказы упрЕ1влсния. Схема однобайтной обработки является инородным телом в процессоре, нарушает регулярность структуры, затрудняет реализацию процессора на больидих интегральных схемах, ухудшает надежность.

Известно также устройство для об работки данных, содержащее блок памяти, арифметическо-логичэское устройство, разбитое на схемы, которые коымутируются схемой задания конфигурации, распределитель слов, связанный с кодовой шиной, блок разбивки секций, распределитель символов, связанный через кодовую шину символа с блоком формирования сикшолов, который подключен к блоку разбивки секдий 2. В этом, устройстве логическая обработка выполняется также посимвольно, но в обработке ynacTEiyjOT несколько секдий арифметическо-логического устройства. Информация из распределителя символов по кодовым шинам символа поступает на блок формирования символов, который через блок разбивки секций,организует объединение соответствую.щи.х секций арифметического и логического устройства для работы с символами, поступающими на эти секции с блока формирования символов. С этих секций обработанная информация поступает на блок формирования символов и кодовые шины символов на распределитель символов для пересылки ее в нужное устройство процессора и блок памяти,

Это устройство имеет существенные преимущества перед предьщутцим устройством, так как логическая обработ™ ка символов производится с использованием основного оборудования, а не на специальном оборудовании. Однако, обладая более высоким коэффициентом использования оборудования, оно не обладает высоким быстродействием, так как обработка производится посимвольно, т.е процесс обработки одного слова разбивается на четыре этапа, выполняемых последовательно.

Наиболее близким к изобретению по технической сущности и достигаемому положительному результату является устройство для обработки данных переменной длины, содержащее блок памяти J первый вход которого соединен с выхо ; дом арифметико-логического блока, ком

мутатор первый и второй вылоды которого соедииень соотБеаСТВйнно с перовым и вторым входами арифметяко-ло- гического блока, блок управления, выход которого соединен с первым входом KDMNQTHTOpa, вторым аходэм блока па- мяти и трет1 им входам арифметико-логического блоквг первую и вторую шины обмена, причем третий вход и первый вькод блока памяти, первые аход и выход устройства соединены с первой шиной обмена, четвертый ьход и второй выход блока памяти, вторые вход и выход устройства соединены с вт.о- рой шиной обмена, первьШ и второй входы - вьрсоды комментатора соединены соответственно с первой и второй шинами обмена з.

Однако подусловный формат пересылок значительно снижает быстродействие устройства, так как цикл обращения в оперативную память обычно в 3-4 раза длительнее внутреннего цикла устройства, т,е, устройство будет простаивать в ожидании информации из памяти Обращение в память за полным словом выгоднее, так как позволяет более полно использовать время обращения для загрузки оборудования обработкой, полученной в предьщущем такте информации.

Наличие байтной обработки символо также значительно снижает быстродей- c-fBHe устройства, вследствие расчла нения процесса обработки на выполняемые последовательные циклы, Компо- новка информации на входах арифметико-логического блока сводится к подключению правого или левого байтов Расширение данной структуры до четырех байтов значительно усложнило бы как аппаратуру коммутатора, так и схемь управления имиа

,Цвль изобретения - повьпиение быстродействия,. , ..

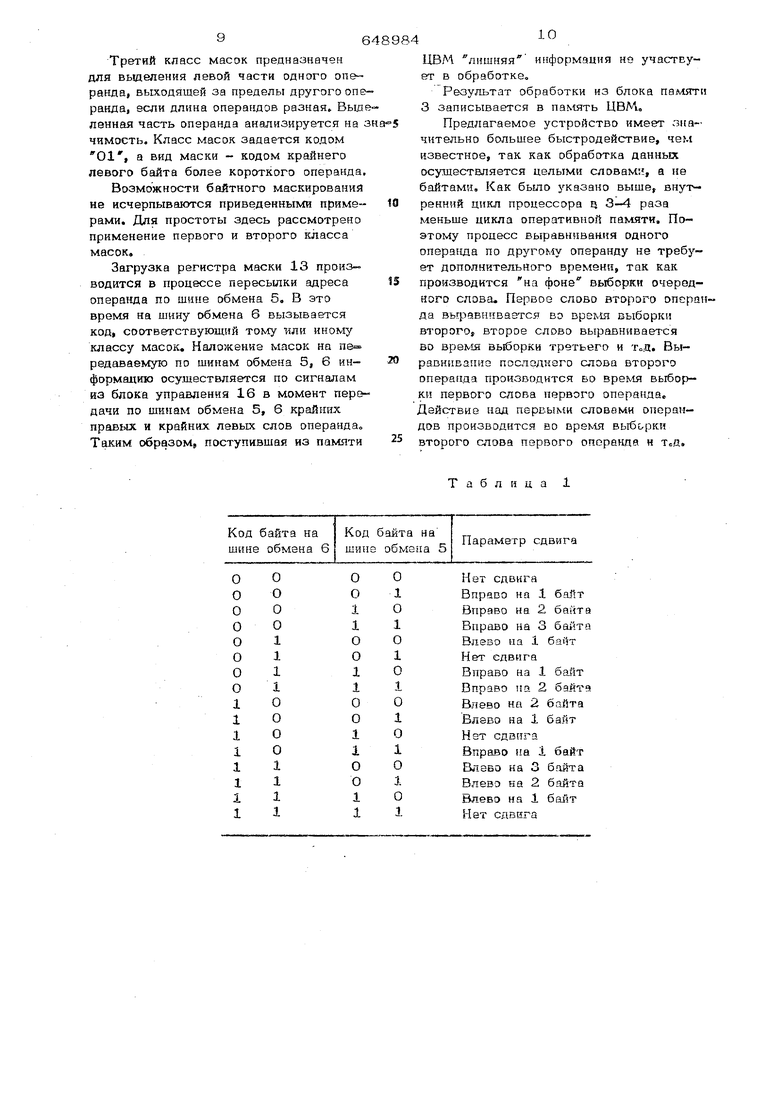

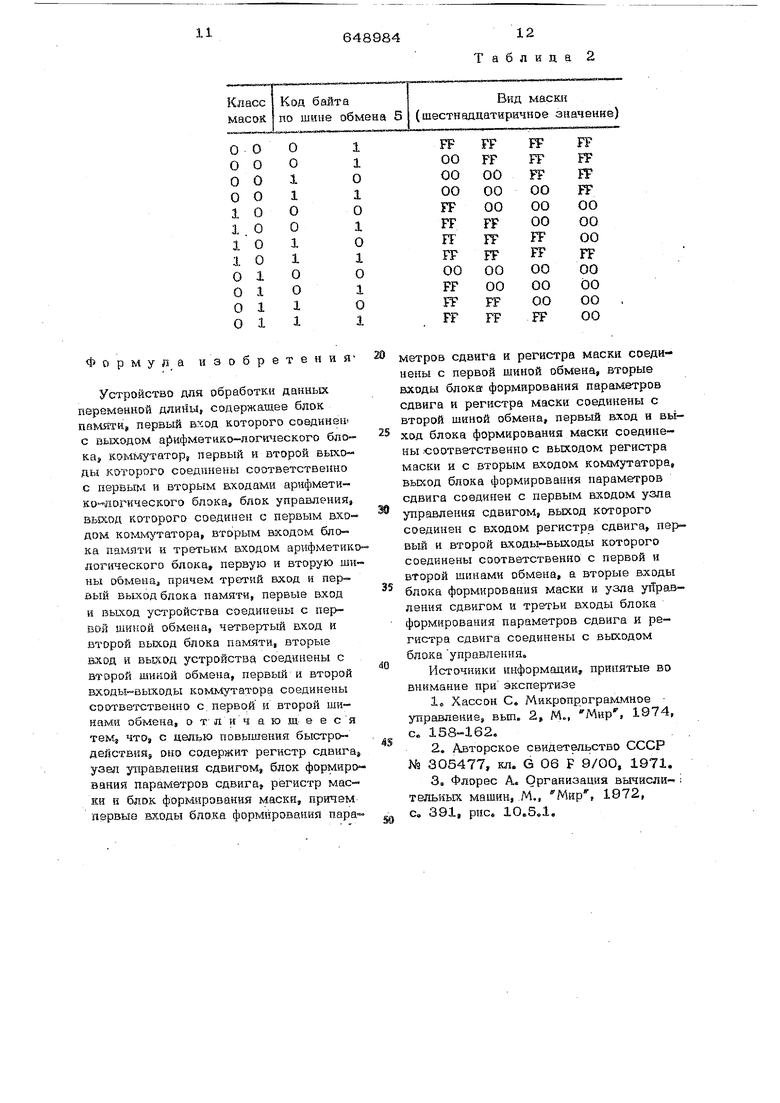

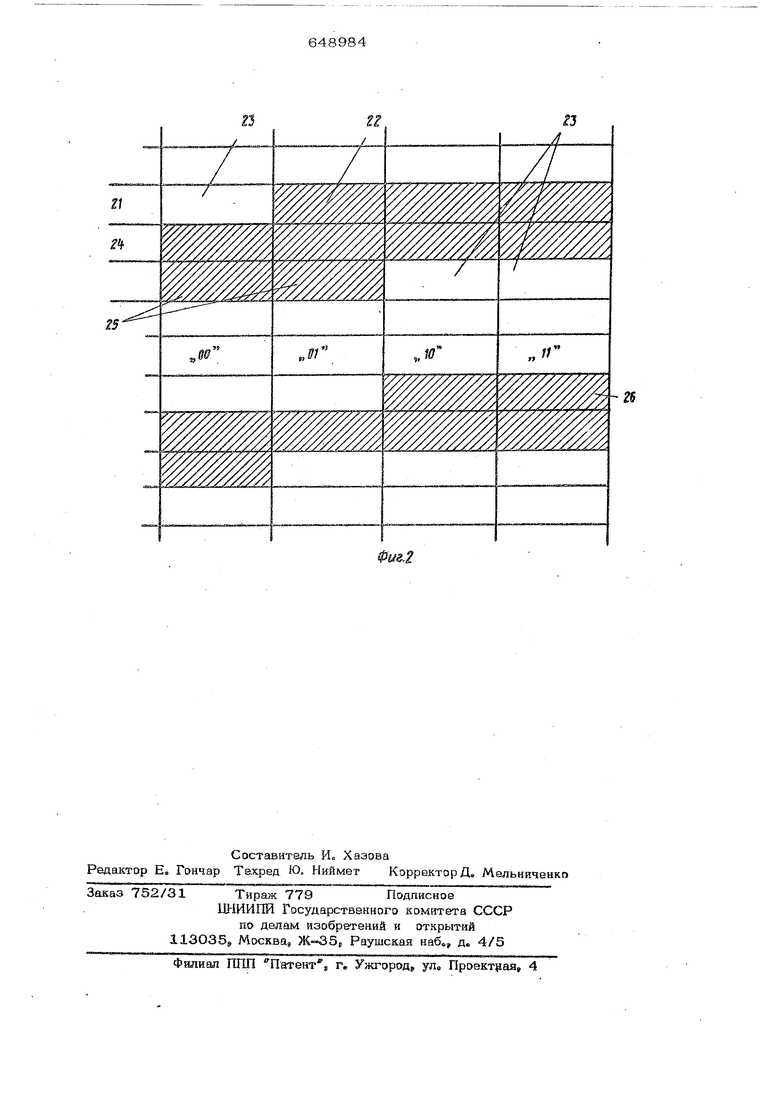

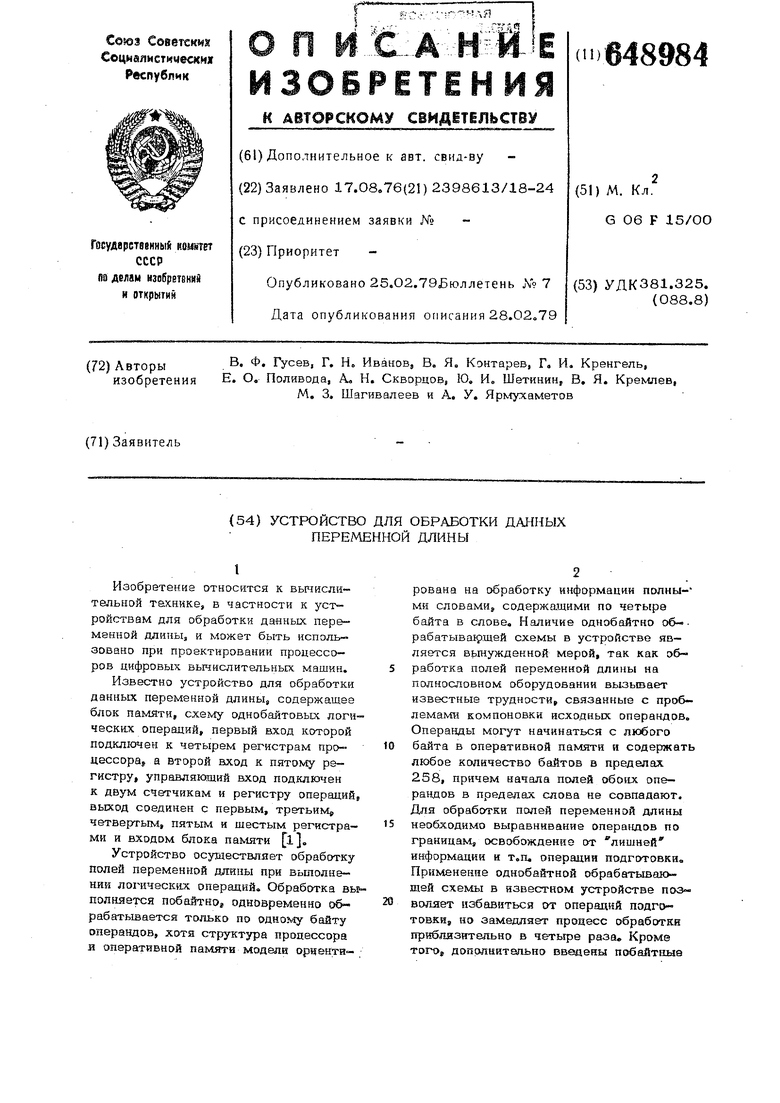

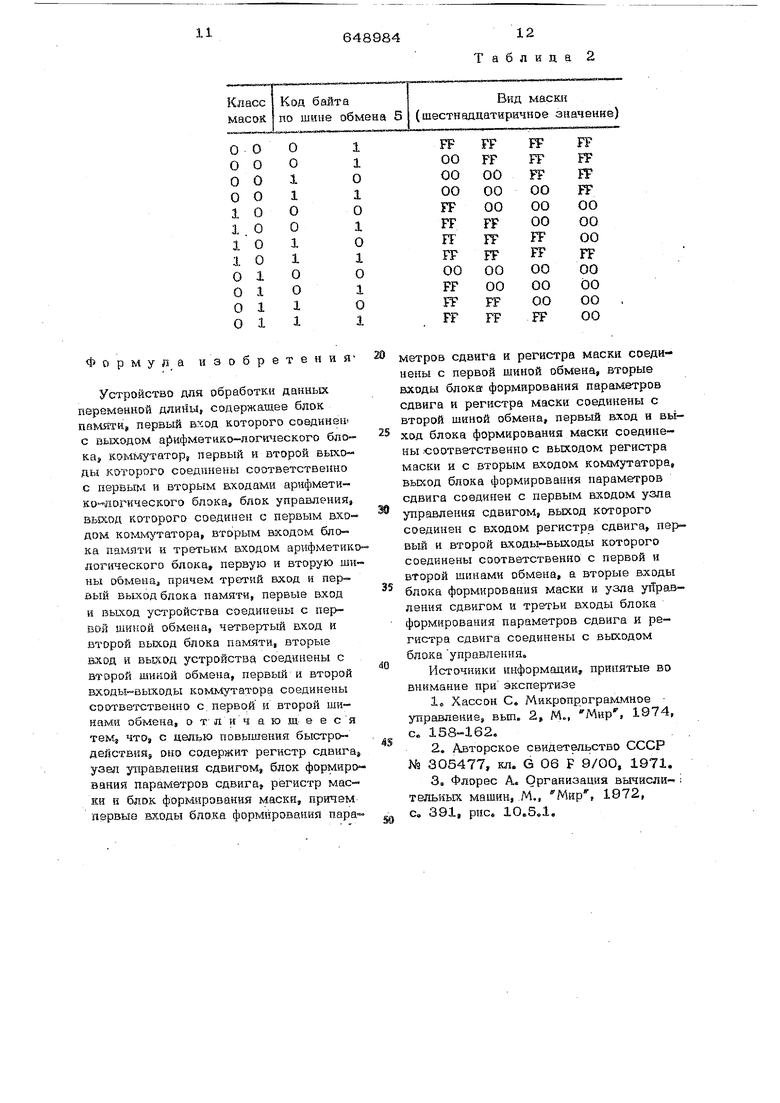

Достигается это тем, что устройст- во содержит регистрсдвига, узел управления сдвигом, блок формирования параметров сдвигаг регистр маски .и блок формирования маски, причем пер™ вые аходы блока формирования параметров сдвига и-регистра маски соединены с первой шиной обмена, вторые входы блока формирования параметров сдвига и регистра маскй соединены с второй шиной обмена, первый вход и выход блока формировашш маска cosw динены соответственно с выходом ре гистра маски и с вторым аходом ком мутатора, вьсход блока формирования параметров сдвига соединен с первым входом узла управления сдвигом, выход торого соединен с входом регистра сдвиг первый и второй входы - выходы которог соединены соответственно с первой и второй шинами обмена, а вторые входы блока формирования маски и узла управ ления сдвигом и третьи входы блока формирования параметров сдвига и регистра сдвига соединены с выходом блока управления. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - пример расположения данных переменной длины в оперативной памяти ЦВМ. Устройства для обработки данных переменной длины содержит арифметико логический блок 1 с выходом 2, блок памяти 3, коммутатор 4, первую шину обмена 5, вторую шину обмена 6, регистр сдвига 7, входы 8,9, выходы Ю 11, блок 12 формирования параметров сдвига, регистр маски 13, блок 14 формирования маски, узел 15 управлени сдвигом, блок управления 16, входывыходы 17, 18 коммутатора, входывыходы 19, 20 регистра сдвига. Данные переменной длины, могут быть расположены следующим образом (см. фиг. 2): 21 - первое слово операнда, 22 - первый байт поля данных, 23 - лишние байты, 24 - последнее слово операнда, 25 - последние байты поля данных, 26 - второй операнд, коды 00, 01, 10, 11 - коды байтов. Адресуемой единицей информации в оперативной памяти ЦВМ является байт группа двоичных разрядов, сопровождае мая контрольным разрядом. Одно слово оперативной памяти содержит четыре байта, причем, поле данных может начинаться и заканчиваться на любом бай те в пределах слова. При обращении за операндами информация извлекается из памяти целыми словами, и,если операнд начинается (или заканчивается) в пределах данного слова, то в устройство обработки поступают как нужные байты так и лишние байты, относяшиеся к другим операциям (см. фиг. 2). Поле данных определяется, например адресом первого байта поля и его дли ной (количеством байтов в поле), либо адресом первого и последнего байтов поля. При любом виде адресадии фигурирует понятие адрес байта. Адрес байта складывается из адреса слова памяти и позиции байта внутри слова (кода байта) и определяется выражениемАБ АС+КБ, где АБ - адрес байта; АС - адрес слова; КБ - код байта. Как правило, при обращении в память за словом последний компонент адреса (КБ) игнорируется. Код байта может принять численное значение СО, 01, 1О и 11, определяя соответственно первый, второй, третий и четвертый байты в слове. Коды байтов показаны на фиг. 2. В этом примере код крайнего левого байта первого операнда будет 01, код крайнего правого байта того же операнда будет также 01, код крайнего левого байта второго опера1ща 10, а его крайнего правого байта ОО. Очевидно, что перед послов Jй обработкой операвдов, они должны быть расположены так, чтобы соответствующие байты операндов занимали одноименные позиции в слове, т.е. операнды должны быть выравнены. Большинс-пво систем команд современных ЭВМ указывают только адреса исходных операвдов, определяя адрес записи результата косвенно. Например, в системе команд ЕС ЭВМ результат должен быть записан по адресу первого операнда, т.е. занять его место в памяти после обработки. Поэтому выравнивать один операвд по другому, например, по первому, чтобы результат оказался автоматически в той позиции, в которой он должен быть записан в память. Как видно из фиг. 2, процесс выравнивания может быть осуществлен путем сдвига вправо всех байтов одного операнда до тех пор, пока крайний правый байт этого операнда не займет позицию крайнего правого байта другого операнда при выравнивании по правой границе или аналогичным процессом сдвига влево при выравнивании по левой границе, причем величина сдвига определяется разностью кодов байтов, а направление - их взаимным расположением, Устройство работает следующим образом. Адреса данных, например адреса райних правых байтов обоих операндов. 6 назьшаются из блока памяти 3 на шнну обмена 5 и на шину обмена 6. Входы блока 12 параметров сдвига и регистра масЕи 13 подключены к тем разрядам шин обмена 5 и 6, куда поступают коды байтов (КБ) при пересьшке адресов по шинам обмена. По сигналу из блока управления 16 упомянутые коды байтов принимаются в блок 12 формирований параметров сдвига, где по взаимному расположению операндов и разности меж ду кодами 6afiTOB вычисляется параметр сдвига и его направление согласно табл. 1. По сигналу из блока управления 16 параметр сдвига, опре деляющий направление сдвига и его величину, подается на узел 15 управления сдвигом, где хранится до конца обработки. Параметр сдвига вычисляется относительно одного из адресов, напри- мер адреса, вызываемого на шину обмена 5. При вьфавнивании по первому операнду его адрес вызывается на шину обмена 5, а адр ; выравниваемого операнда на шнну обмена 6. Следует отмктить, что при выравнивании по правой границе на шины обмена 5, 6 подаются-адреса крайних правых байтов, а при выравнивании по левой границе (например, для операции сравнения) на шины обмена 5, 6 подаются адреса крайних левых байтов. Адрес второго операнда по одному из выходов, например 11, поступает в память ЦВМ (на фиг. 1 не показана) Извлеченное из памяти ЦВМ слово поступает на шины обмена 5, 6 по входу, например 8, и записывается в блок памяти 3. Адрес продвигается на величину, равную количеству байтов в слове, и производится новый Запрос за следую шим словом данных. Полученное из па мяти ЦВМ слово вместе со словом, полученным в предьщуяцем такте, вызывае ся на шины обмена 5 и 6, эти два слова сдвигаются на регистре сдвига 7 по сигналам из узла 15 управления сдвигом, который вырабатывает последовательность сигналов для обеспечения нужного сдвига, согласно зафиксированного параметра сдвига. Результат сдвига записывается в блок пакадти 3, Тем временем производится обращение за следующим словом и т,д. пока все поле второго операнда не будет извлечено из памяти, выравнено пи первому операнду и расположено в блоке памяти 3. Если длинный операнд не помещается в бло48е памяти 3, выравнивание может быть ыполнено по частям По окончании извлечения из памяти ВМ и выравнивания второго операнда ачинается извлечение из памяти ЦВМ ервого операнда по словам Полученное из ЦВМ по одноу из аходов 18 или 19 слово первого операнда вызывается на одну из шин обмена, например 5, а на шину обмена 6 из блока памяти 3 вызывается соответствующее ему слово второго операнда. Блоком управления 16 арифметико-логического блока 1 задается вид выполняемой операции Через коммутатор 4 операнды с шин обмена 5 и 6 поступаю-т на входы арифметикологического блока 1, который преобра зует операнды, согласно заданной блоком управления 16 функции. Результат преобразования с выхода 2 арифметикологического блока 1 записывается в блок памяти Зо Для того, чтобы в преобразованиях не участвовала лишняя информация, извлеченная из памяти ЦВМ вместе с нужной в составе одного слова оперативной памяти, на поступаюшую через коммутатор 4 информацию накладывается байтная маска. Выработка байтной маски производится блоком 14 формирования маски в зависимости от кодов, присутствующих на регистре маски 13. Наложение маски на информацию производится путем логического умножения (функция И)дан ных, передаваемых по шинам обмена 5 и 6, и маскирующей информации, вырабатываемой блоком 14 формирования маски. Операция наложения маски осушествляется коммутатором 4 по сигналу из блока управления 16, Виды масок приведены в табЛо 2. Как видно из таблицы применяются три класса масок,. Первый класс задается кодом 00 на шине обмена 6. Маска предназначена для освобождения от лишней информации слева от обрабатываемого поля. Вид маски определяется кодом Kpaiinero левого байта операнда, поступшозцего ма регистр маски 13с шины обмена 5, Второй класс масок задается кодом 10 на шине обмена 6 и предназначен для освобождения от лишней информации справа от обрабатываемого поля, Вид маски определяется кодом крайнего правого байта операнда. Третий класс масок предназначен для выделения левой части одного операнда, выходящей за пределы другого опе ранда, если длина операндов разная, Вьщ ленная часть операнда анализируется на чимость. Класс масок задается кодом 01, а вид маски - кодом крайнего левого байта более короткого операнда Возможности байтного маскирования не исчерпываются приведенными примерами. Для простоты здесь рассмотрено применение первого и второго класса масок. Загрузка регистра маски 13 произ водится в процессе пересылки адреса операнда по шине обмена 5, В это время на шину обмена 6 вызывается код, соответствующий тому или иному классу масок. Наложение масок на пе редаваемую по шинам обмена 5, 6 информацию осуществляется по сигналам из блока управления 16 в момент пере дачи по шинам обмена 5, 6 крайних правых и крайних левых слов операнда. Таким образом, поступившая из памяти

Таблица 1 llBAl лишняя информация но участвует в обработке. Результат обработки из блока памяти 3 записывается в память ЦВМ, Предлагаемое устройство имеет значительно большее быстродействие, чем известное, так как обработка данных осушествляется целыми словами, а не байтами. Как было указано выше, внутренний цикл процессора 5 3-4 раза меньше цикла оперативной памяти, По этому процесс выравнивания одного операвда по другому операнду не требу ет дополнительного времени, так как производится на фоне выборки очередного слова. Первое слово второго oncpaisда выравннвается во выборки второго, второе слово выравнивается во время выборки третьего и ТоД. Выравнивапиз последнего слова второго операвда производится во время выборки первого слова первого операнда. Действие над первыми словами операндов производится во время выборки второго слова первого операнда н Тсй,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для обработки информационных полей переменной длины | 1978 |

|

SU767769A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

о 1 о 1 о 1 о 1

Нет сдвига Вправо на .1 байт Вправо на 2 байта Вправо на 3 6aiiTa Влево на 1 байт Нет сдвига Вправо на 1 байт Вправо на 2 байта

о 1 о 1 о 1 о 1 Влево на 2 байта Влево на 1 байт Нет сдвига Вправо на 1 байт Ekte-Bo на 3 байта Влево на 2 байта на 1 байт Нет сдвига

II Формупа изобретения Устройство для обработки данньос переменной длийы, содержащее блок nsMSiTH, первый вход которого соад1шен с выходом а{5ифмвтнко-логического бло- KBj коммутатор, первый и второй выхоAbs которого соединены соответственно с первым и вторым ьходами арифметико-логического блока, блок управления, вь5ход которого соединен с первым входом комк утатора, вторым входом бло ка памяти и третьим аходом арифметико логического блока, первую и вторую ши ны обмена, причем третий вход и первый выход блока памяти, первые вход и устройства соединены с первой шиной обмена, четвертый вход и второй выход блока памяти, вторые вход и вьосод устройстве соединены с второй шиной обмена, первый и второй входы-выходы коммутатора соединены соответственно с первой- и второй шинами обмена, о Тл и ч а ю т. е е ся теМг что, с аелью повышения быстро-действкя оно содержит регистр сдвига узел управления сдвигом, блок формирований параметров сдвига регистр маски н блок формирования маски, причем первые входы блока формирования пара

12

648984

Таблица 2 метров сдвига и регистра маскн соединены с первой щиной обмена, вторые входы блока; формирования параметров сдвига и регистра маски соединены с второй шиной обмена, первый вход и выход блока формирования маски соединены соответственно с выходом регистра маски и с вторым аходом коммутатора, выход блока формирования параметров сдвига соединен с первым входом узла управления сдвигом, выход которого соединен с входом регистра сдвига, и второй &ходы выходы которого соединены соответственно с первой и второй шинами обмена, а вторые входы блока формирования маски и узла уйраБ ления сдвигом и третьи входы блока формирования параметров сдвига и регистра сдвига соединены с выходом блокауправления. Источники информации, принятые во внимание при экспертизе 1е X асе он С, Mикpoпpoгpaм шoe управление, вьш. 2, М., Мир, 1974, Се 158-162. 2. Авторское свидетельство СССР № 30S477, кл. G 06 F 9/00, 1971. За Флорес А. Организация вычисли- i телькых машин, ,М., Мир, 1972, с, 391, рис, 10.5Л,

Авторы

Даты

1979-02-25—Публикация

1976-08-17—Подача