Изобретение относится к микроэлектронике и импульсной технике и предназначено для реализации фундаментальных симметрических булевых функций (ф.с.б.ф.) п переменных.

Известен многофункциональный логический модуль, содержащий выполненные на МОП-транзисторах п элементов НЕ и п линеек логических ячеек, 1-я (,2,...,п) из которых содержит п-Н-1 логических ячеек, каждая из которых представляет собой выполненные на МОП-транзисторах элементы 2-2И-2ИЛИ-НЕ (если i - нечетное) и элементы 2-2ИЛИ-2И-НЕ (если I - четное) 1. Модуль при простой настройке реализует все симметрические булевые функции (в том числе и все ф.с.б.ф.) п переменных.

Недостатком модуля является ограниченная область применения , rak как он имеет только один выход и не позволяет одновременно вычислять значения п+1 ф.с.б.ф. на данном наборе п переменных.

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является устройство для выделения двоичных кодовых комбинаций произвольного веса, содержащее n-входовый элемент ИЛИ, элемент И, п-2 пороговых элементов, п-1 элементов ЗАПРЕТ, элемент НЕ, п входов и п+1 выходов 2. Устройство реализует одновременно n+Т ф.с.б.ф. п переменных.

Недостатком известного устройства является высокая конструктивная сложность, которая по числу МОП-транзисторов для определенной интегральной технологии оценивается как 0(п ).

Цель изобретения - упрощение многофункционального логического модуля.

Многофункциональный логический модуль содержит п (п - число переменных реализуемых булевых функций) элементов ЙЕ, п-1 групп элементов И и п-1 групп элементов 2-2И-2ИЛИ, п информационных п+1 выходных шин. Каждая группа элементов И содержит по два элемента И, а i-я (,2...,n-1) группа элементов 2-2Ц-2ИЛИ содержит i элементов 2-2И-2ИЛИ. Первая информационная шина модуля соединена с входом первого элемента НЕ, выход которого соединен с первым входом первого элемента И первой группы и первым входом элемента 2-2И-2ИЛИ первой группы, вто- рой вход которого соединен с первым входом второго элемента И первой группы и входом первого элемента НЕ. Выход k-ro (,2) элемента И j-й (,2,...,n-2) группы соединен с первым входом k-ro элемента И (+1)-й группы и первым входом (J+k j+1)-ro элемента 2-2И-2ИЛИ (1+1)-й группы. Выход

t-го (,2,.,.,j) элемента 2-2И-2ИЛИ j-й группы соединен с вторым входом t-ro элемента 2-2И-2ИЛИ (+1)-й группы и первым входом (t+1)-ro элемента 2-2И-2ИЛИ 0+1)-й

группы. Причем (1+1)-я информационная шина модуля соединена с третьим входом s-ro (,2,...,l) элемента 2-2И-2ИЛИ 1-й группы, вторым входом второго элемента И 1-й группы и входом (1+1)-го элемента НЕ, выход

которого соединен с вторым входом первого элемента И -й группы и четвертым входом s-ro элемента 2-2Й-2ИЛИ 1-й группы, Выход элемента И (п-1)-й группы соединен с (k- п-п+1)-й выходной шиной модуля, 1-я

выходная шина которого соединена с выходом i-ro элемента 2-2И-2ИЛИ (п-1)-й группы.

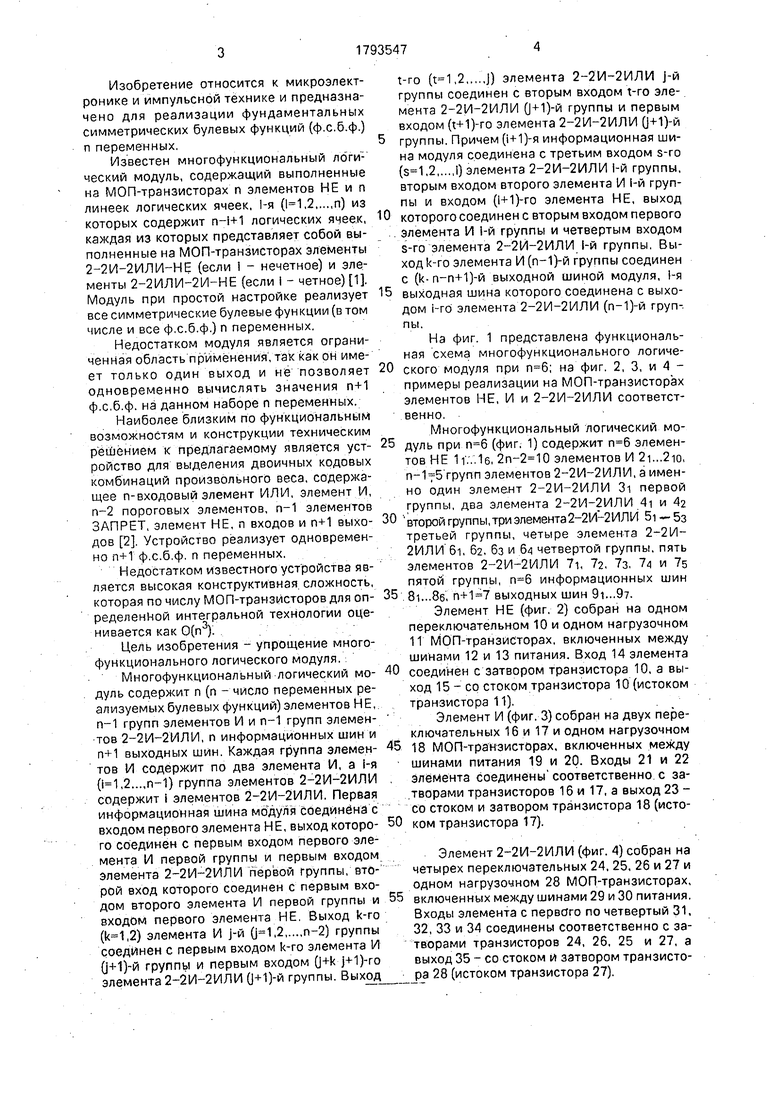

На фиг. 1 представлена функциональная схема многофункционального логического модуля при на фиг. 2, 3, и 4 - примеры реализации на МОП-транзисторах элементов НЕ, И и 2-2И-2ИЛИ соответственно.

Многофункциональный логический модуль при (фиг. 1) содержит элементов НЕ Н..Иб, элементов И 2i...2io, п-1 5 групп элементов 2-2И-2ИЛИ, а именно один элеме-нт 2-2И-2ИЛИ Зч первой группы, два элемента 2-2И-2ИЛИ 4i и 42

второй группы,три элемента2-2И-2ИЛИ 5i -5з третьей группы, четыре элемента 2-2И- 2ИЛИ 6i. 62. 63 и 64 четвертой группы, пять элементов 2-2И-2ИЛИ 7i, 72, 7з, 7А и 7s пятой группы, информационных шин

8i...86, выходных шин 9i...9.

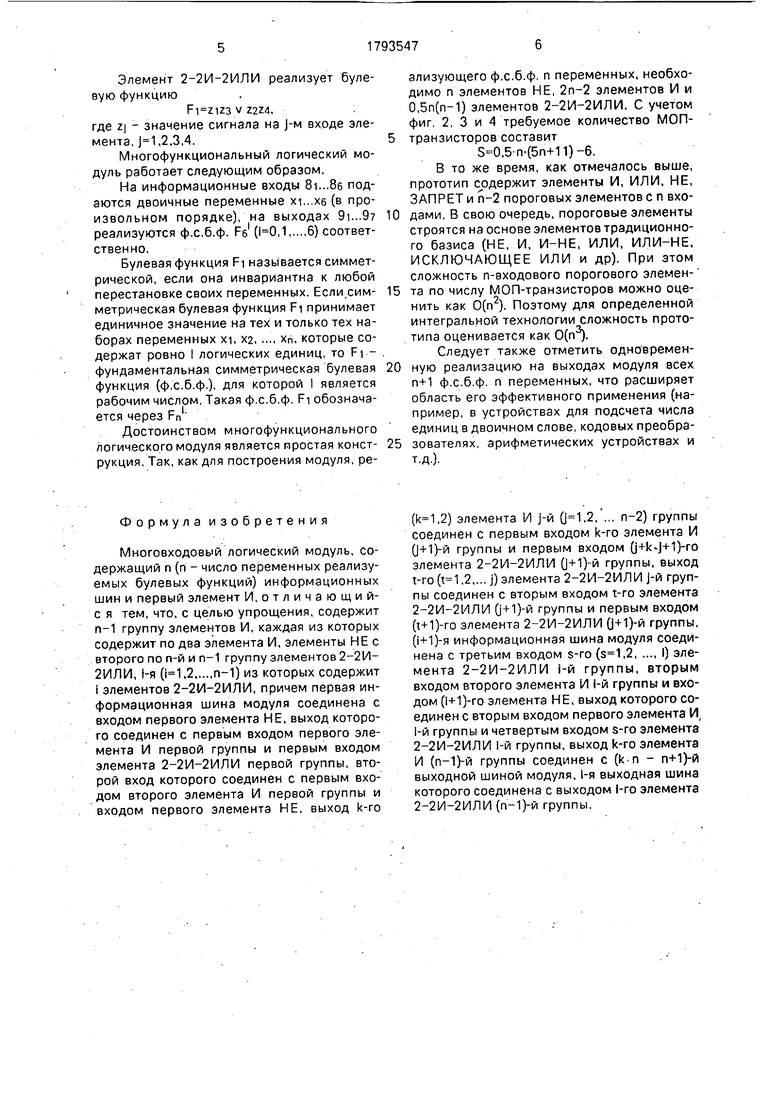

Элемент НЕ (фиг. 2) собран на одном переключательном 10 и одном нагрузочном 11 МОП-транзисторах, включенных между шинами 12 и 13 питания. Вход 14 элемента

соединен с затвором транзистора 10, а выход 15 - со стоком транзистора 10 (истоком транзистора 11).

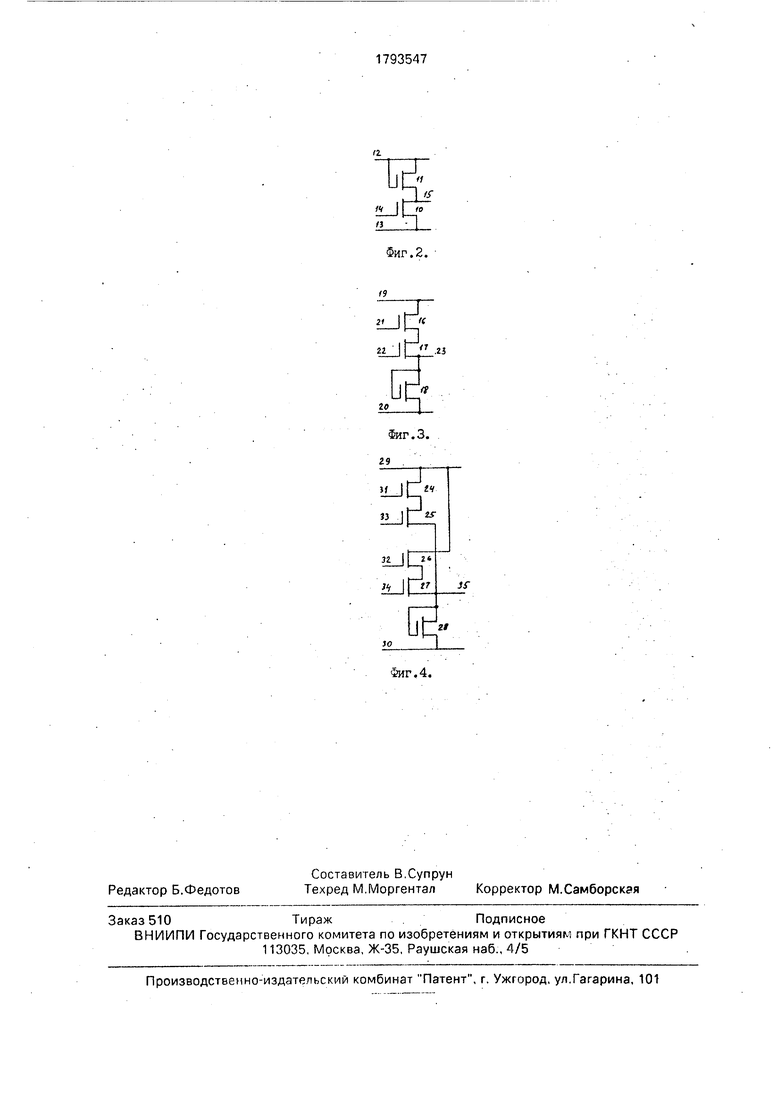

Элемент И (фиг. 3) собран на двух переключательных 16 и 17 и одном нагрузочном

18 МОП-транзисторах, включенных между шинами питания 19 и 20. Входы 21 и 22 элемента соединены соответственно, с за- дворами транзисторов 16 и 17, а выход 23 - со стоком и затвором транзистора 18 (истоком транзистора 17).

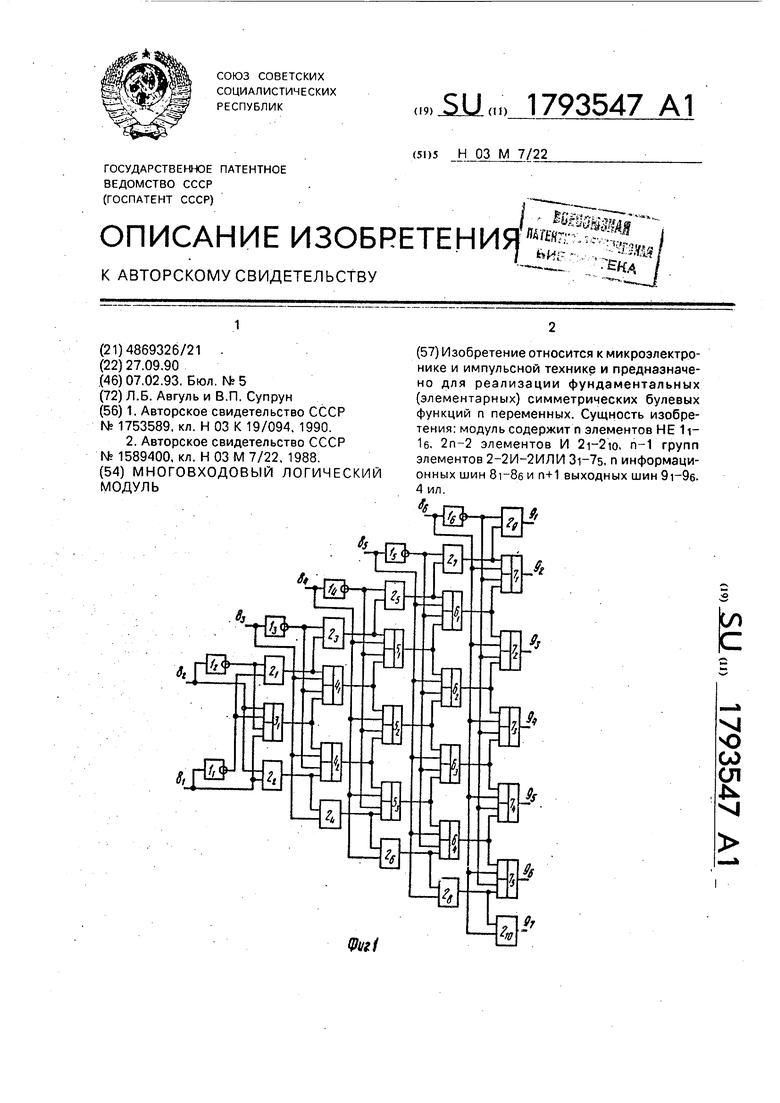

Элемент 2-2И-2ИЛИ (фиг. 4) собран на четырех переключательных 24, 25, 26 и 27 и одном нагрузочном 28 МОП-транзисторах, включенных между шинами 29 и 30 питания. Входы элемента с первого по четвертый 31, 32, 33 и 34 соединены соответственно с затворами транзисторов 24, 26, 25 и 27, а выход 35 - со стоком и затвором транзистора 28 (истоком транзистора 27).

Элемент 2-2И-2ИЛИ реализует буле- вую функцию

v Z2Z4,: где zj - значение сигнала на j-м входе элемента, ,2,3,4.

Многофункциональный логический модуль работает следующим образом.

На информационные входы 8i...86 подаются двоичные переменные xi...xe (в произвольном порядке), на выходах 9i...9 реализуются ф.с.б.ф. Fe (,1,...,6) соответственно.

Булевая функция FI называется симметрической, если она инвариантна к любой перестановке своих переменных. Если.сим- метрическая булевая функция FI принимает единичное значение на тех и только тех наборах переменных xi, Х2, .... Хр, которые содержат ровно I логических единиц, то FI - фундаментальная симметрическая булевая функция (ф.с.б.ф.), для которой I является рабочим числом. Такая ф.с.б.ф. FI обозначается через Fn

Достоинством многофункционального логического модуля является простая конструкция. Так,как для построения модуля, реализующего ф.с.б.ф. п переменных, необходимо п элементов НЕ, 2п-2 элементов И и 0,5п(п-1) элементов 2-2И-2ИЛИ. С учетом фиг. 2, 3 и А требуемое количество МОПтранзисторов составит

.5-n-(5n+11)-6.

В то же время, как отмечалось выше, прототип содержит элементы И, ИЛИ. НЕ, ЗАПРЕТ и п-2 пороговых элементов с п входами. В свою очередь, пороговые элементы строятся на основе элементов традиционного базиса (НЕ, И, И-НЕ, ИЛИ. ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ и др). При этом сложность n-входового порогового элемента по числу МОП-транзисторов можно оценить как 0(п ). Поэтому для определенной интегральной технологии сложность прототипа оценивается как 0(n j.

Следует также отметить одновременную реализацию на выходах модуля всех n-Ч ф.с.б.ф. п переменных, что расширяет область его эффективного применения (например, в устройствах для подсчета числа единиц в двоичном слове, кодовых преобразователях, арифметических устройствах и т.д.).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Устройство для вычисления фундаментальных симметрических булевых функций | 1990 |

|

SU1789978A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Устройство для полиномиального разложения симметрических булевых функций | 1988 |

|

SU1559338A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1742811A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

Изобретение относится к микроэлектронике и импульсной технике и предназначено для реализации фундаментальных (элементарных) симметрических булевых функций п переменных. Сущность изобретения: модульсодержит п элементов НЕ 1i- 1б. 2п-2 элементов И 2i-2 io, n-1 групп элементов 2-2И-2ИЛИ 3i-7s, n информационных шин 8i-8e и п+1 выходных шин 9i-9e. 4 ил. .гп г-1,,

Формула изобретения

Многовходовый логический модуль, содержащий п (п - число переменных реализуемых булевых функций) информационных шин и первый элемент И.отличающий- с я тем, что, с целью упрощения, содержит п-1 группу элементов И, каждая из которых содержит по два элемента И, элементы НЕ с второго по n-й и п-1 группу элементов 2-2И- 2ИЛИ, 1-я (,2....,п-1) из которых содержит i элементов 2-2И-2ИЛИ, причем первая информационная шина модуля соединена с входом первого элемента НЕ, выход которого соединен с первым входом первого элемента И первой группы и первым входом элемента 2-2И-2ИЛИ первой группы, второй вход которого соединен с первым входом второго элемента И первой группы и входом первого элемента НЕ. выход k-ro

(,2) элемента И j-й .2. ... п-2) группы соединен с первым входом k-ro элемента И 0+1)-й группы и первым входом (j+k«j+1)-ro элемента 2-2И-2ИЛИ 0+1)-й группы, выход t-ro (,2,... j) элемента 2-2И-2ИЛ И J-й группы соединен с вторым входом t-ro элемента 2-2И-2ИЛИ 0+1)-й группы и первым входом (t+1)-ro элемента 2-2И-2ИЛИ (j+1)-u группы, (1+1)-я информационная шина модуля соединена с третьим входом s-го (,2, ..., I) элемента 2-2И-2ИЛИ i-й группы, вторым входом второго элемента И i-й группы и входом (i+1)-ro элемента НЕ, выход которого соединен с вторым входом первого элемента И(

1-й группы и четвертым входом s-ro элемента

2-2И-2ИЛИ i-й группы, выход k-ro элемента И (п-1)-й группы соединен с (k.n - п+1)-й выходной шиной модуля, 1-я выходная шина которого соединена с выходом 1-го элемента 2-2И-2ИЛИ (п-1)-й группы.

Ж,

LJU п LФиг.2.

Фиг.З.

Фиг,4,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выделения двоичных кодовых комбинаций произвольного веса | 1988 |

|

SU1589400A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1993-02-07—Публикация

1990-09-27—Подача