1

(21)3902385/63

(22)28.05.85

(46) 15.10.91. Бюл. М-38

(72) Г.Н.Тимонькин, В.С.Харченко, С Н.Ткаченко, Г.К,Подзолов, Н.И.Хлебников.

Ю.М.Гнедовский, Е.Е.Миневич и А.А.Файвинов

(53)681.325(088.8)

(56) Авторское свидетельство СССР

№ 1259279, кл. G 06 F 15/16, 1985.

Авторское свидетельство СССР № 734657,кл. G 06 F 3/04, 1978

(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

(57) Изобретение относится к цифровой вычислительной технике и может быть использовано для управления синхронизацией думлек- снойСчвухканальной) вычислительной системы Цель изобретения - повышение надежности и расширение области применения Устройство для синхронизации вычислительной системы содержит первый канал, включающий блок задания режима, блок асинхронной связи и генератор импульсов, а также второй канал При этом в каждый копал введены блок контроля времени связи, блок синхронного пуска, блок управления синхронизацией, блок приостановэ и распределитель тактовых импульсов 9 ил 2 )эбл

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Устройство для синхронизации каналов | 1985 |

|

SU1262471A1 |

| Конвейерная система для программного управления | 1989 |

|

SU1665340A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для программного управления | 1989 |

|

SU1700537A1 |

| Устройство для управления с контролем | 1983 |

|

SU1156074A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Трехканальное резервированное устройство для синхронизации сигналов | 1988 |

|

SU1709316A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления синхронизацией дуплексной (двухканальной) вычислительной системы.

Цель изобретения - повышение надежности и расширение области применения.

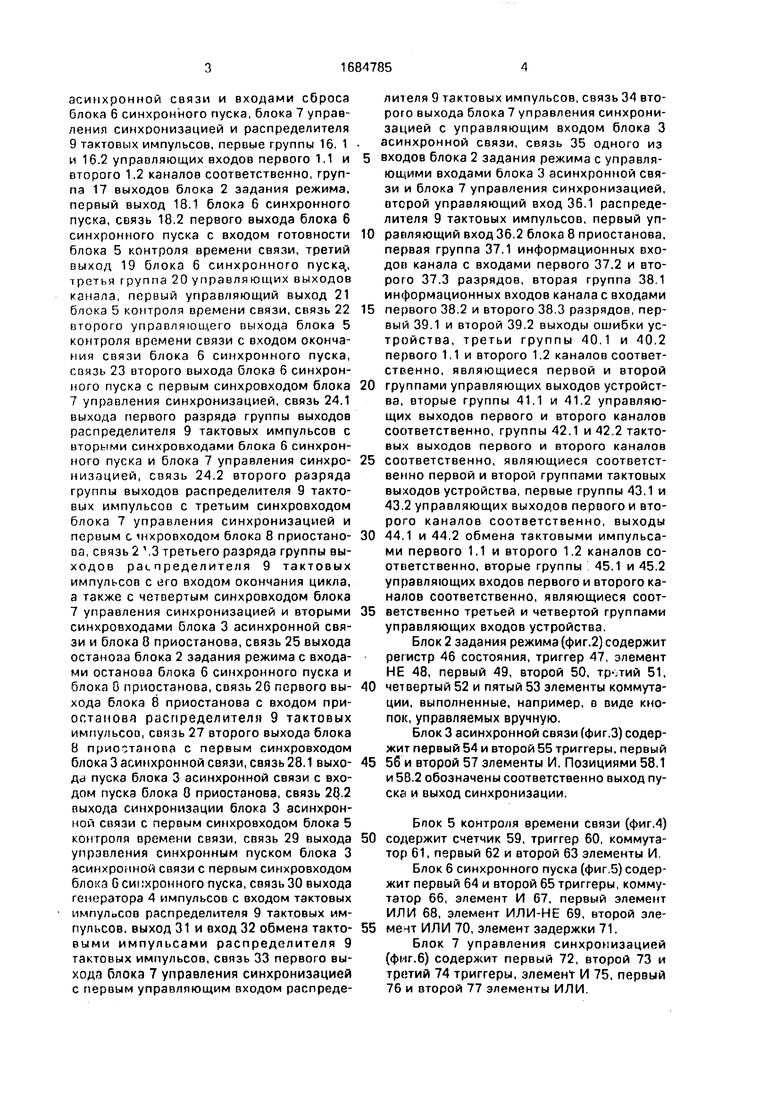

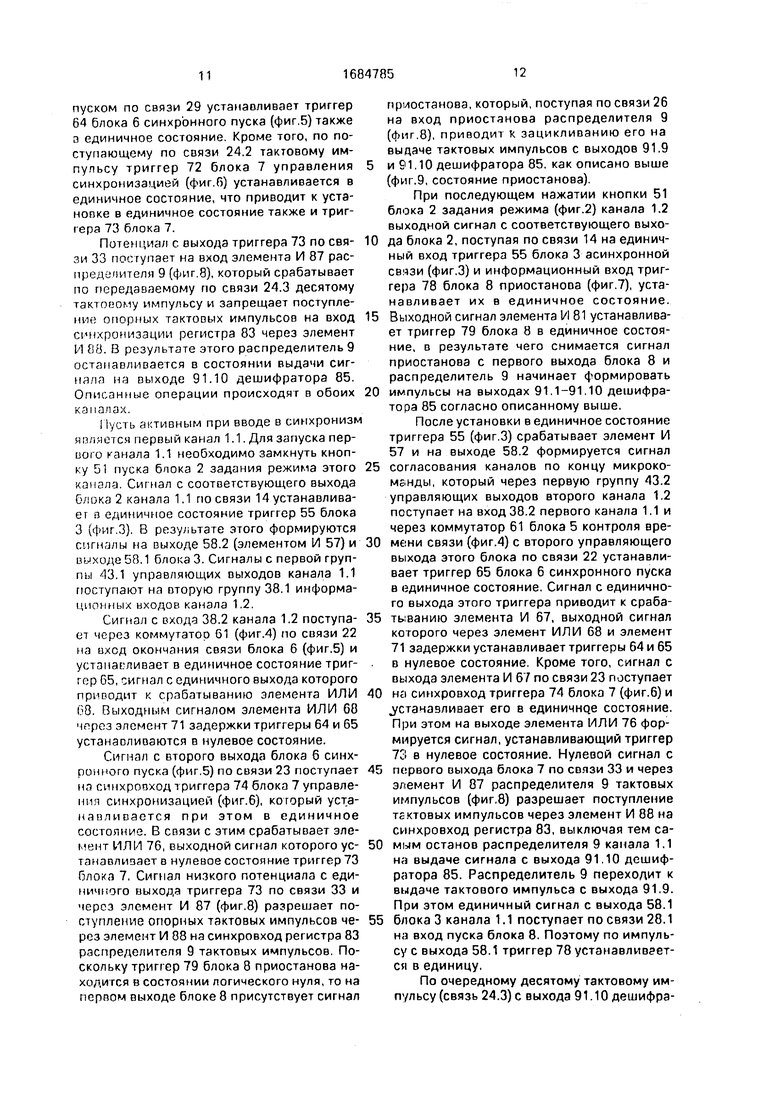

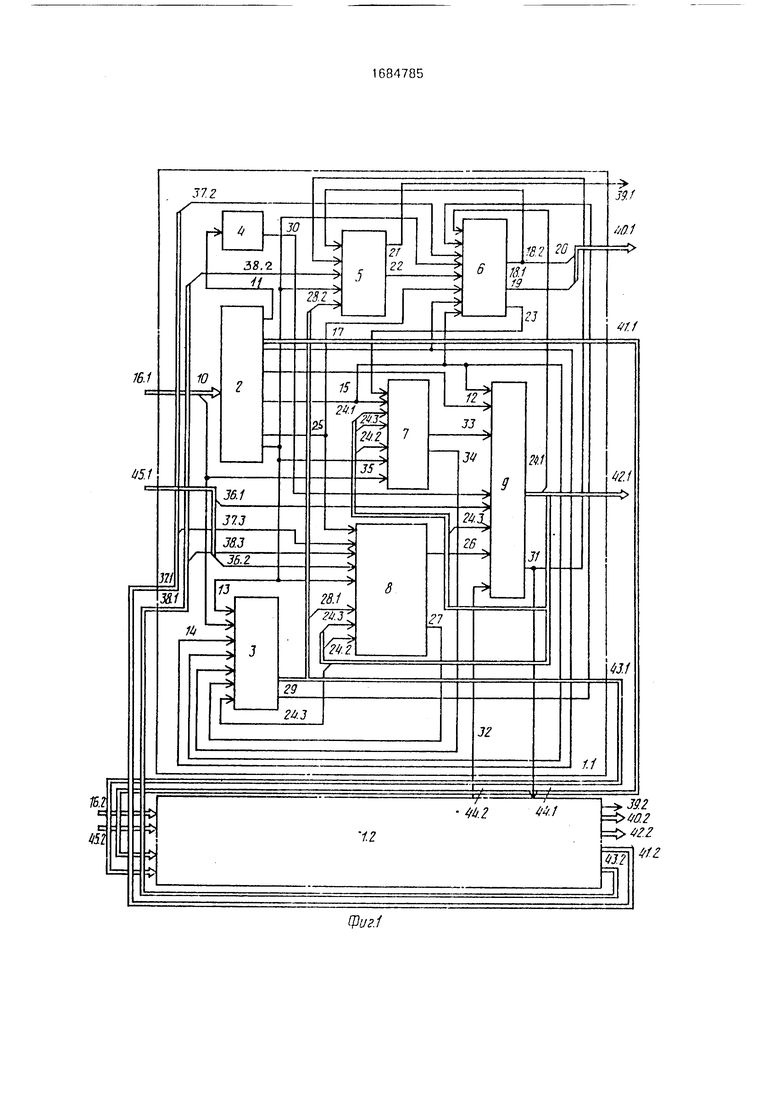

На фиг.1 приведена структурная схема устройства; на фиг.2-8 - функциональные схемы блоков задания режима, асинхронной связи, контроля времени связи, синхронного пуска, управления синхронизацией, приостанова и распределителя тактовых импульсов соответственно: на фиг.9 - временные диаграммы работы распределителя тактовых импульсов

На фиг.1 обозначены первый канал 1.1 и второй канал 1.2, каждый канал включает блок 2 задания режима, блок 3 асинхронной связи, генератор 4 импульсов, блок 5 контроля времени связи, блок 6 синхронною пуска, блок 7 управления синхронизацией,

сл

с

блок 8 приостанова, распределитель 9 .актовых импульсов, входы 10 блока 2 задания режима, связь 11 нерпою пуска блока 2 задания режима с входом генератора 4 импульопв, связь 12 выхода выбора тактовых импульсов блока 2 задания режима с входом выбора тактовых им пульсов распределителя 9 тактовых импульсов, связь 13 выхода синхронного режима блока 2 задания режима с первым управляющим входом блока 3 асинхронной связи и входами синхронного режима блока 5 контроля времени связи блока б синхронного пуска блока 7 управления синхронизацией и В приостанови связь 14 второго пуска блока 2 задания режима с нгорым управляющим входом блока 3 асинхронной связи и с входом пуска блока 6 синхронною . связь 15 выхода сброса блока 2 задания режима с третьим управляющим входом блока 3

о с

U J 00 СЛ

:

асинхронной связи и входами сброса блока 6 синхронного пуска, блока 7 управления синхронизацией и распределителя 9 тактовых импульсов, первые группы 16. 1 и 16.2 управляющих входов первого 1.1 и второго 1.2 каналов соответственно, группа 17 выходов блока 2 задания режима, первый выход 18.1 блока 6 синхронного пуска, связь 18.2 первого выхода блока 6 синхронного пуска с входом готовности блока 5 контроля времени связи, третий выход 19 блока 6 синхронного пуска,, третья группа 20 управляющих выходов канала, первый управляющий выход 21 блока 5 контроля времени связи, связь 22 второго управляющего выхода блока 5 контроля времени связи с входом окончания связи блока 6 синхронного пуска, связь 23 второго выхода блока 6 синхронного пуска с первым синхровходом блока 7 управления синхронизацией, связь 24.1 выхода первого разряда группы выходов распределителя 9 тактовых импульсов с вторыми синхровходами блока 6 синхронного пуска и блока 7 управления синхронизацией, связь 24.2 второго разряда группы выходов распределителя 9 тактовых импульсов с третьим синхровходом блока 7 управления синхронизацией и первым с шхровходом блока 8 приостано- оа, связь 2 3 третьего разряда группы выходов рас. пределителя 9 тактовых импульсов с его входом окончания цикла, а также с четвертым синхровходом блока

7управления синхронизацией и вторыми синхровходами блока 3 асинхронной связи и блока 8 приостанова,связь 25 выхода останова блока 2 задания режима с входами останова блока б синхронного пуска и блока 0 приостанова, связь 26 первого выхода блока 8 прмостанова с входом приостанови распределителя 9 тактовых импульсов, связь 27 второго выхода блока

8приоотанова с первым синхровходом блока 3 асинхронной связи, связь 28.1 выхода пуска блока 3 асинхронной связи с входом пуска блока 8 приостанова, связь 28.2 выхода синхронизации блока 3 асинхронной связи с первым синхровходом блока 5 контроля времени связи, связь 29 выхода управления синхронным пуском блока 3 асинхронной связи с первым синхровходом блока 6 CHI:хронного пуска, связь 30 выхода генератора 4 импульсов с входом тактовых импульсов распределителя 9 тактовых импульсов, выход 31 и вход 32 обмена тактовыми импульсами распределителя 9 тактовых импульсов, связь 33 первого выхода блока 7 управления синхронизацией с первым управляющим входом распределителя 9 тактовых импульсов, связь 34 второго выхода блока 7 управления синхронизацией с управляющим входом блока 3 асинхронной связи, связь 35 одного из

входов блока 2 задания режима с управляющими входами блока 3 асинхронной связи и блока 7 управления синхронизацией, второй управляющий вход 36.1 распределителя 9 тактовых импульсов, первый управляющий вход 36,2 блока 8 приостанова. первая группа 37.1 информационных входов канала с входами первого 37.2 и второго 37.3 разрядов, вторая группа 38.1 информационных входов канала с входами

первого 38.2 и второго 38.3 разрядов, первый 39.1 и второй 39.2 выходы ошибки устройства, третьи группы 40.1 и 40.2 первого 1,1 и второго 1.2 каналов соответственно, являющиеся первой и второй

группами управляющих выходов устройства, вторые группы 41.1 и 41.2 управляющих выходов первого и второго каналов соответственно, группы 42.1 и 42.2 тактовых выходов первого и второго каналов

соответственно, являющиеся соответственно первой и второй группами тактовых выходов устройства, первые группы 43.1 и 43.2 управляющих выходов первого и второго каналов соответственно, выходы

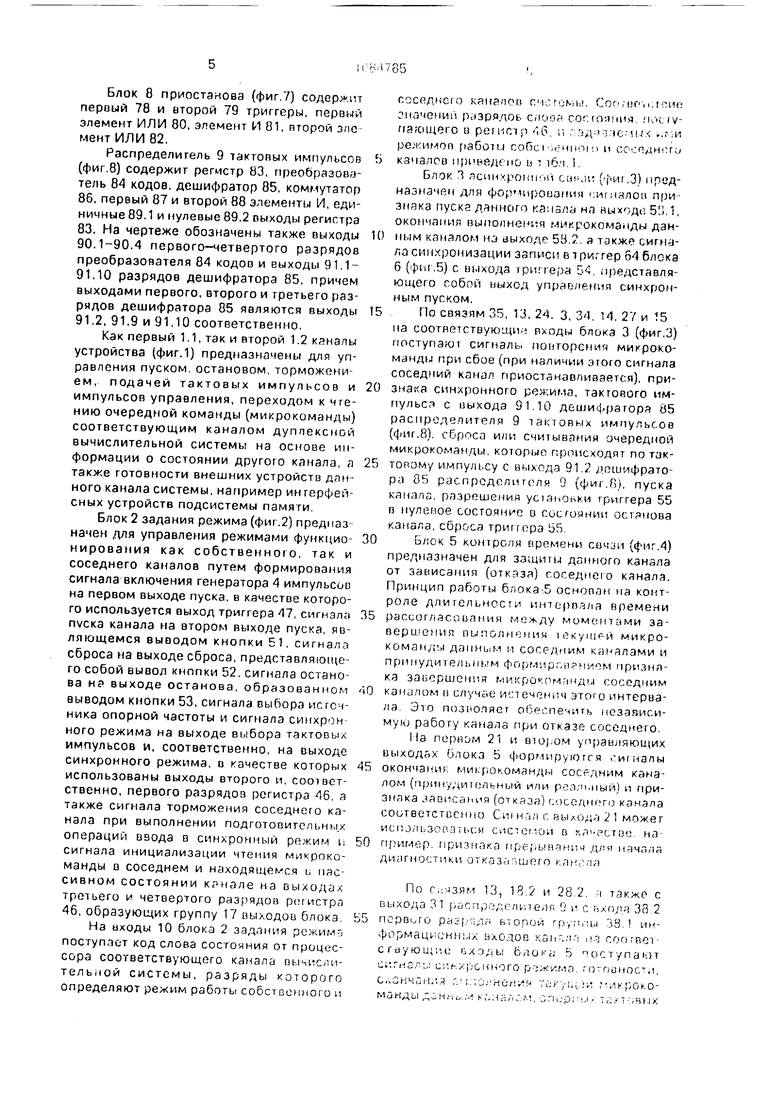

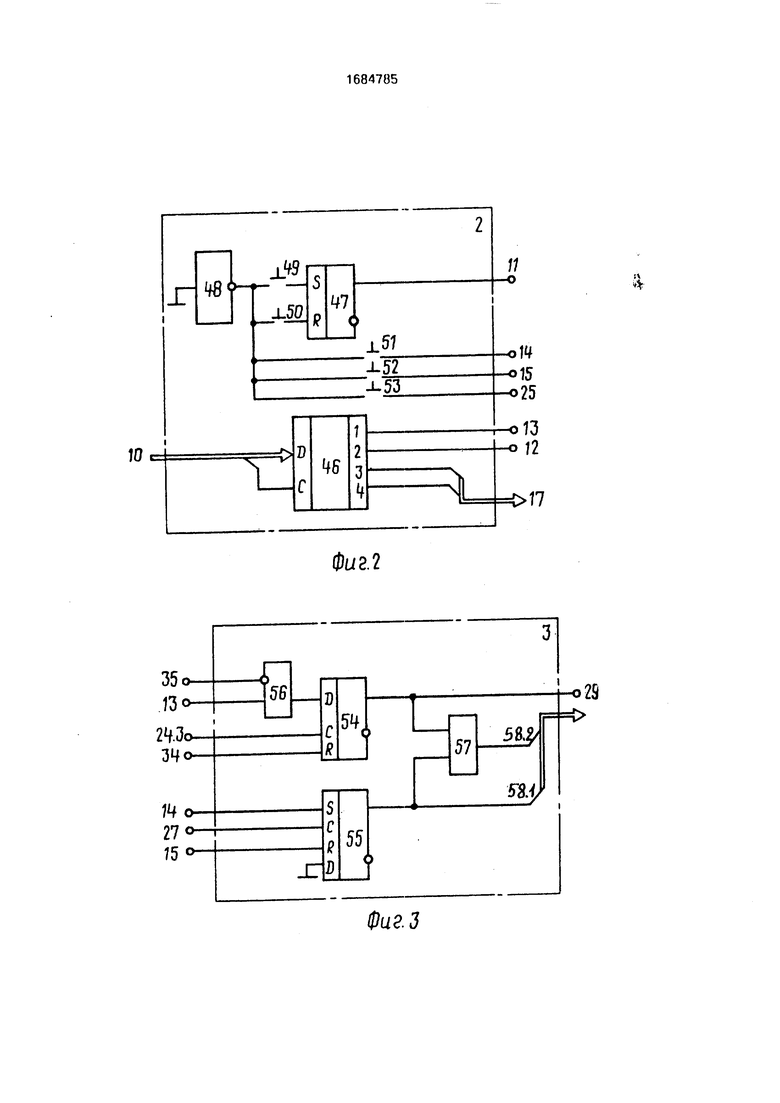

Блок 2 задания режима (фиг.2) содержит регистр 46 состояния, триггер 47, элемент НЕ 48, первый 49, второй 50, третий 51,

четвертый 52 и пятый 53 элементы коммутации, выполненные, например, в виде кнопок, управляемых вручную.

Блок 3 асинхронной связи (фиг.З) содержит первый 54 и второй 55 триггеры, первый

56 и второй 57 элементы И, Позициями 58.1 и 58.2 обозначены соответственно выход пуска и выход синхронизации.

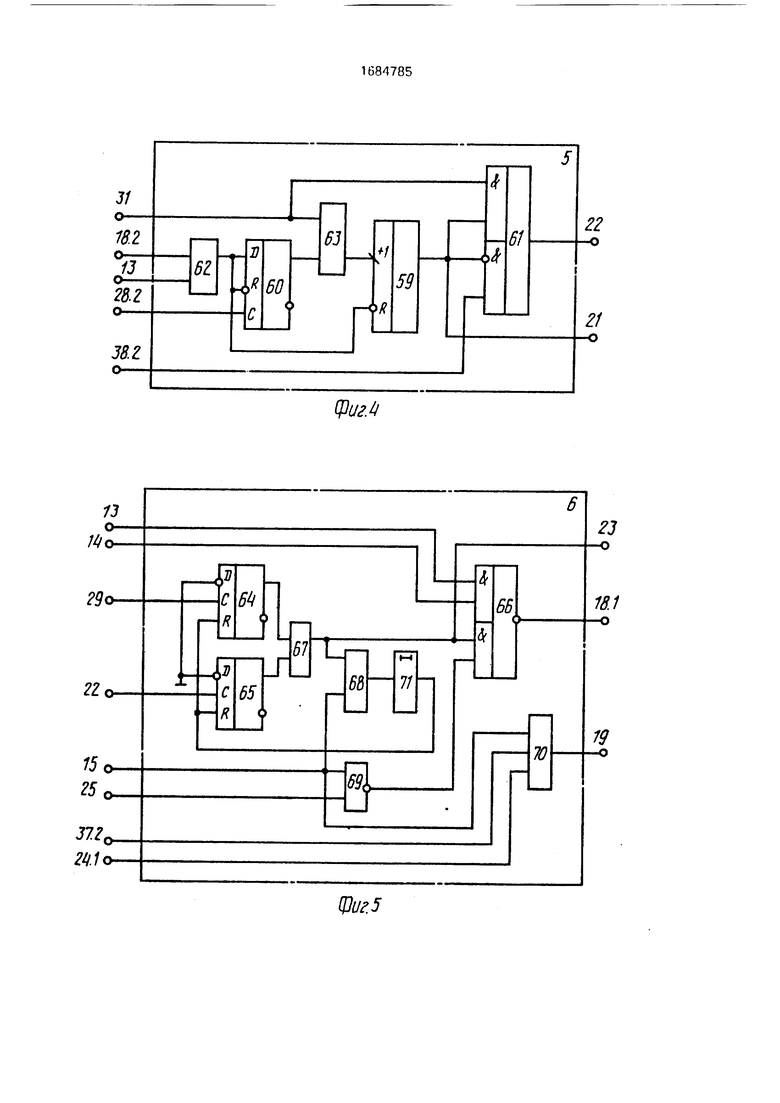

Блок 5 контроля времени связи (фиг.4) содержит счетчик 59, триггер 60, коммутатор 61, первый 62 и второй 63 элементы И. Блок 6 синхронного пуска (фиг.5) содержит первый 64 и второй 65 триггеры, коммутатор 66, элемент И 67, первый элемент ИЛИ 68, элемент ИЛИ-НЕ 69, второй эле- мент ИЛИ 70, элемент задержки 71.

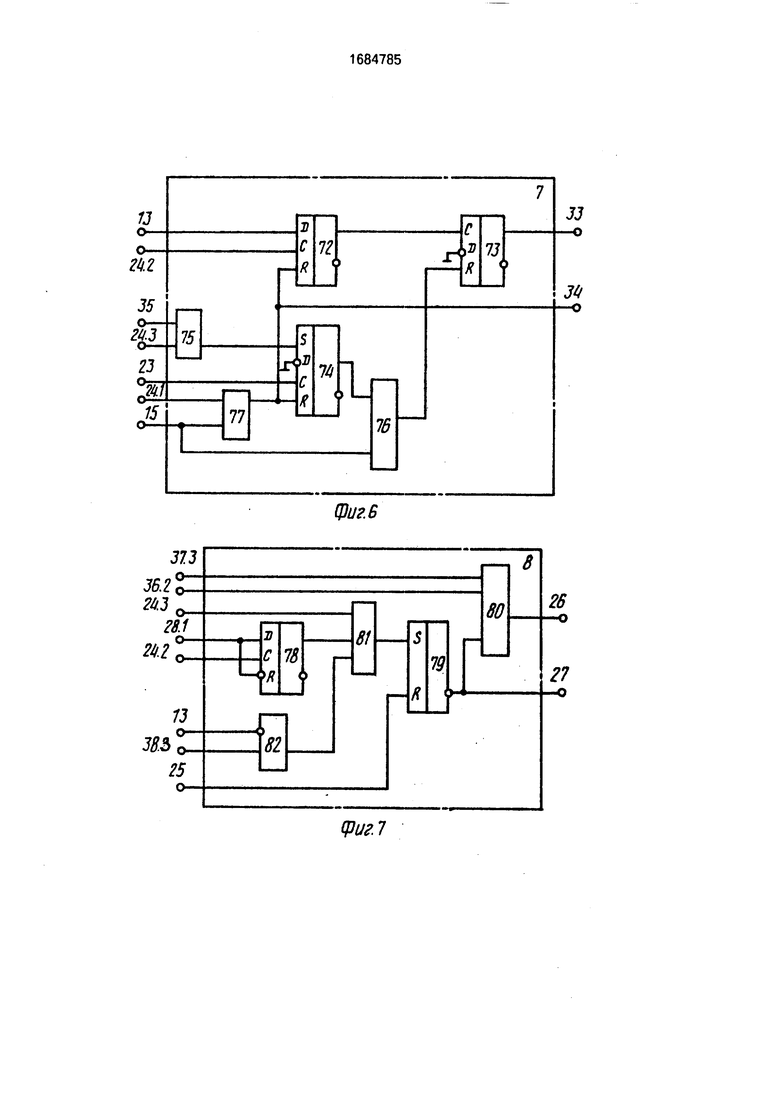

Блок 7 управления синхронизацией (фиг.6) содержит первый 72, второй 73 и третий 74 триггеры, элемент И 75, первый 76 и второй 77 элементы ИЛИ.

Блок 8 приостанова (фиг.7) содержит первый 78 и второй 79 триггеры, первый элемент ИЛИ 80, элемент И 81, нторой зле мент ИЛИ 82.

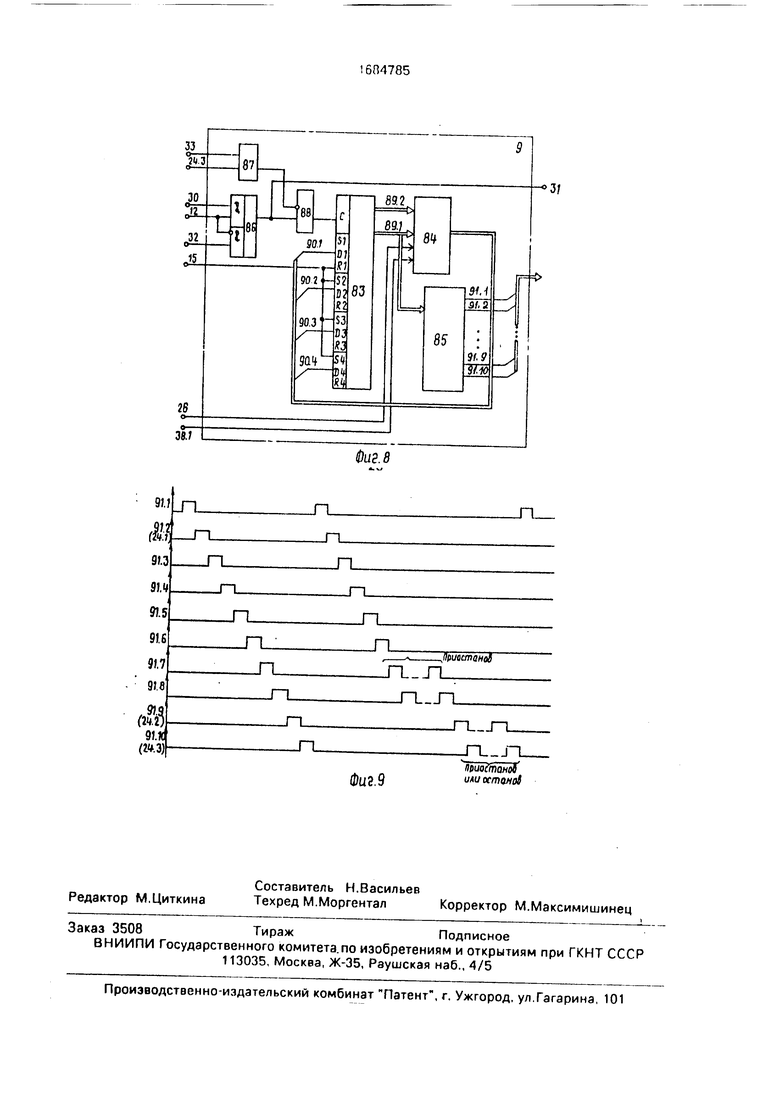

Распределитель 9 тактовых импульсов (фиг.8) содержит регистр 83, преобразователь 84 кодов, дешифратор 85, коммутатор 86, первый 87 и второй 88 элементы И, единичные 89.1 и нулевые 89.2 выходы регистра 83. На чертеже обозначены также выходы 90.1-90.4 первого-четвертого разрядов преобразователя 84 кодоо и выходы 91.1- 91.10 разрядов дешифратора 85, причем выходами первого, второго и третьего разрядов дешифратора 85 являются выходы 91,2, 91.9 и 91.10 соответственно.

Как первый 1.1, так и второй 1.2 каналы устройства (фиг.1) предназначены для управления пуском остановом, торможением, подачей тактовых импульсов и импульсов управления, переходом к чтению очередной команды (микрокоманды) соответствующим каналом дуплексной вычислительной системы на основе информации о состоянии другого канала, а также готовности внешних устройств данного канала системы, например интерфейсных устройств подсистемы памяти

Блок 2 задания режима (фиг.2) предназ начен для управления режимами функционирования как собственного, так и соседнего каналов путем формирования сигнала включения генератора 4 импульсив на первом выходе пуска, в качестве которого используется выход триггера 47, сигнала пуска канала на втором выходе пуска, являющемся выводом кнопки 51, сигнала сброса на выходе сброса, представляющего собой вывод кнопки 52, сигнала останова н выходе останова, образованном выводом кнопки 53, сигнала выбора него i- ника опорной частоты и сигнала синхрон ного режима на выходе выбора тактовых импульсов и, соответственно, на выходе синхронного режима, в качестве которых использованы выходы второго и, соответственно, первого разрядов регистра 46, я также сигнала торможения соседнего канала при выполнении подготовительны/ операций ввода в синхронный режим L. сигнала инициализации чтения микрокоманды в соседнем и находящееся ь массивном состоянии крнале на выходах третьего и четвертого разрядов регистра 46, образующих группу 17 выходов блока

На иходы 10 блока 2 задания режим поступает код слова состояния от процессора соответствующего канала вычислительной системы, разряды которого определяют режим работы собственного и

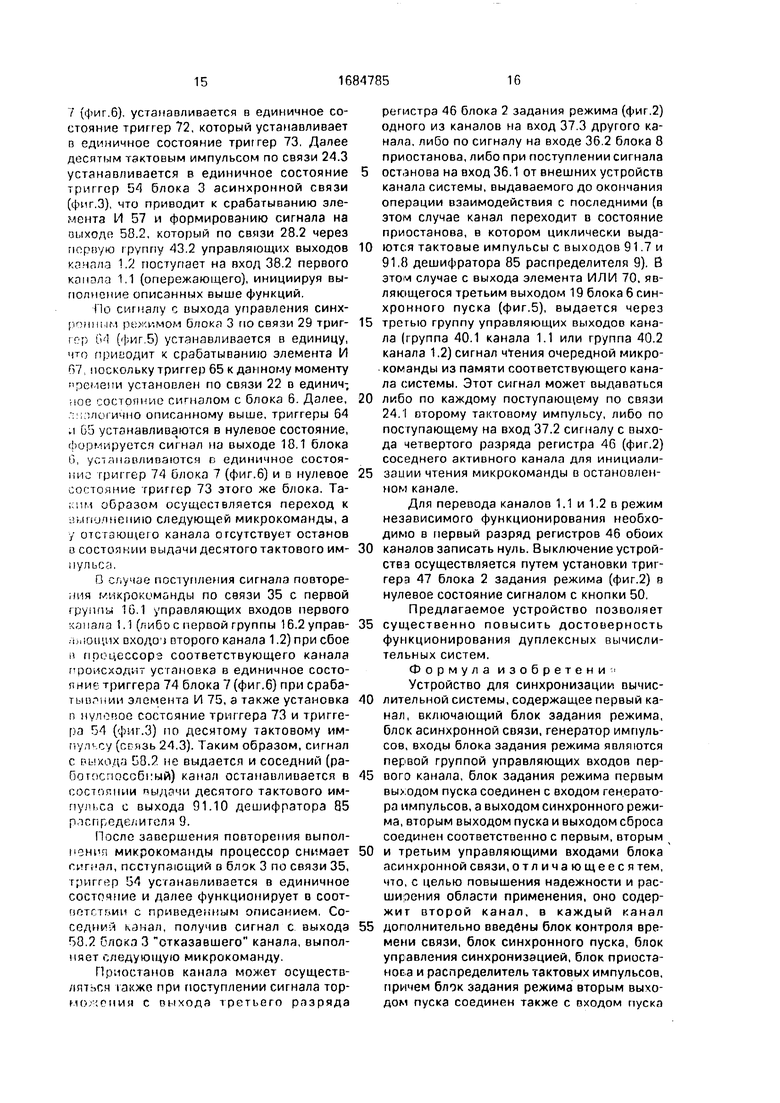

СОСРДНСЮ каналов пк-г JN.H Согмцрп значении раэрядоь слоп соггоячия ;кч iv мающего о регистр 413 и u-к .. и режимов работы собс. i ,г-нно| и

кзчалов иринедс но и т бч 1

Блок 3 лсин ронпчи cu -jH (фиг.З) предназначен для формирования ипилоп при знака пуска данного капали на пыходг. 5 1, окончания выполнения микрокоманды данмим каналом на йыходе 58 а также сигала синхронизации записи в триггер 64 блока б (Јы,5) с выхода фиггерл 54 представляющею гобой выход управления синхронным пуском.

По связям 35, 13. 24. 3, 34, 14, 27 и 15

на соответствующие входы блока 3 (фиг.З) поступаю сигналы повторения микрокоманды при сбое (при наличии этого сигнала соседний канал приостанавливается), признака синхронного режима, тактового импульса с выхода 91 10 дешифратора 65 распределителя 9 тактовых импульсов (фи1.8) сброса или считывании очередной микрокоманды которые происходят по такюпому импульсу с выхода 91 2 дешифратора 05 распределителя 9 (фиг 0). пуска канала, разрешения установки триггера 55 п нулепое состояние о состоянии останова канала, сброса триггера Ь5

Блок 5 контроля времени CBMJH (фиг.4)

предназначен для защиты данного канала от зависания (отказа) соседнею канала. Принцип работы блока 5 основан па контроле длительности интервала времени

рассогласования между моментами за- вершения пи пол нения искушен микрокоманды данным и соседним каналами и принудительпым формирг, признака завершения микрокоманды соседним

канилом и случае истечении этого интервала Это позволяет обеспечить независимую работу канала при отказе соседнего

На первом 21 и BTOJOM управляющих выходах блока 5 формируются сигналы

ОКОНЧЗНИ5 микрокоманды соседним каналом (принудительный или Р - О п.ныи) и признака зависания (о кязгз) (,)сел,нгт(3 качала соответственно Cnn-n/i г выхода 21 может исиользопз i ьс.я 1,истопои гз КЛ РСТВО на

пример признака прс рынчни д/ я (ычо/ia диагностики откаэ ШРГО лнсма

По г, -1зям 13, 18 2 и 28 2 i также с выхода 31 рчспродсл теля - и с ЬАОДЧ 38 2 первого pd ui ь-,опои rp,,, bi ни- формац1 с;нш,1л ьлотов чзь. i гоогвот с г в у ю и; но Ьли1с; Ь п ост/па ют о. ,UiHoro р j/к/ма го-оонос.1

С СНЧСН,,- i , . riuf .-1 ь U. ,.Л()ОЮманды .-.о , t.:. K-/Iс f О ь,р, M.TI. - /вн/

импульсов и окончания выполнения текущей микрокоманды соседним каналом,

Блок 6 синхронного пуска (фиг. 5) предназначен для формирования сигналов готовности на выходе 18.1 и разрешения чтения очередной микрокоманды на выходе 19. Сигнал с второго выхода блока 6, т.е. с выхода элемента И 67, по связи 23 передается на соответствующий вход блока 7 (фиг.6) и используется для синхронизации записи в триггер 74.

По связям 13, 14, 29, 22, 15, 25 и 24.1, а также с входа 37.2 первой группы 37.1 информационных входов канала на соответствующие входы блока 6 поступают сигналы признака синхронного режима, муска канала, синхронизации записи в триггер 64, окончания выполнения микрокоманды соседним каналом,сброса, останова, тактового импульса с выхода 91.2 дешифратора 85 распределителя 9 (фиг.8) и инициализации чтения микрокоманды в данном (пассивном) канале.

Элемент71 предназначен для задержки сигнала сброса триггеров 64 и 65 на время, достаточное для установки в единичное состояние триггера 60 (фиг.4) по сигналу с выхода элемента И 67, коммутатора 66 и элемента И 62 и для установки триггера 74 блока 7 (фиг.6).

Блок 7 управления синхронизацией (фиг.6) предназначен для формирования сигналов запрета подачи тактовых импульсов на синхровход регистра 83 распределителя 9 (фиг.8) с первого выхода блока до окончания выполнения текущей микрокоманды соседним каналом и для сброса триггера 54 блока 3 (фиг.З) сигналом с второго выхода блока 7, т.е. сигналом, формируемым элементом ИЛИ 77 и передаваемым по связи 34.

По связям 13, 15,23,24.1,24.2,24.3и35 на соответствующие входы блока 7 поступают сигналы синхронного режима, сброса, синхронизации записи в триггер 74 и тактовых импульсов с выходов 91.2, 91.9 и 91.10 дешифратора 85 распределителя 9 тактовых импульсов, а также сигнал повторения микрокоманды в канале при сбое.

Блок 8 приостанова (фиг.7) предназначен для формирования сигнала приостанова распределителя 9 тактовых импульсов, вырабатываемого элементом ИЛИ 80 и передаваемого по связи 26, и сигнала разрешения записи в триггер 55 блока 3 (фиг.З), вырабатываемого на инверсном выходе триггера 79 и передаваемого по связи 27.

На один из входов элемента ИЛИ 80 с пхода 37.3 канала поступает сигнал торможения от соседнего канала на время выполнения подготовительных операций по вводу данного канала в синхронный режим работы.

Вход 36.2 блока 8 предназначен для

подачи сигнала торможения канала от интерфейса с памятью соответствующего канала вычислительной системы до момента окончания операции взаимодействия с ней.

0 Третий управляющий вход блока 8 приостанова, т.е. прямой вход элемента ИЛИ 82, подключенный к входу 38.3 канала, предназначен для подачи сигнала признака пуска соседнего канала (перехода его в

5 активное состояние).

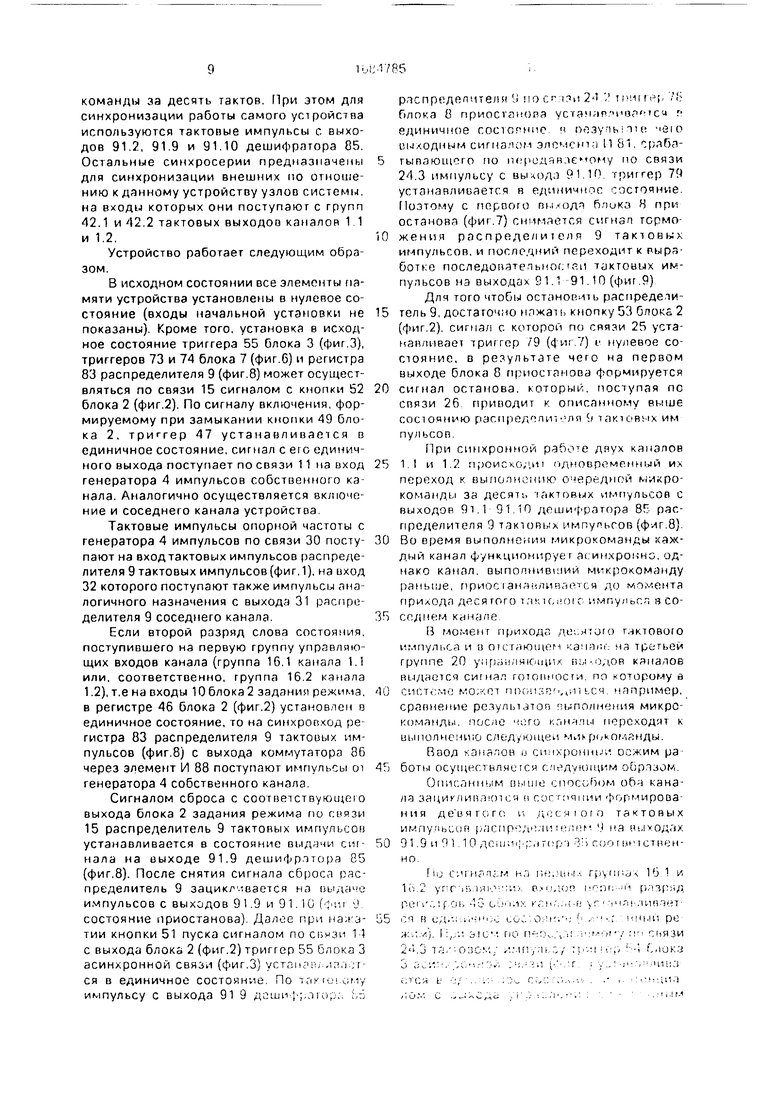

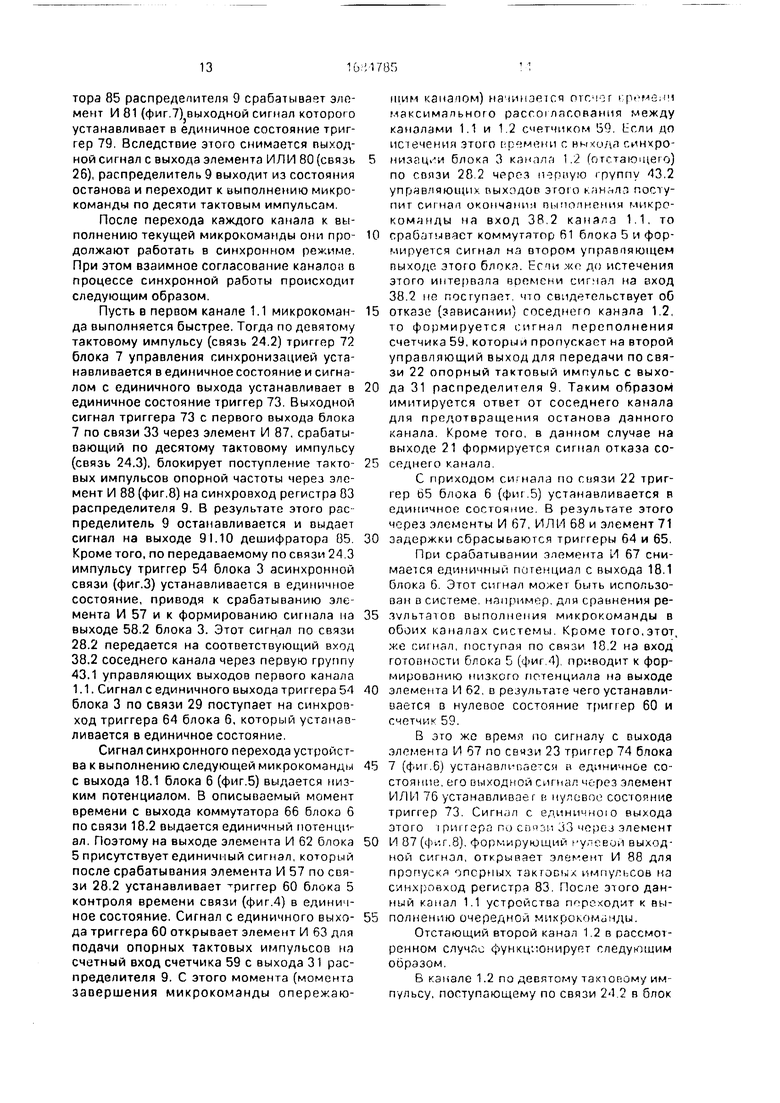

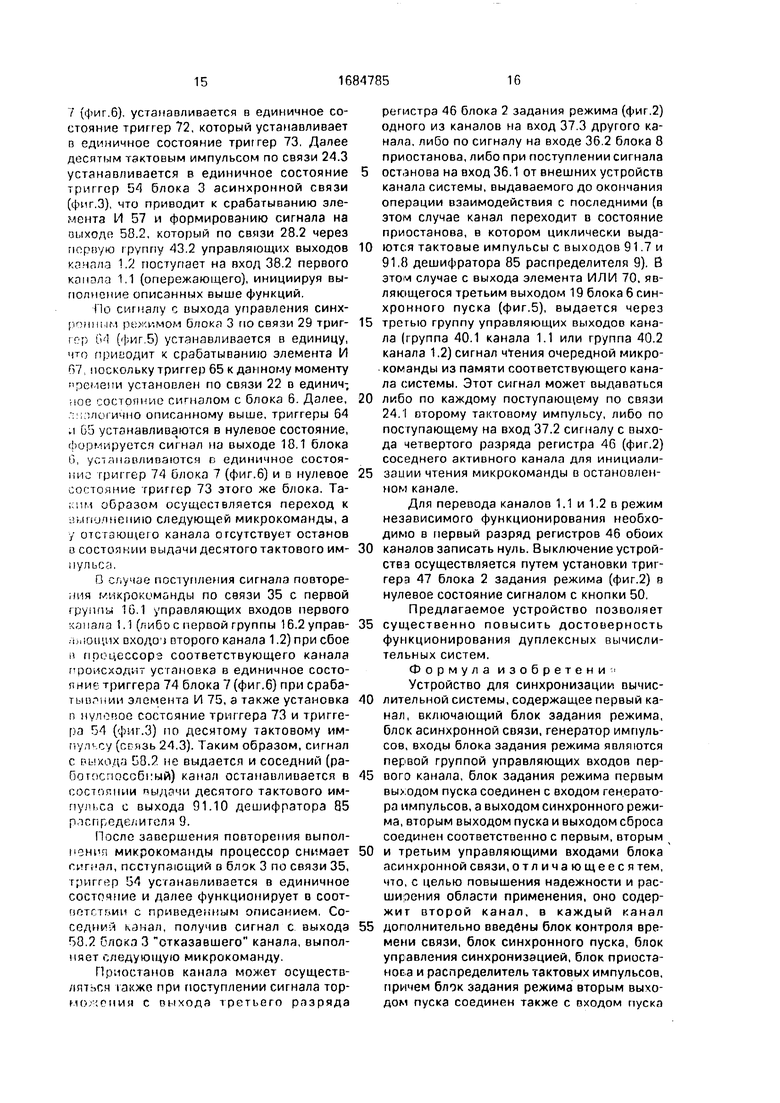

Распределитель 9 тактовых импульсов (фиг.8) предназначен для выдачи импульсов опорной частоты на выходе 31 и тактовой сетки импульсов на выходах 91.1-91.10 де0 шифратора 85, образующих группу 42.1 так- тоных выходов первого канала 1.1 (соответственно группу 42.2 тактовых выходов второго канала 1.2). Временная диаграмма сигналов на выходах 91.1-91.10

5 представлена на фиг.9.

Синхронизация распределителя 9 тактовых импульсов осуществляется через коммутатор 86, управляемый поступающим по связи 12 сигналом от блока 2 задания режи0 ма, опорными тактовыми импульсами, поступающими либо по связи 30 с генератора 4 импульсов собственного канала, либо на вход 32 с выхода обмена тактовыми импульсами соседнего канала.

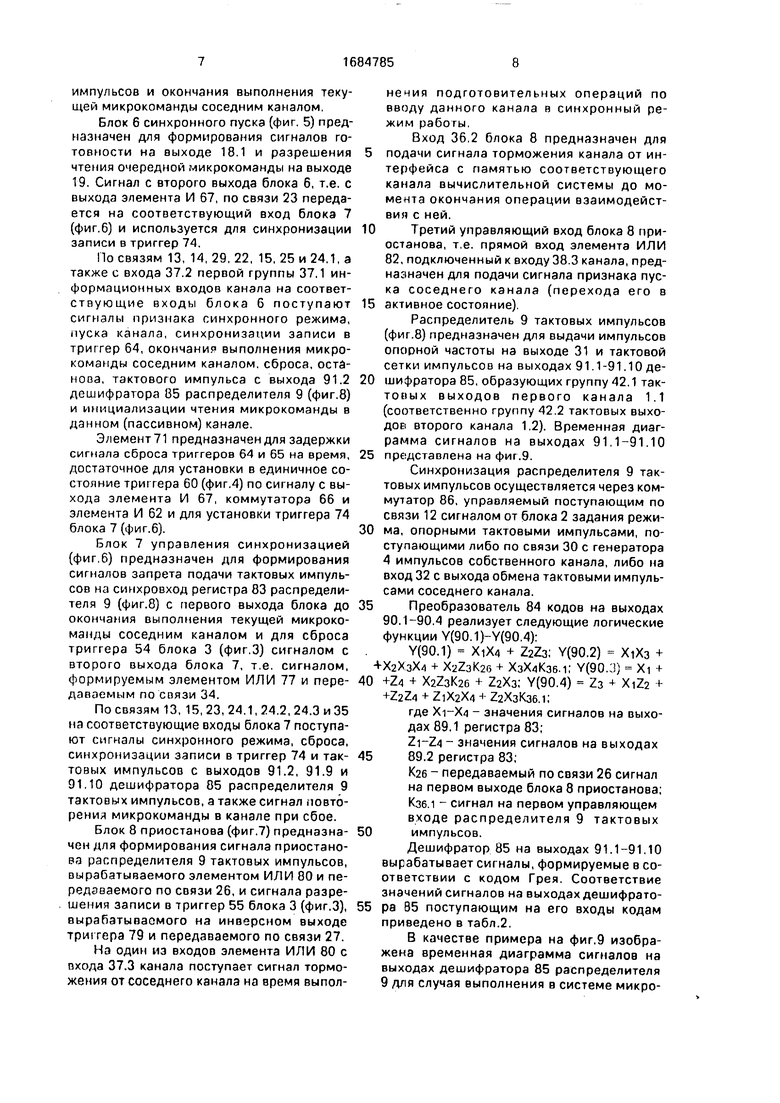

5 Преобразователь 84 кодов на выходах 90.1-90.4 реализует следующие логические функции Y(90.1)-Y(90.4):

Y(90.1) XiX4 + Z2Z3; Y(90.2) XiX3 +

4X2X3X4 + X2Z3«26 + ХзХ/)Кзб.1; Y(90.:i) Xi + 0 +ZA + XaZ3K26 + 72X3; Y(90.4) 2з + XiZ2 + +Z2Z4 + ZiX2X4 + Z2X3K36.i;

где Xi-X/i - значения сигналов на выходах 89.1 регистра 83; Zi-Z4 - значения сигналов на выходах 5 89.2 регистра 83;

К2б - передаваемый по связи 26 сигнал на первом выходе блока 8 приостанова; Кзе.1 - сигнал на первом управляющем входе распределителя 9 тактовых 0импульсов.

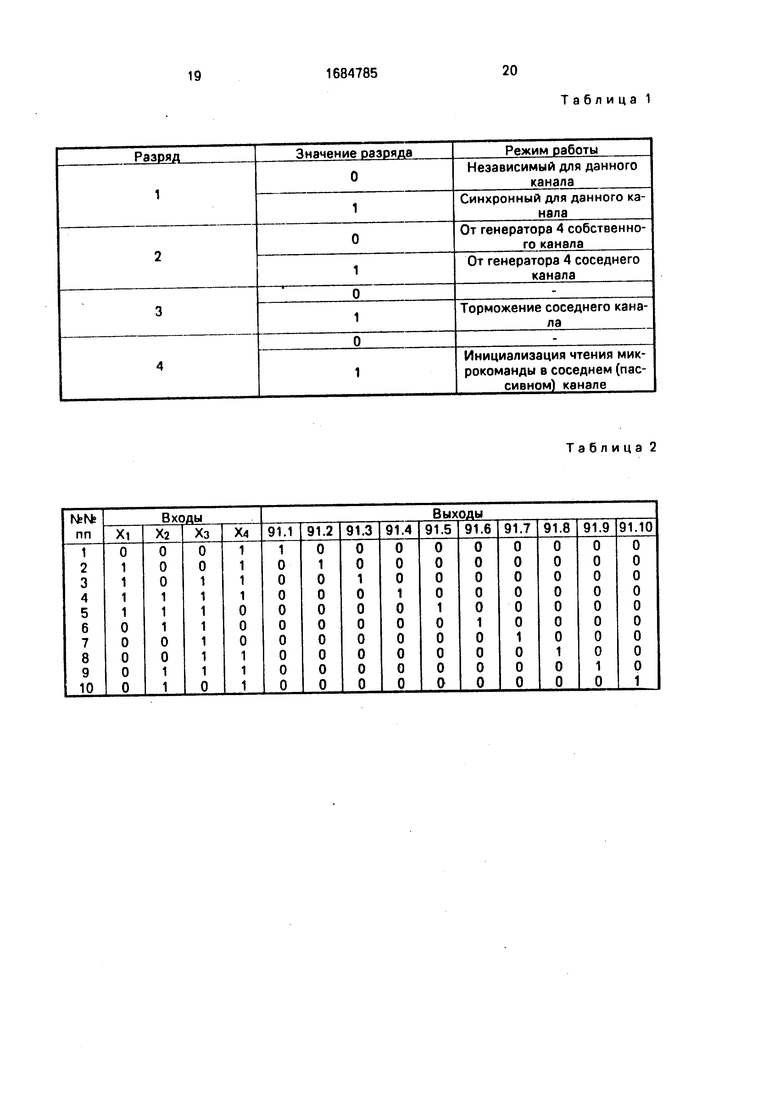

Дешифратор 85 на выходах 91.1-91.10 вырабатывает сигналы, формируемые в соответствии с кодом Грея. Соответствие значений сигналов на выходах дешифрато- 5 ра 85 поступающим на его входы кодам приведено в табл.2.

В качестве примера на фиг.9 изображена временная диаграмма сигналов на выходах дешифратора 85 распределителя 9 для случая выполнения в системе микрокоманды за десять тактов. При этом для синхронизации работы самого устройства используются тактовые импульсы с выходов 91.2, 91.9 и 91.10 дешифратора 85. Остальные синхросерии предназначены для синхронизации внешних по отношению к данному устройству узлов системы. на входы которых они поступают с групп 42.1 и 42.2 тактовых выходов каналов 1 1 и 1.2.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти устройства установлены в нулевое состояние (входы начальной установки не показаны). Кроме того, установка в исходное состояние триггера 55 блока 3 (фиг.З), триггеров 73 и 74 блока 7 (фиг.6) и регистра 83 распределителя 9 (фиг.8) может осуществляться по связи 15 сигналом с кнопки 52 блока 2 (фиг.2). По сигналу включения, формируемому при замыкании кнопки 49 блока 2, триггер 47 устанавливается в единичное состояние, сигнал с его единичного выхода поступает по связи 11 на вход генератора 4 импульсов собственного канала. Аналогично осуществляется включение и соседнего канала устройства

Тактовые импульсы опорной частоты с генератора 4 импульсов по связи 30 поступают на вход тактовых импульсов распределителя 9 тактовых импульсов (фиг. 1), на вход 32 которого поступают также импульсы аналогичного назначения с выхода 31 распределителя 9 соседнего канала.

Если второй разряд слова состояния, поступившего на первую группу управляющих входов канала (группа 16.1 канала 1.1 или. соответственно, группа 16.2 канала 1.2), т.е на входы 10 блока 2 задания режима. в регистре 46 блока 2 (фиг.2) установлен в единичное состояние, то на синхровход регистра 83 распределителя 9 тактооых импульсов (фиг.8) с выхода коммутатора 86 через элемент И 88 поступают импульсы от генератора 4 собственного канала.

Сигналом сброса с соответствующею выхода блока 2 задания режима по связи 15 распределитель 9 тактовых импульсов устанавливается в состояние выдачи сигнала на выходе 91.9 дешифратора 85 (фиг.З). После снятия сигнала сброса распределитель 9 зацикливается на оыдаче импульсов с выходов 9 1.9 и 91.10 (vni -J состояние приостанова) Далее при нажатии кнопки 51 пуска сигналом по связи 1 } с выхода блока 2 (фиг.2) триггер 55 блока 3

аСИНХрОННОЙ СВЯЗИ (фИГ.З) устам : ; ,1,) , Гся в единичное состояние По так го м/ импульсу с выхода 91 9 ;,: i о,,, ;о

распределителя , по с г пи . TI mi f e; блока 8 приостанова устач р ччзр - сч г- единичное состояние ч пезучь1 те чет выходным сигналом элемент-ч И 81, срягЗагывающет но продаваемому но связи 24.3 импульсу с вылодл 91 Н1 триггер 79 устанавливается в единичное состояние Поэтому с первого выходя блика Н при останова (фиг.7) снимается сигнал тсрмо0 жен и я распределителя g тактовых импульсов, и последний переходит к выработке последовательное. TRM тактовых импульсов на выходах 91.1 91.10 (фиг 9) Для того чтобы остановить распредели5 тель 9, достаточно нпжать кнопку 53 блока 2 (фиг.2), сигнал с. которой по связи 25 устанавливает триггер /9 (4 иг 7) v нулевое состояние, в результате чего на первом выходе блока 8 приостанова формируется

0 сигнал останова, который, поступая по спязи 26 приводит к описанному выше состоянию распределителя 9 тактовых им пульсов

При синхронной днух каналов

5 11 и 1 2 происходи одновременный их переход к выполнению очередной микрокоманды за десять тактовых импульсов с выходов 91.1 91 10 дешифратора 85 распределителя 9 тактовых импупьсов (флг.8)

0 Во время выполнения микрокоманды кахч- дый канал функционирует ас инхронно, однако канал, выполнивший микрокоманду раньше, приооiаидоливается до момента прилода де с я того т ,чч ic. oi с импуяьг.л в со5 седкем KdHane

В момент прихода де;,я:ого тактового импульса и в отстающем ;a in/;t на третьей группе 20 упра.ычющи/ вы-идов каналов выдается сигнал готовности по - оторому в

0 системе мо,от гтоизпчл.л ьсч например, сравнение рглулыспоп -ыполнения микрокоманды, после чего кпН -ты переходят к выполнению следующей микрокоманды. Ввод энймОН и си ixpoHHtA. осжим ра

5 боты осуществляется следующим обртзом

Описанным выше способом оба канала зацикливают си a cor imi формирова- ния де очтого и ц ее. от о тактовых имлуаьсив p. irnp VuMii нмем () на выводах

O 91 9 и П 1 1 0 дсш.11, p.jrc p) Т) гоопимствен- но

Пи h. i п-:.Ч)Ы- грут;. 16 1 и 1ь 2 уг г ib ьтп г;и |,r;lr, ,и f, ip;,;i

PeU ,,1 С rib -iG L m.1s КГН. r( fj , iHTi .Ul ll T

5 eq н ид.,. .II-HI , tu;. о M , -, i , ; IMU.UI pe

A , s I ,.., . FIG ,, : . - Н , П Г,)ЯЗИ

2 j Tr i - о лс .., /vHij.it,/ ; i -i ,/ ( L/IOK;J о s.. -. - .- -.1 { r i ; , j uiiia

i.l С л I 1. , „ Г,У - ,, .. ,11,1

j.O.v о .„:, i , . ,. . i, ir.i

пуском по связи 29 устанавливает триггер 64 блока 6 синхронного пуска (фиг.5) также а единичное состояние. Кроме того, по поступающему по связи 24.2 тактовому импульсу триггер 72 блока 7 управления синхронизацией (фиг.6) устанавливается в единичное состояние, что приводит к установке в единичное состояние также и триггера 73 блока 7.

Потенциал с выхода триггера 73 по свя- зи 33 поступает на вход элемента И 87 распределителя 9 (фиг.8), который срабатывает по передаваемому по связи 24.3 десятому тактовому импульсу и запрещает поступление опорных тактовых импульсов на вход синхронизации регистра 83 через элемент И 8В. В результате этого распределитель 9 останавливается в состоянии выдачи сигнала на выходе 91.10 дешифратора 85. Описанные операции происходят в обоих каналах.

Пусть активным при вводе в синхронизм является первый канал 1.1. Для запуска первого канала 1.1 необходимо замкнуть кнопку 51 пуска блока 2 задания режима этого канала. Сигнал с соответствующего выхода блока 2 канала 1.1 по связи 14 устанавливает а единичное состояние триггер 55 блока 3 (фиг.З). В результате этого формируются сигналы на выходе 58.2 (элементом И 57) и выходе 58.1 блока 3. Сигналы с первой группы 43.1 управляющих выходов канала 1.1 поступают на вторую группу 38.1 информационных входов канала 1,2,

Сигнал с входа 38.2 канала 1.2 поступа- ет через коммутатоо 61 (фиг.4) по связи 22 на ихсд окончания связи блока 6 (фиг.5) и устанавливает в единичное состояние триг- гор 65, сигнал с единичного выхода которого приводит к срабатыванию элемента ИЛИ |i8. Выходным сигналом элемента ИЛИ 68 чгрез элемент 71 задержки триггеры 64 и 65 устанавливаются в нулевое состояние.

Сигнал с второго выхода блока 6 синхронного пуска (фиг.5) по связи 23 поступает на синхропход риггерз 74 блока 7 управления синхронизацией (фиг.б), который устанавливается при этом в единичное состояние. В связи с этим срабатывает элемент ИЛИ 76, выходной сигнал которого ус- танавлизает в нулевое состояние триггер 73 блока 7, Сигнал низкого потенциала с единичного выхода триггера 73 по связи 33 и через элемент И 87 (фиг.З) разрешает поступление опорных тактовых импульсов че- рез элемент И 88 на синхровход регистра 83 распределителя 9 тактовых импульсов. Поскольку триггер 79 блока 8 приостанова находится в состоянии логического нуля, то на первом выходе блоке 8 присутствует сигнал

приостанова, который, поступая по связи 26 на вход приостанова распределителя 9 (фиг.8), приводит к зацикливанию его на выдаче тактовых импульсов с выходов 91.9 и 91,10 дешифратора 85, как описано выше (фиг.9, состояние приостанова).

При последующем нажатии кнопки 51 блока 2 задания режима (фиг.2) канала 1.2 выходной сигнал с соответствующего выхода блока 2, поступая по связи 14 на единичный вход триггера 55 блока 3 асинхронной свчзи (фиг.З) и информационный вход триггера 78 блока 8 приостанооа (фиг.7), устанавливает их в единичное состояние. Выходной сигнал элемента I/I 81 устанавливает триггер 79 блока 8 в единичное состояние, в результате чего снимается сигнал приостанова с первого выхода блока 8 и распределитель 9 начинает формировать импульсы на выходах 91.1-91.10 дешифратора 85 согласно описанному выше.

После установки в единичное состояние триггера 55 (фиг.З) срабатывает элемент И 57 и на выходе 58.2 формируется сигнал согласования каналов по концу микрокоманды, который через первую группу 43.2 управляющих выходов второго канала 1,2 поступает на вход 38.2 первого канала 1.1 и через коммутатор 61 блока 5 контроля времени связи (фиг.4) с второго управляющего выхода этого блока по связи 22 устанавливает триггер 65 блока 6 синхронного пуска в единичное состояние. Сигнал с единичного выхода этого триггера приводит к срабатыванию элемента И 67, выходной сигнал которого через элемент ИЛИ 68 и элемент 71 задержки устанавливает триггеры 64 и 65 в нулевое состояние, Кроме того, сигнал с выхода элемента И 67 по связи 23 поступает нг синхровход триггера 74 блока 7 (фиг.б) и .устанавливает его в единично состояние. При этом на выходе элемента ИЛИ 76 формируется сигнал, устанавливающий триггер 73 в нулевое состояние. Нулевой сигнал с первого выхода блока 7 по связи 33 и через элемент И 87 распределителя 9 тактовых импульсов (фиг.8) разрешает поступление тгктовых импульсов через элемент И 88 на синхровход регистра 83, выключая тем самым останов распределителя 9 канала 1.1 на выдаче сигнала с выхода 91.10 дешифратора 85. Распределитель 9 переходит к выдаче тактового импульса с выхода 91.9. При этом единичный сигнал с выхода 58.1 блока 3 канала 1.1 поступает по связи 28.1 на вход пуска блока 8. Поэтому по импульсу с выхода 58.1 триггер 78 устанавливается в единицу,

По очередному десятому тактовому импульсу (связь 24.3) с выхода 91.10 дешифратора 85 распределителя 9 срабатывает элемент И 81 (фиг.7) выходной сигнал которого устанавливает в единичное состояние триггер 79. Вследствие этого снимается пыход- ной сигнал с выхода элемента ИЛИ 80 (связь 26), распределитель 9 выходит из состояния останова и переходит к выполнению микрокоманды по десяти тактовым импульсам.

После перехода каждого канала к выполнению текущей микрокоманды они про- должают работать в синхронном режиме. При этом взаимное согласование каналоп в процессе синхронной работы происходит следующим образом.

Пусть в первом канале 1.1 микрокоман- да выполняется быстрее. Тогда по девятому тактовому импульсу (связь 24.2) триггер 72 блока 7 управления синхронизацией устанавливается в единичное состояние и сигналом с единичного выхода устанавливает в единичное состояние триггер 73. Выходной сигнал триггера 73 с первого выхода блока 7 по связи 33 через элемент И 87, срабатывающий по десятому тактовому импульсу (связь 24.3), блокирует поступление такто- вых импульсов опорной частоты через элемент И 88 (фиг.8) на синхровход регистра 03 распределителя 9. В результате этого рас пределитель 9 останавливается и выдает сигнал на выходе 91.10 дешифратора 85. Кроме того, по передаваемому по связи 24.3 импульсу триггер 54 блока 3 асинхронной связи (фиг.З) устанавливается в единичное состояние, приводя к срабатыванию элемента И 57 и к формированию сигнала на выходе 58.2 блока 3. Этот сигнал по связи 28.2 передается на соответствующий вход 38.2 соседнего канала через первую группу 43.1 управляющих выходов первого канала 1.1. Сигнал с единичного выхода триггера 54 блока 3 по связи 29 поступает на синхровход триггера 64 блока 6, который устанавливается в единичное состояние.

Сигнал синхронного перехода устройства к выполнению следующей микрокоманды с выхода 18.1 блока 6 (фиг.5) выдается низким потенциалом. В описываемый момент времени с выхода коммутатора 66 блока б по связи 18.2 выдается единичный потенцп - ал. Поэтому на выходе элемента И 62 блока 5 присутствует единичный сигнал, который после срабатывания элемента И 57 по связи 28.2 устанавливает -триггер 60 блока 5 контроля времени связи (фиг.4) в единичное состояние. Сигнал с единичного выхо- да триггера 60 открывает элемент И 63 для подачи опорных тактовых импульсов на счетный вход счетчика 59 с выхода 31 распределителя 9. С этого момента (момента завершения микрокоманды опережающим каналом) начинается оточог рсм-з. м максимального pacroi лаг.ования между каналами 1.1 и 12 счетчиком 59. 1с, до истечения этого времени с выхода синхронизации блока 3 канала 1.2 (отстающею) по связи 28 2 через первую группу 43.2 управляющих выходов этою поступит сиг нэп окончании выполнения микрокоманды на вход 38.2 канала 1.1, то срабатывает коммутатор 61 блока 5 и формируется сигнал на втором управляющем пыходе этого блока. Епи ж о до истечения этого интервала времени сигнал на вход 38.2 не поступает что свидетельствует об отказе (зависании) соседнего канала 1.2, то формируется сигнал переполнения счетчика 59, который пропускает на второй управляющий выход для передачи по связи 22 опорный тактовый импульс с выхода 31 распределителя 9. Таким образом имитируется ответ от соседнего канала для предотвращения останова данного канала. Кроме того, в данном случае на выходе 21 формируется сигнал отказа соседнего канала

С приходом сигнала по сиязи 22 триггер 65 блока 6 (фиг.5) устанавливается в единичное состояние. В результате этого через элементы И 67, ИЛИ 68 и элемент 71 задержки сбрасываются триггеры 64 и 65.

При срабатывании элемента И 67 снимается единичный потенциал с выхода 18.1 блока 6. Этот сигнал может быть использован в системе, например, для сравнения результатов выполнения микрокоманды в обоих каналах системы. Кроме того,этот, же сигнал, поступая по связи 18.2 на вход готовности блока 5 (фиг 4) приводит к формированию низкого потенциала на выходе элемента И 62, в результате чего устанавливается в нулевое состояние триггер 60 и счетчик 59.

В это же время по сигналу с выхода элемента И 57 по связи 23 триггер 74 блока 7 (фш.6) устанавливается в единичное состояние, его выходной сигнал через элемент ИЛИ 76 устанавливает в нулевое состояние триггер 73. Сигнал с единично о выхода этого i рш гера по J3 через элемент И 07 (фиг.8), формирующий гулевой выходной сигнал, открывает элемент И 88 для пропуска оперных тактовых импульсов на синхровход регистра 83. После этого данный канал 1.1 устройства переходит к выполнению очередной микрокоманды.

Отстающий второй канал 1.2 в рассмотренном случае функционирует следующим образом,

В канале 1.2 по девятому тактовому импульсу, поступающему по связи 24 2 в блок

7 (фиг.6), устанавливается в единичное состояние триггер 72, который устанавливает в единичное состояние триггер 73. Далее десятым тактовым импульсом по связи 24.3 устанавливается в единичное состояние триггер 54 блока 3 асинхронной связи (фиг.З), что приводит к срабатыванию элемента И 57 и формированию сигнала на выходе 58.2, который по связи 28.2 через первую ipynny 43.2 управляющих выходов качала 1.2 поступает на вход 38.2 первого канала 1.1 (опережающего), инициируя выполнение описанных выше функций.

По сигналу с выхода управления синх- рпнним рехимом блока 3 по связи 29 триггер О1 (фиг 5) устанавливается в единицу, что приводит к срабатыванию элемента И П7 поскольку триггер 65 к данному моменту прсмепи установлен по связи 22 в единич-, ное состояние сигналом с блока 6. Далее, :i, тлигично описанному выше, триггеры 64 .1 Ь5 устанавливаются в нулевое состояние, бормируетсп сигнал на выходе 18.1 блока Г;, устанавливаются в единичное состоя- мис триггер 74 блока 7 (фиг.6) и о нулевое состояние триггер 73 этого же блока. Та- ;,;IM образом осуществляется переход к : Ы11улнению следующей микрокоманды, а у отстающего канала отсутствует останов о состоянии выдачи десятого тактового импульса.

О случае поступления сигнала повторения микрокоманды по связи 35 с первой группы 16. управляющих входов первого чапала 1.1 (либо с первой группы 16.2 управ- .-и.ющих входов второго канала 1.2) при сбое и процессоре соответствующего канала происходит установка в единичное состояние триггера 74 блока 7 (фиг.6) при сраба- ТЫВРЬИИ элемента И 75, а также установка п нулевое состояние триггера 73 и триггера 54 (фиг.З) по десятому тактовому им- пул су (СЕЯЗЬ 24.3). Таким образом, сигнал с г ыхода 58.2 не выдается и соседний (работоспособный) канал останавливается в состоянии пыдэчи десятого тактового импульса с выхода 91.10 дешифратора 85 рлспределигеля 9.

После завершения повторения выпол- иснип микрокоманды процессор снимает сигнал, псступзюа1ий в блок 3 по связи 35, триггер 54 устанавливается в единичное состояние и далее функционирует о соот- г)г;тгтг(Ии с приведенным описанием. Соседний канал, получив сигнал с выхода 58.2 Олока 3 отказавшего канала, выполняет следующую микрокоманду.

Приостамов канала может осуществлялся 1экжс при поступлении сигнала тор- мо/чемия с выхода третьего разряда

регистра 46 блока 2 задания режима (фиг.2) одного из каналов на вход 37.3 другого канала, либо по сигналу на входе 36.2 блока 8 приостанова, либо при поступлении сигнала

останова на вход 36.1 от внешних устройств канала системы, выдаваемого до окончания операции взаимодействия с последними (в этом случае канал переходит в состояние приостанова, в котором циклически выда0 ются тактовые импульсы с выходов 91.7 и 91,8 дешифратора 85 распределителя 9). 8 этом случае с выхода элемента ИЛИ 70, являющегося третьим выходом 19 блока 6 синхронного пуска (фиг.5), выдается через

5 третью группу управляющих выходов канала (группа 40.1 канала 1.1 или группа 40.2 канала 1.2) сигнал чтения очередной микрокоманды из памяти соответствующего канала системы. Этот сигнал может выдаваться

0 либо по каждому поступающему по связи 24.1 второму тактовому импульсу, либо по поступающему на вход 37.2 сигналу с выхода четвертого разряда регистра 46 (фиг.2) соседнего активного канала для инициали5 зации чтения микрокоманды в остановленном канале.

Для перевода каналов 1.1 и 1.2 в режим независимого функционирования необходимо в первый разряд регистров 46 обоих

0 каналов записать нуль. Выключение устройства осуществляется путем установки триггера 47 блока 2 задания режима (фиг.2) в нулевое состояние сигналом с кнопки 50, Предлагаемое устройство позволяет

5 существенно повысить достоверность функционирования дуплексных вычислительных систем.

Формула изобретени Устройство для синхронизации вычис0 лительной системы, содержащее первый канал, включающий блок задания режима, блок асинхронной связи, генератор импульсов, входы блока задания режима являются первой группой управляющих входов пер5 вого канала, блок задания режима первым выходом пуска соединен с входом генератора импульсов, а выходом синхронного режима, вторым выходом пуска и выходом сброса соединен соответственно с первым, вторым

0 и третьим управляющими входами блока асинхронной связи, отличающееся тем, что, с целью повышения надежности и рас- шиоения области применения, оно содержит второй канал, в каждый канал

5 дополнительно введены блок контроля времени связи, блок синхронного пуска, блок управления синхронизацией, блок приоста- нос.а и распределитель тактовых импульсов, причем блок задания режима вторым выходом пуска соединен также с входом пуска

блока синхронного пуска, первый выход Олокэ синхронного пуска соединен с сходом готовности блока контроля времени связи, первый управляющий выход которого является выходом ошибки каиапя. второй управляющий пыход блока контроля времени связи соединен с входом окончания связи блока синхронного пуска, второй выход которого соединен с первым синхровходом блока управления синхронизацией, блок задания режима выходом сброса соединен с входами сброса блока синхронного пуска, блока управления синхронизацией и распределителя тактовых импульсов, группа выходов которого является группой тактоных выходов канала. блок задания режима выходом останова связан с входами останова блока синхронного пуска и блока приостанови, первый и второй выходы которого соединенLI соответственно с входом приостанова распределителя тактовых импульсов и первым синхровходом блока асинхронной связи, входы синхронно о режима блока контроля времени связи, блока синхронного пуска, блока управления синхронизацией и блока приосганова подсоединены к выходу синхронного режима блока задания режима, выход выбора тактовых импульсов которого соединен с входом выбора тактовых импульсов распределителя тактовых импульсов, выходы пуска и синхронизация блока асинхронной связи соединены соответственно с входом пуска блока приостанова и первым синхровходом блока контроля времени связи и являются первой группой управляющих выходов канала связи, выход управления синхронным пуском блока асинхронной связи соединен с первым синхровходом блока синхронного пуска, выход генератора импульсов соединен с входом тактовых импульсов распределителя тактовых импульсов, выход и вход обмена тактовыми импульсами которого являются соответственно выходом и входом обмена тактовыми импульсами канала связи, выход обмена тактовыми импульсами распределителя тактовых импульсов соединен с тактовым входом блока контроля времени связи, первый и второй выходы блока управления синхронизацией соединены со- ответстоенно с первым управляющим входом распределителя тактовых импульсов и управляющим входом блока асинхронной связи, выход первого разряда группы выходов распределителя так юных импульсов соединен с вторым синхровходом блока синхронного пуска и вторым синхровходом блока управления синхронизацией, и лход ы opoi о разрчд i группы выходов распредгл и г--злч , пульсов соединен с третьим син.фовло дом блока управления синлроиизациейи первым синхровходом 5лск .фиостано- ва, выход третьего ралрядс ipy 1 .лы выхо- доз распределителя тякточых импульсов соединен с его входом окончания цикла, а также с четвертым синхровходом бг-о0 ка управления синхронизацией, вторым синхровходом блока присстангва и вторым опнхровходом асинхронной связи, управляющие входы блока управлениясинхрончзяцмойи блока асин5 уропной связи соединены с одним из входов блока задачи я режима, второй управляющий вход распределителя тактовых импульсоп и первый управляющий вход блока приостанови являются второй

0 группой управляющих входов капала, входы первого и второго разрядов первой группы информационных входов канала свчзи соединены соответственно с входом инициализации чтения Ьлока синхронного

5 пуска и вторым управляющим входом блока приостанова, входы первого и второго разрядов второй группы информационных входов канала соединены соответственно с вторым синхровходом блока контроля вре0 мени связи и третьим управляющим входом бпока приостанова, в каждом из каналов группа выходов бпока задания режима является второй группой управляющих выходов канала и соединена с первой группой ин5 формационных входов другого канала, я первая группа управляющих выходов каждого канала под о.юченя к пторой группе информационных входов другого канала, в каждом канале первый и третий выходы бло0 ка синхронного пуска являются третьей группой управляющих ВЫХСДОР капала, выход обмена тактовыми импульсами каждого канала связан с входом обмена тактовыми импульсами другого канала, выходы ошибки

5 первого и второго каналов являются соответственно первым и вторым выходами ошибки устройства, третьи группы управляющих выходов nepFioro и второго каналов яеллются соответственно п:рссй и второй

0 группами управляющих выходов устройства, группы тактовых выходов первого и ото- noto каналов являются и второй группами гсктовых выходов устройства, первые труппы управляющие входов персо

5 го и второго каиалсз являются меркой и второй группами входов устройства, а вторые группы управляющих входсз первого и ыо- рс-го конзлоо - соответственна третьей и четвертой (руппзми входов устройсиз..

Таблица 1

Таблица 2

in со rT

oo to

cu

3

.

f

cr

00

-J

O3 СЛ

Щи г Б

Фиг. 7

п

п

п

п

п

п

П

П.

touocmnHal

.

Фиг.9

приоГтанм им остоно

Авторы

Даты

1991-10-15—Публикация

1985-05-28—Подача