Изобретение относится к вычислительной технике, а именно к разделам ассоциативных запоминающих устройств и операций над матрицами и может быть использовано в системах цифровой обработки массивов факсимильных данных, а также в ассоциативных вычислительных системах, томографах, автоматизированных рабочих местах, имеющих развитую аппаратуру отображения информации.

Целью изобретения является расширение области применения ассоциативного запоминающего устройства за счет возможности многоформатного доступа к произвольно расположенным W-разрядным фрагментам столбцов и строк.

Для осуществления многоформатного доступа к данным, включающего в себя размещение элементов любого W-разрядного фрагмента строки и столбца матрицы данных в разных микросхемах памяти и формирование адреса для каждой микросхемы памяти при данном размещении элементов, сначала формируются адреса для каждой микросхемы памяти при данном размещении элементов, сначала формируются адреса для каждой микросхемы памяти отдельно с применением арифметических операций

( 00

4 00

го

по модулю W над базовым адресом, адресом смещения W-разрядного фрагмента от- носительно базового и номером микросхемы согласно коду типа обращений, затем над данными W-разрядного фрагмента, полученного в результате обращения к памяти при чтении или из шины данных при записи, производится операция циклического сдвига для приведения к однозначному соответствию между элементами массива данных, номерами микросхем и адресами в них согласно местоположению W- разрядного фрагмента в массиве данных занесение модифицированного W-разрядного фрагмента в шину данных при чтении или в блок памяти при записи. Причем каждый элемент массива данных с координатами Ј i, m, где { - адрес строки массива данных,

();

I - адрес слова в строке (0 I 1-1);

m - параметр смещения, равный адресу бита в слове (0 m W-I), размещают в микросхеме, номер которой п определяется по формуле

где modw значение выражения в скобках, взятое по модулю числа W.

Формирование адреса строки Atn для микросхемы с номером п - при обращении к произвольно расположенному в массиве данных W-разрядному фрагменту столбца производится по формуле

W modw W-m}+ n-Wj,

где С- адрес строки верхнего бита,W - разрядного фрагмента столбца, при этом

О l L-1-W;

m - адрес верхнего Вита W-разрядного фрагмента столбца в слове относительно традиционного способа адресации, при этом 0 m W-1;

ц.ч - целая часть выражения, заключенного в скобках,

. 11 при п modwtf+

J о при n m а формирование адреса слова Aiu в строке с адресом А|П при обращении к фрагменту столбца для всех микросхем памяти одинаково и адрес равен I, где 0 I 1-1, при этом приведение к однозначному соответствию между элементами массива данных и номерами микросхем памяти при записи обеспечивается посредством циклического сдвига на количество разрядов Z, вычисляемое по формуле

, а при чтении - по формуле

Z W-modw l+m.

Формирование адреса Ain слова в строке для микросхемы с номером п при обращении к произвольно расположенному в

массиве данных W-разрядному фрагменту строки производится по формуле + q,

1 при modwtl n rnodwfC+ m где g 0 при n &modwtt+m О при n :S modwtfl;

| - адрес левого бита W-разрядного фрагмента строки в слове относительно традиционного способа адресации, при этом О m Ј W-1;

Я- адрес строки, при этом О С L-1,

а формирование адреса строки Afn длп всех микросхем памяти одинаково и адрес равен I, где О S Is L-I. При этом приведение к однозначному соответствию между элементами массива данных и номерами микросхем памяти при записи обеспечивается посредством циклического сдвига ни количество разрядов Z, вычисляемое по формуле , а при чтении - по формуле

Z W-modwrf+m.

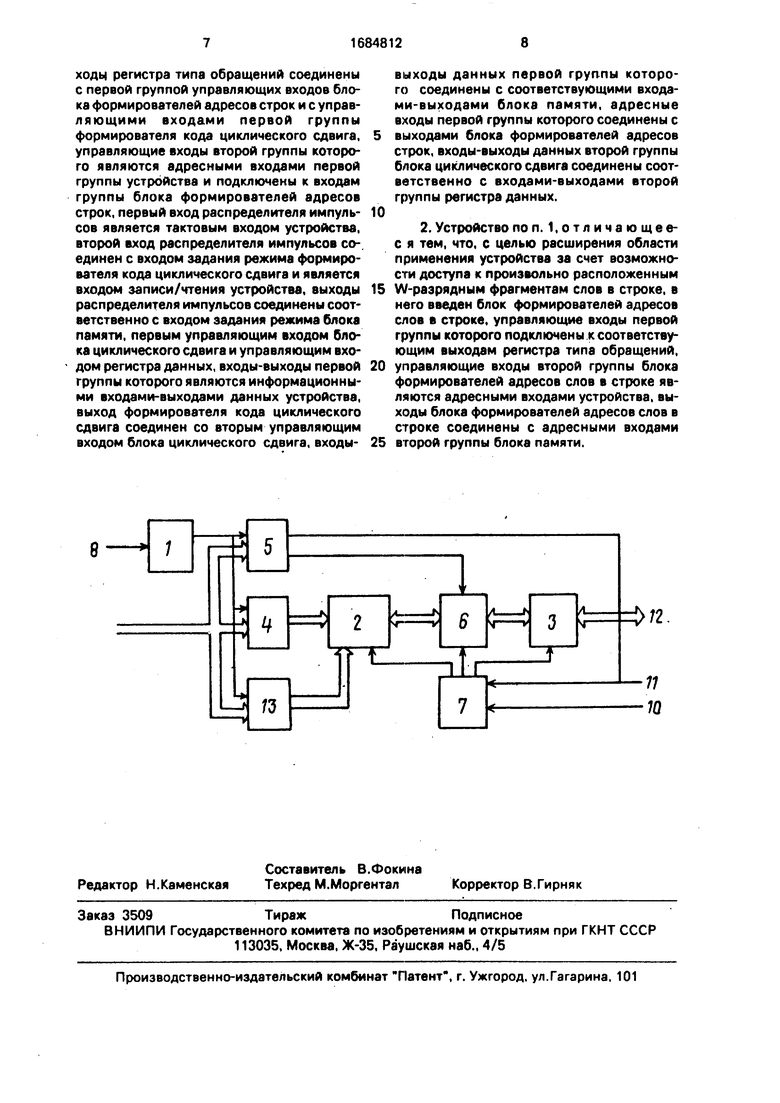

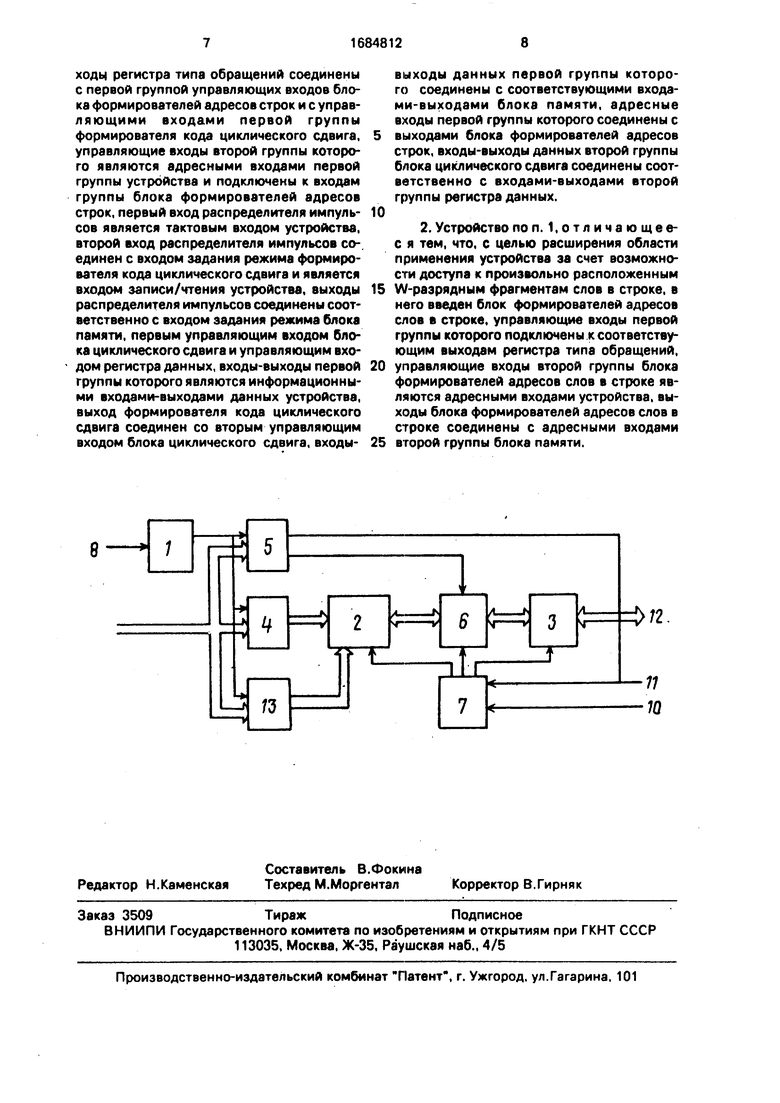

На чертеже показана блок-схема ассоциативного запоминающего устройства, реализующего многоформатный доступ к данным.

Ассоциативное запоминающее устройство с многоформатным доступом к данным содержит регистр типа обращений 1, блок памяти 2, регистр данных 3, блок формирователей адресов строк 4, формирователь кода циклического сдвига 5, блок циклического сдвига 6, распределитель импульсов 7, группу входов 8 регистра типа обращений к данным, адресные входы 9, тактовый вход 10 устройства, вход задания

режима записи-чтения устройства 11, двунаправленную W-разрядную шину данных 12 и блок 13 формирователей адресов слов в строке.

Группы входов 8 регистра типа обращений 1 являются информационными входами устройства, выходы регистра типа обращений 1 являются информационными входами устройства, выходы регистра типа обращений 1 соединены с первой группой управляющих входов блока формирователей адресов строк 4 и с первой группой управляющих входов формирователя кода циклического сдвига 5, управляющие входы второй группы которого являются адресными входами устройства 9 и подключены ко второй группе входов блока формирователей адресов строк 4, первый вход распределителя импульсов 7 является тактовым входом 10 устройства, второй вход распределителя импульсов соединен с входом задания режима формирователя кода циклического сдвига 5 и является входом записи/чтения 11 устройства, выходы распределителя импульсов 7 соединены соответственно с входом задания режима блока памяти 2, первым управляющим входом блока циклического сдвига б и управляющим входом регистра данных 3, входы-выходы первой группы которого являются информационными входами-выходами данных устройства 12, выход формирователя кода циклического сдвига 5 соединен со вторым управляющим входом блока циклического сдвига 6, входы-выходы данных первой группы которого соединены с соответствующими входами-выходами блока памяти 2, адресные входы первой группы которого соединены с выходами блока формирователей адресов строк 4, входы-выходы данных второй группы блока циклического сдвига 6 соединены соответственно с входами-выходами второй группы регистра данных 3, управляющие входы первой группы блока формирователей адресов слов в строке 13 подключены к соответствующим выходам регистра типа обращений 1, управляющие входы второй группы блока формирователей адресов слов в строке 13 являются группой адресных входов устройства, выходы блока формирователей адресов слов в строке 13 соединены с адресными входами второй группы блока памяти 2.

Осуществление многоформатного доступа к данным обеспечивается ассоциатив- ным запоминающим устройством следующим образом.

На адресную шину 9 устройства подается базовый адрес, в котором располагается левый или верхний бит W-разрядного фрагмента строки или столбца двумерного L х(1х xW) бинарного массива данных. В регистр типа обращений 1 заносится адрес m левого или верхнего бита W-разрядного фрагмента строки или столбца относительно традиционного метода адресации к W-разрядным словам и код типа обращения строка/столбец.

По этим адресам формирователь кода циклического сдвига 5 выдает в блок циклического сдвига 6 в режиме чтения количество разрядов Z, на которое необходимо циклически сдвинуть полученные в результате обращения к блоку памяти 2.

Согласно кода типа обращения, записанного в регистр типа обращений 1, и адресов в блоке формирователей адресов строк 4 при обращении к фрагменту столбца для каждой одноразрядной микросхемы памяти с номером n(0 n W-I) с адресным пространством L x I блока памяти 3 формируется и поступает свой адрес строки Afh.

Согласно кода, записанного в регистр 5 типа обращений 1, и адресов в блоке формирования адресов слов 13 при обращении к фрагменту строки для каждой одноразрядной микросхемы памяти с номером n регистра 3 формируется и подается свой адрес

0 слова Afh, а при обращении к фрагменту столбца для каждой микросхемы памяти адрес слова в строке одинаков и равен А|ПН.

При поступлении сигнала Запись распределитель импульсов 7 воспринимает им5 пульсы тактового входа устройства 10, формирует временные диаграммы, необходимые для осуществления последовательностей операции доступа к блоку памяти 2. При записи входные W-разрядные данные

0 сначала записываются в регистр данных 3, затем над полученными данными производится операция циклического сдвига в блоке циклического сдвига 6 на количество разрядов, вычисленное в формирователе

5 кода циклического сдвига 5, и далее модифицированные данные записываются в блок памяти 2 по адресам, поступающим из блоков формирователей адресов 4 и 13, При поступлении сигнала Чтение рас0 пределитель импульсов 7, воспринимая импульсы с тактового входа устройства 10, формирует временные диаграммы, необходимые для осуществления последовательностей операций доступа к блоку памяти 2

5 при чтении в соответствии с выбранной элементной базой, при этом из блока памяти 2 по адресам, сформированным в блоках формирователей адресов 4 и 13, выбирается W-разрядная информация, над которой про0 изводится операция циклического сдвига в блоке 6 на количество разрядов, вычисленное в формирователе кода циклического сдвига 5, и полученный таким образом W- разрядный фрагмент массива заносится в

5 регистр данных 3.

Формула изобретения 1. Ассоциативное запоминающее устройство с многоформатным доступом к данным, содержащее регистр типа обращений,

0 блок памяти и регистр данных, отличающееся тем, что, с целью расширения области применения устройства за счет возможности доступа к произвольно расположенным W-разрядным фрагментам слов в

5 столбце, в него введены блок формирователей адресов строк, формирователь кода циклического сдвига, блок циклического сдвига и распределитель импульсов, причем входы группы регистра типа обращений являются информационными входами устройства, выходц регистра типа обращений соединены с первой группой управляющих входов блока формирователей адресов строк и с управ- ляющими входами первой группы формирователя кода циклического сдвига, управляющие входы второй группы которого являются адресными входами первой группы устройства и подключены к входам группы блока формирователей адресов строк, первый вход распределителя импуль- сов является тактовым входом устройства, второй вход распределителя импульсов соединен с входом задания режима формирователя кода циклического сдвига и является входом записи/чтения устройства, выходы распределителя импульсов соединены соответственно с входом задания режима блока памяти, первым управляющим входом блока циклического сдвига и управляющим входом регистра данных, входы-выходы первой группы которого являются информационными входами-выходами данных устройства, выход формирователя кода циклического сдвига соединен со вторым управляющим входом блока циклического сдвига, входы-

выходы данных первой группы которого соединены с соответствующими входами-выходами блока памяти, адресные входы первой группы которого соединены с выходами блока формирователей адресов строк, входы-выходы данных второй группы блока циклического сдвига соединены соответственно с входами-выходами второй группы регистра данных.

2. Устройство поп. 1,отличающее- с я тем, что, с целью расширения области применения устройства за счет возможности доступа к произвольно расположенным W-разрядным фрагментам слов в строке, в него введен блок формирователей адресов слов в строке, управляющие входы первой группы которого подключены к соответствующим выходам регистра типа обращений, управляющие входы второй группы блока формирователей адресов слов в строке являются адресными входами устройства, выходы блока формирователей адресов слов в строке соединены с адресными входами второй группы блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с многоформатным доступом к данным | 1983 |

|

SU1108507A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1345259A1 |

| Запоминающее устройство с параллельным произвольным доступом к строкам и окнам данных | 1987 |

|

SU1499355A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1981 |

|

SU1043747A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1355997A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Устройство цифровой двумерной свертки | 1988 |

|

SU1647585A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1336109A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

Изобретение относится к вычислительной технике, а именно к разделам ассоциа- тивных запоминающих устройств и операций над матрицами, и может быть использовано в системах цифровой обработки массивов факсимильных данных, а также в ассоциативных вычислительных системах, томографах, автоматизированных рабочих местах, имеющих развитую аппаратуру отображения информации. Целью изобретения является расширение области применения устройства за счет возможности доступа к произвольно расположенным W-разряд- ным фрагментам слов в столбце и в строке. Поставленная цель достигается введением в устройство блока формирователей адресов строк, формирователя кода циклического сдвига, блока циклического сдвига распределения импульсов и блока формирователей адресов слов в строке. Для осуществления многоформатного доступа к данным, включающего в себя размещение элементов любого W-разрядного фрагмента строки и столбца матрицы данных в разных микросхемах памяти и формирование адреса для каждой микросхемы, сначала формируются адреса для каждой микросхемы отдельно, затем надданными поразрядного фрагмента производится операция циклического сдвига. 1 з. п. ф-лы, 1 ил. Ё

| УСТАНОВКА И СПОСОБ ИЗВЛЕЧЕНИЯ ЦИНКА ИЗ ИЗГАРИ ЦИНКА | 2008 |

|

RU2369650C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Патент США I 3800289, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1991-10-15—Публикация

1988-06-15—Подача