f1 Изобретение относится к вычислительной Технике, в частности к запо hiUHaiOBgHM устройствам, и может быть использовано в специализированных системах хранения и цифровой обрабо ки изображений, а также в ассоциативных вычислительных системах. Известно запоминающее устройство с многоформатным доступом к данным содержащее блок памяти и средства диагональной адресаций, допускающие хранение двумерных бинарных массивов с возможностью параллельного доступа к их строкам и столбцам СП Недостатком этого устройства являются большие аппаратные затраты Наиболее близким техническим решением к изобретению является асс циативное запоминающее устройство, содержащее регистр типа обращений, регистр адреса, сумматор по модулю два, блок мультиплексоров, регистр данных и блок памяти, причем выход регистра типа обращений соединен с одним из входов сумматора по модулю два, выход которого соединен с первь1М адресным входом блока памяти, выход регистра адреса соединен с управляющим входом блока мультиплексоров данных, вторым входом сумматора по модулю два и вторым адресным входом блока памяти, выход которого соединен через блок мультиплексоров с регистром данных. Блок памяти этого устройства постро ен на интегральных микросхемах памя ти емкостью Z бит каждая, где R 1,2,3,... . Дпя хранения информаци используется W интегральных микросхем памяти () . Для реализаци многоформатного (к строкам и столбцам) доступа, элементы запоминаемой матрицы (бинарного массива W W) размещаются в интегральньк микросхемах памяти таким образом, чтобы все элементы любой строки или столб ца попадали в разные микросхемы памяти. Это обеспечивает возможность одновременной выборки произвольной строки или-столбца. Для описания соответствия между элементами запоминаемой матрицы,номерами интеграл ньк микросхем памяти и адресами в них введем следующие обозначения: J, I - номер столбца, строки запоминаемой матрицы: J O-J-(W-I); (W-1); N - номер интегральной микросхемы памяти ,N Or(W-l); A-R - разрядный адрес, определяю7щий выборку бита в одной микросхеме памяти, S - тип обращения, S О - (W-1). Конкретные значения J, I, N, А, S можно рассматривать как двоичные .векторы и обозначить соответственно J, I, N А, S. В дальнейшем используются поразрядные операции коньюнкции Л, дизъюнкции V , сложения по модулю два @ и отрицание - над двоичными векторами. Каждый двоичный элемент запоминаемой матрицы с координатами I, J хранится в микросхеме памяти, код номера которой определяется из соотношения: © J Для подачи адресов на микросхемы памяти используются две шины X и У. По шине X подается код адреса (X) с регистра адреса устройства, а по шине Y поступает код (Y) с выхода сумматора по модулю два, на вход которого заведены X и S т.е. Y S. Такое соединение обеспечивает S различных способов обращения, причем при 3 000.. .0 обращение происходит к строкам запоминаемой матрицы, а при.S 111 ... 1 - к столбцам запоминаемой матрицы. Номер строки и столбца задается кодом Х Выражение (1), определяющее распределение элементов строк (столбцов) по микросхемам памяти, указывает, что для различных строк (столбцов) порядок элементов на шине данньк блока памяти различный. Этот порядок для строки (столбца) с номером I (J) определяется соответствующим диадным (по модулю два) сдвигом. Чтобы обеспечить однозначную упорядоченность при выборке любой строки (столбца) в устройстве используется мультиплексор данных, состоящий из logjW групп, Каждая группа реализует перестановку элементов строки (столбца), соответствующую диадному сдвигу определенного 2°, 2 2,..., порядка. Управление включения групп мультиплексора данных осуществляется в зависимости от состояния разрядов регистра адреса 21. Недостатком этого устройства является невозможность реализации

трехмерной запоминающей среды, в которой наряду с многоформатными обращениями к элементам битовой матрицы памяти допускалась бы возможность доступа к словам, К разрядов которых распределены в К матрицах битовой памяти, что сужает область применения устройства.

Целью изобретения является расширение области применения запоминающго устройства с многоформатным доступом к данным за счет обеспечения возможности хранения трехмерного битового массива данных (двумерного массива многоразрядных данных) и организации трехмерного доступа к ним: к строкам и столбцам любой матрицы, а также к словам, разряды, которых распределены во всех матрицах памяти.

Поставленная цель достигается тем, что в запоминающее устройство с многоформатным доступом к данным, содержащее регистр типа обращений, регистр-адреса,-первый сумматор по модулю два, мультиплексор, регистр данных и матричный блок памяти, причем выход регистра типа обращений соединен с одним из входов первого сумматора по модулю два, выход которого соединен с первым адресным входом матричного блока памяти, выход регистра адреса соединен с вторым входом первого сумматора по модулю два и вторым адресным входом матричного блока памяти, информационный выход которого соединен с входом мультиплексора, выход которого подключен к входу регистра данных, введены дополнительные матричные блоки памяти и мультиплексоры, регистр номера столбца, второй и третий сумматоры по модулю два, триггер режима, регистр номера матрицы памяти и первый и второй дешифраторы, причем перйые адресные входы дополнительных матричных блоков памяти подключены к выходу первого сумматора по модулю два, вторые адресные входы - к выходу регистра адреса и к первому входу . второго сумматора по модулю два, выход которого соединен с входом первого дешифратора, с первыми Управляющими входами мультиплексоров и с первым входом третьего сумматор по модулю два, выход которого соединен с вторыми управляющими входами

мультиплексоров, информационные выходы дополнительных мультиплексоров подключены к входам регистра данных, информационные входы - к соответствующим выходам дополнительных матричных блоков памяти, прямой выход триггера режима соединен с вторым входом третьего сумматора по модулю два и стробируюшим входам первого дешифратора, выходы которого подключены к третьим адресным входам матричных блоков памяти, инверсный выход триггера режима соединен с стробирующим вхо5дом второго депшфратора, вход которого соединен с выходом регистра номера матрицы памяти, а выходы подключены к четвертым адресньм входам матричньк блоков памяти, выход ре0гистра номера столбца соединен с вторым входом второго сумматора по модулю.два.

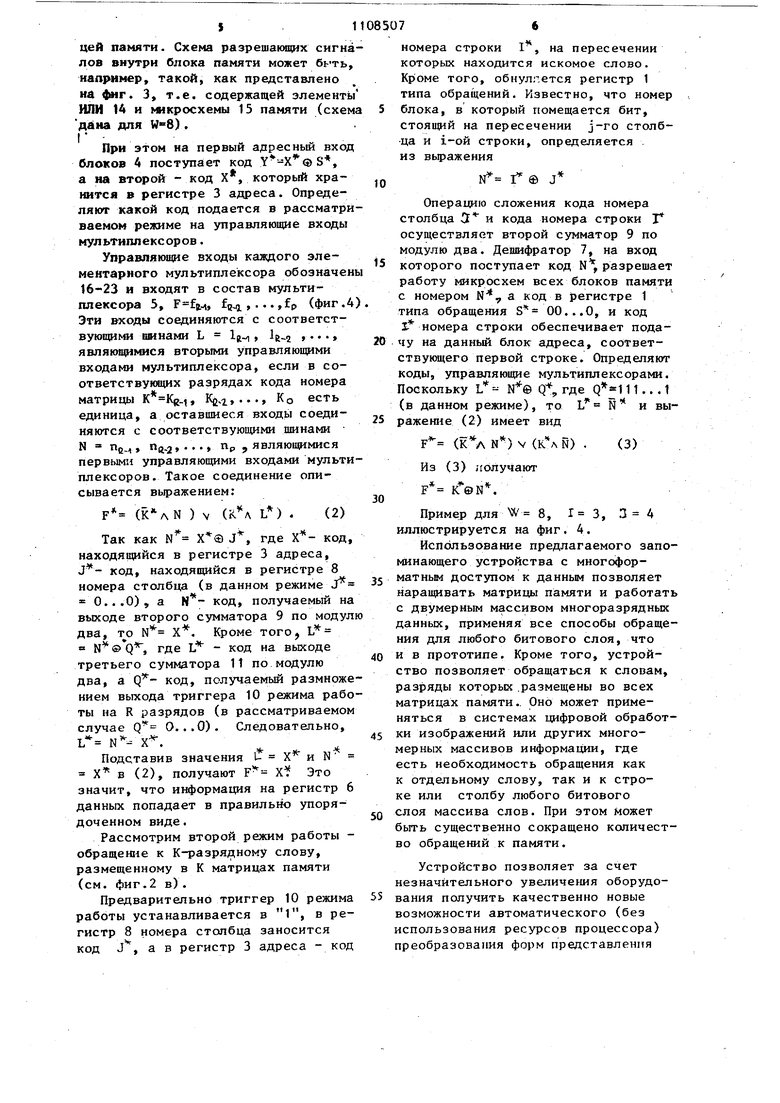

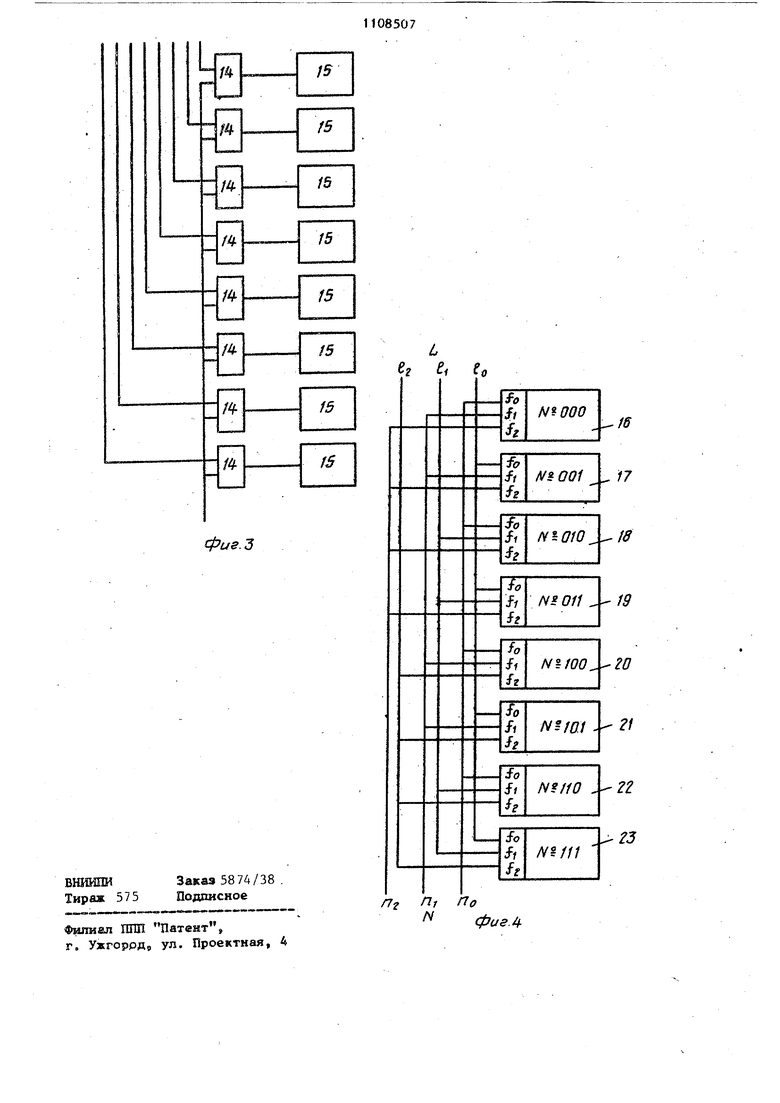

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - три основных вида обращений, соответствующие трехмерной организации доступа к данным; на фиг. 3 - схема оргаHH3ai9iH разрешающих сигналов в матричном блоке памяти, на фиг. 4 - схе0ма соединения управляющих входов мультиплексоров.

Запоминающее устройство с многоформатным доступом к данным (см. фиг. t) содержит регистр 1 типа

5 обращений, первый сумматор 2 по модулю два, регистр 3 адреса, матричные блоки А памяти, мультиплексоры 5, регистр 6 данных, первый дешифра-тор 7, регистр 8 номера столбца,

0 второй сумматор 9 по модулю два, триггер 10 режима, третий сумматор 11 по модулю два, регистр 12 номера матрицы, второй дешифратор 13.

Д5 Рассмотрим работу устройства в режиме обращения к строкам (столбцам) матри1в 1 (см. фиг. 2 а,б) .Перед началом работы триггер 10 режима работы устанавливается в О.

jQ.задается тип обращения (код S записывается в регистр 1 типа обращений) , задается адрес обращения (код X записывается в регистр 3 адреса), задается номер матриьрл, к которой должно произойти обращение (код к записывается в регистр 12), и обнуляется регистр 8 номера столбца. К-ый выход дешифратора 13 разрешает работу с соответствующей матрицей памяти. Схема разрешающих сигн лов внутри блока памяти может бь-ть например, такой, как представлено на 4мг. 3, т.е. содержащей элемент ИЛИ 1А и микросхемы 15 памяти (схе ддна для ). При этом на первый адресный вхо блоков 4 поступает код , а на второй - код X, который хранится в регистре 3 адреса. Определяют какой код подается в рассматр ваемом режиме на управляющие входы мультиплексоров. Управляющие входы каждого элементарного мультиплексора обозначе 16-23 и входят в состав мультиплексора 5, , fgjj , fp (фиг. Эти входы соединяются с соответствующими шинами L 1(1 , ) t являющимися вторыми управляющими входами мультиплексора, если в соответствующих разрядах кода номера матрицы ., KC-I,..., KO есть единица, а оставшиеся входы соединяются с соответствующими шинами являющимися о-1 в-2 первь1ми управляющими входами мульт плексоров. Такое соединение описывается выражением: F ( ) Так как N J, где находящийся в регистре 3 адреса, код, находящийся в регистре 8 номера столбца (в данном режиме J 0...0), а код, получаемый н выходе второго сумматора 9 по моду два, то N X. Кроме того, L и N ® Q, где L - код на выходе третьего сумматора И по модулю два, а код, получаемый размнож нием выхода триггера 10 режима раб ты на R разрядов (в рассматриваемо случае Q О...0). Следовательно, L- X. 1 Х и N Подставив значения Х в (2), получают F Xlf Это значит, что информация на регистр данных попадает в правильно упорядоченном виде. Рассмотрим второй режим работы обращение к К-разрядному слову, размещенному в К матрицах памяти (см. фиг.2 в). Предварительно триггер 10 режима работы устанавливается в 1, в ре гистр 8 номера столбца заносится код J, а в регистр 3 адреса - код номера строки 1 , на пересечении которых находится искомое слово. Кроме того, обнулпется регистр 1 типа обращений. Известно, что номер блока, в который помещается бит, стоящий на пересечении j-ro столбца и i-ой строки, определяется из выражения N Г ® J Операцию сложения кода номера столбца 5 и кода номера строки I осуществляет второй сумматор 9 по модулю два. Дешифратор 7, на вход которого поступает код N разрешает работу ьткросхем всех блоков памяти с номером N, а код в регистре 1 типа обращения S 00...О, и код 1 номера строки обеспечивает подачу на данный блок адреса, соответствующего первой строке. Определяют Коды, зшравляющие мультиплексорами. Поскольку L - Q, где ... 1 (в данном режиме), то L N ражеш{е (2) имеет вид F N) V (К N) . Из (3) .-голучают Пример для W 8, 1 3, 3 4 иллюстрируется на фиг. 4. Использование предлагаемого запоминающего устройства с многоформатньм доступом к данным позволяет наращивать матрицы памяти и работать с двумерным массивом многоразрядных данньЕс, применяя все способы обращения для любого битового слоя, что и в прототипе. Кроме того, устройство позволяет обращаться к словам, разряды которых .размещены во всех матрицах памяти.. Оно может применяться в системах цифровой обработки изображений или других многомерных массивов информации, где есть необходимость обращения как к отдельному слову, так и к строке или столбу любого битового слоя массива слов. При этом может быть существенно сокращено количество обращений к памяти. Устройство позволяет за счет незначительного yвeличe шя оборудования получить качественно новые возможности автоматического (без спользования ресурсов процессора) преобразования форм представления

данных. Так, например, устройство памяти, хранящее двумерный массив многоразрядных слов, допускает наряду с возможностью адресной выборки слова выполнение обращений к любому разрядному срезу множества слов, составляющих строку или столбец двумерного массива.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с многоформатным доступом к данным | 1981 |

|

SU1043747A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1345259A1 |

| Ассоциативное запоминающее устройство с многоформатным доступом к данным | 1988 |

|

SU1684812A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Устройство для формирования оптимальных дискретно-частотных сигналов | 1988 |

|

SU1552395A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ШЮГОФОРМАТНЫМ ДОСТУПОМ К ДАННЫМ, содержащее регистр типа обращений, регистр адреса, первый сумматор по модулю два, матричный блок памяти, мультиплексор и регистр данных, причем выход регистра типа обращений соединен с одним из входов первого сумматора по модулю два, выход Которого соединен с первым адресным входом матричного блока памяти, выход регистра адреса соединен с вторым входом первого сумматора по модулю два и вторым адресным входом матричного блока памяти, информационный выход которого соединен со входом мультиплексора, выход которого подключен к входу регистра данных, отличаю ; ееся тем, что, с целью расширения области применения устройства за счет обеспечения- трехмерного доступа к данным, в него введены дополнительные матричные блоки памяти и мультиплексоры, регистр номера столбца, второй и третий сумматоры по модулю два, триггер режима, регистр номера матрицы памяти, первый и второй дешифраторы, причем первые адресные входы дополнительных матричных блоков памяти подключены к выходу первого сумматора по модулю два, вторые адресные входы - к выходу регистра адреса и к первому входу второго сумматора по модулю два, выход которого соединен с входом первого дешифратора, с первыми управляющими входами мультиплексоров и с первым входом третьего сумматора по модулю два, выход которого соединен с вторыми управляющими входами мультиплексоров, информационные выходы дополнительных мультиплексоров подключены к входам регистра данных, информационные входы - к соответствующим выходам дополнительных матричных блоков памяти, прямой выход триггера режима соединен с вторьпч входом третьего сумматора по модулю Q два и стробирующим входом первого эо дешифратора, выходы, которого подклюг СП чены к третьим адресным входам матричных блоков памяти, инверсный о выход триггера режима соединен с стробирующим входом второго дешифратора, вход которого соединен с выходом регистра номера матрицы памяти, а выходы подключены к четвертым адресньм входам матричных блоков памяти, выход регистра номера столбца соединен с вторым входом второго сумкатора по модулю два.

э

g

,л

/с

л

//

../-,

/// ////////J

фиа.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кохонен Т | |||

| Ассоциативные запоминающие устройства | |||

| М., Мир, 1982, с | |||

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3800289, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-08-15—Публикация

1983-01-10—Подача