Изобретение относится к вычислительной технике и может быть использовано в многоразрядных устройствах сдвига информации. Целью изобретения является упрощение регистра сдвига, которое позволяет уменьшить площадь, занимаемую регистром, а также снизить потребляемую регистром мощность при интегральном исполнении регистра.

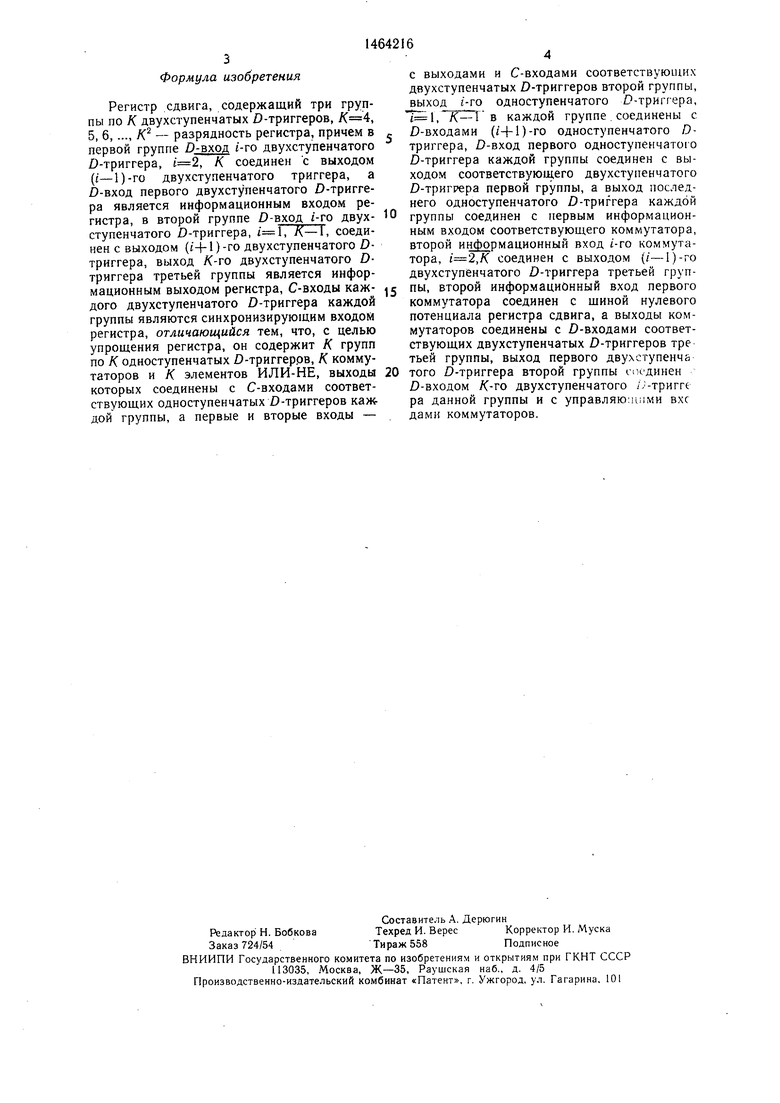

На чертеже показана схема 16-разрядного регистра.

На схеме обозначены информационные вход 1 и выход 2 регистра, вход 3 синхронизации регистра, первая 4, вторая 5 и третья 6 группы по К двухступенчатых )-триггеров в каждой (/(4, 5, 6 ..., К - разрядность регистра) К групп 7| -7к по /( одноступенчатых D-триггеров в каждой. Л коммутаторов 8, А, элементов ИЛИ-НЕ 9, щина 10 нулевого потенциала (источник сигнала логический 0), выходы 11 триггеров 4, выходы 12 триггеров 5, выходы 13 элементов ИЛИ- НЕ 9, выходы 14 триггеров 7.

Регистр работает следующим образом (работа рассмотрена для случая /(4). В начальном состоянии триггеры 5 второй группы, которые образуют кольцевой регистр, устанавливаются в состояние «1, кроме первого триггера 5i, который устанавливается в состояние «О.

По перво.му тактовому сигналу (С) входные данные записыг5аются в триггер 4 и появляются на его выходе lli после окончания синхросигнала (по срезу). В это время сигнал «О сдвигается в «ольцевом регистре в триггер 5к и появляется на его выходе 12к.

По второму тактовому сигналу второй разряд входных данных записывается в триггер 4i, информация из которого переписывается в триггер 42 и появляется на его выходе Ib. В это время сигнал «О в кольцевом регистре появляется на выходе 2з.

Аналогичным образом по третьему и четвертому тактовым импульсам входные данные записываются в триггеры первой группы и появляются на их выходах lli, Ib, П.з и 11к.

За это время сигнал «О в кольцевом регистре доходит до триггера 5i и появляется на его выходе i2i. По сигналу с выхода 12i и синхроимпульсу (С) на выходе элемента 9i появляется сигнал записи, по которому информация с триггеров 4i-Кк переписывается в первые D-триггеры каждой из К групп - 7i.i, 72.1, 7з.| и 7-к. и появляется на их выходах.

За четыре следующие синхроимпульса в триггеры 4|-4к записываются следуюихие четыре разряда информации. За эти такты (5-8) сигнал «О проходит по кольцеврму регистру и вновь формирует сигнал записи на элементе 9i.

Информация из триггеров 7i..i-7i.w первой ступени переписывается во вторую ступень - триггеры 72.1-72.x по сигналу записи, который формируется элементом Эа по тактовому импульсу С (пауза между сигналами 7 и 8).

По.сищалу «О с выхода триггера 5з и сигналу С формируется сигнал записи в третью ступень - триггеры 7i,3-7.з. Соответствующая информация (четыре первых разряда) появляется на выходах триггеров по фронту сигнала (так как триггеры 7i/ од- нотактные).

Аналогичным образом по сигналу «О с выхода триггера Бк с помощью элемента 9к формируется сигнал записи, по которому информация появляется на выходах триггеров четвертой ступени.

с Параллельно входная информация записывается через каждые четыре такта в од- нотактные триггеры 7 первой ступени.

Когда сигнал «О кольцевого регистра появляется на выходах I2i коммутаторы 8i-8к соединяют выходы последнего яруса 0 триггеров 7|.к-7к.к с входами О-триггеров 6|-6к. При этом первый разряд появляется на выходе 2 регистра по срезу синхроимпульса.

После этого триггеры 6i-6к пересоединяются последовательно и информация вы- водится на выход 2 последовательно.

Для уменьщения потребляемой мощности на вход триггера 6i подается сигнал «О, что позволяет исключить переключение триггеров третьей группы при отсутствии на них Q полезной информации.

Таким образом, предлагаемый сдвиговый регистр осуществляет задержку входной информации на 16 тактов. Аналогичным образом реализуется регистр в случае разрядности К .

3 По сравнению с известным, для реализации которого требуется 2/( одноступенчатых D-триггеров, предлагаемый регистр реализуется на основе 3/С двухступенчатых триггеров, К одноступенчатых триггеров, К коммутаторов и К элементов ИЛИ-НЕ (по сЛож- 0 ности две последние группы элементов эквиваленты К. одноступенчатым триггерам), т. е. на К (К+7) одноступенчатых триггерах. Поэтому выигрыщ в аппаратурных затратах составляет (при ) 2К/() .с раз. Во столько же раз сокращается площадь БИС при интегральном исполнении регистра.

При работе с тактовой частотой F мощность, потребляемая известным регистром (для КМДП реализации),

где С - перезаряжаемая емкость при переключении одного простого D-тркге- гера;

и - напряжение питания. Для предлагаемого регистра потребляе- 55 мая мощность равна 7KCVJV, так как все К одноступенчатых триггеров переключается с частотой F/K. Выигрыш в потребляемой мощности (при ) составляет 2К/7.

Формула изобретения

Регистр сдвига, содержащий три группы по К двухступенчатых 1-триггеров, К, 5, 6,..., /С - разрядность регистра, причем в первой группе Д-вход /-го двухступенчатого D-триггера, , К соединен с выходом ({).го двухступенчатого триггера, а D-вход первого двухступенчатого D-тригге- ра является информационным входом регистра, в второй группе Р-вход г -го двухступенчатого D-триггера, , /С-1, соединен с выходом (t4-l)-ro двухступенчатого D- триггера, выход К-го двухступенчатого D- триггера третьей группы является информационным выходом регистра, С-входы каждого двухступенчатого D-триггера каждой группы являются синхронизирующим входом регистра, отличающийся тем, что, с целью упрощения регистра, он содержит К групп по К одноступенчатых D-триггер.ов, К коммутаторов и К элементов ИЛИ-НЕ, выходы которых соединены с С-входами соответствующих одноступенчатых D-триггеров каждой группы, а первые и вторые входы -

с выходами и С-входами соответствующих

двухступенчатых D-триггеров второй группы,

выход г-го одноступенчатого D-триггера,

,К-Т в каждой группе . соединены с

D-входами (/4-1)-го одноступенчатого D- триггера, D-вход первого одноступенчатою D-триггера каждой группы соединен с выходом соответствуюц1,его двухступенчатого D-тригрера первой группы, а выход последнего одноступенчатого D-триггера каждой

группы соединен с первым информационным входом соответствующего коммутатора, второй информационный вход /-го коммутатора, ,К соединен с выходом (/-1)-го двухступенчатого -триггера третьей группы, второй информационный вход первого коммутатора соединен с щиной нулевого потен циала регистра сдвига, а выходы коммутаторов соединены с D-входами соответствующих двухступенчатых D-триггеров тре тьей группы, выход первого двухступенчй

того D-триггера второй группы соединен D-входом /С-го двухступенчатого /.- -тригге ра данной группы и с управляю: 111ми вхс дамк коммутаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор-накопитель | 1986 |

|

SU1354185A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1084896A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для ввода информации | 1989 |

|

SU1695287A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство цикловой синхронизации | 1979 |

|

SU843273A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

Изобретение относится к вычислительной технике и может быть использовано в многоразрядных устройствах сдвига информации. Целью изобретения является упрощение регистра сдвига, которое позволяет уменьшить площадь, занимаемую регистром, a также снизить потребляемую регистром мощность при интегральном исполнении регистра. Поставленная цель достигается путем использования в регистре одноступенчатых Д-триггеров и последовательно-параллель- но-последовательной организации регистра. Сдвиг информации в одноступенчатых D- триггерах осуществляется с частотой, в К раз меныией тактовой (A - разрядность регистра). В состав регистра, помимо К групп одноступенчатых триггеров 7, по К триггеров в каждой группе, входят две группы 4 к 6 КЗ К двухступенчатых триггеров, каждая для последовательного приема (4) и выдачи (6) информации, К. коммутаторов 8 и группа из К двухступенчатых триггеров 5 для организации параллельного сдвига в группах одноступенчатых триггеров 7. Выигрыш в аппаратурных затратах может быть получен при /(7, a по потребляемой мощности - при /(4. 1 ил. (Л О5 4 o а

| Алексенко А | |||

| Г., Шагурин И | |||

| И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, с | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Соловьев Г | |||

| Н | |||

| Арифметические устройства ЭВМ | |||

| - М.: Энергия, 1978; с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-07—Публикация

1987-07-17—Подача