Изобретение относится к вычислительной технике и может быть использовано для увеличения объема памяти при построении вычислительных систем на базе микроЭВК.

Целью изобретения является сокращение аппаратурных затрат устройства, необходимых для создания многоблочнок памяти большой емкости.

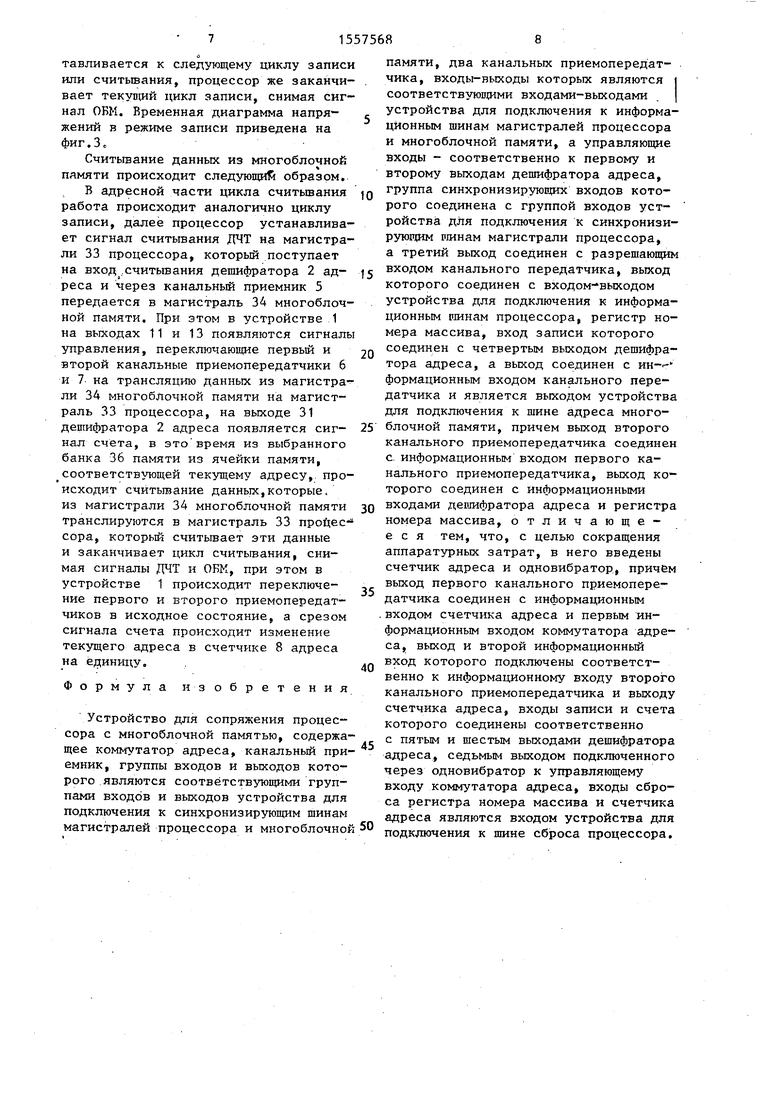

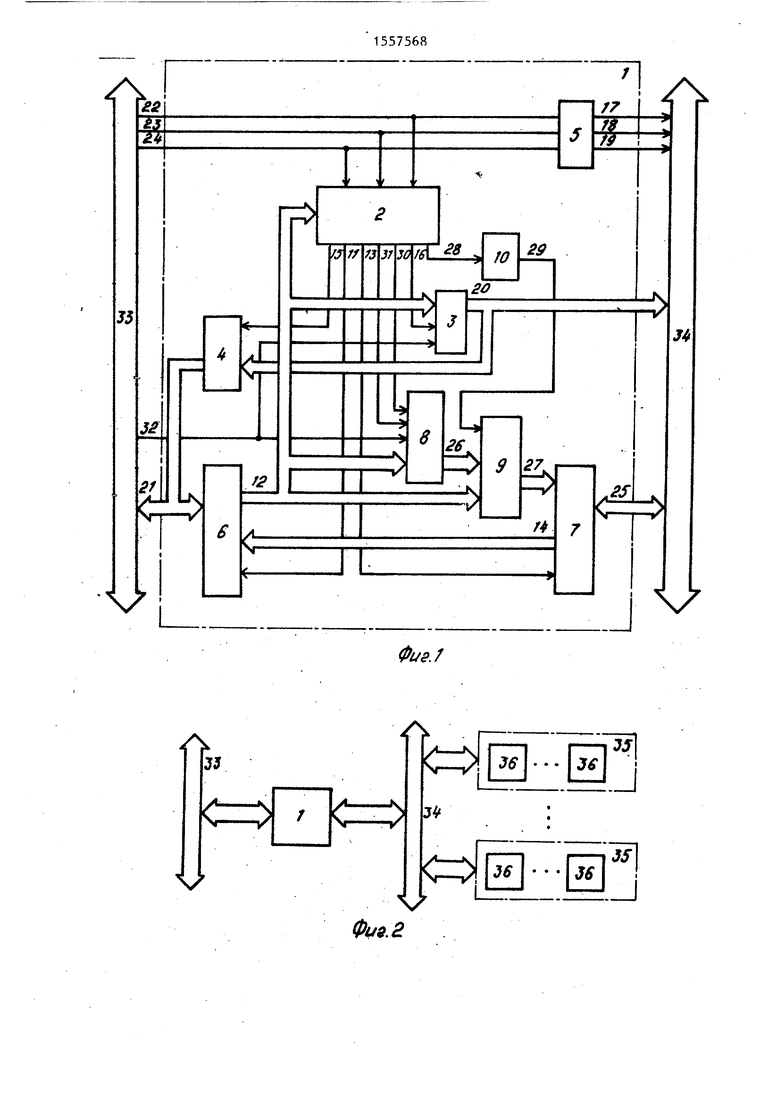

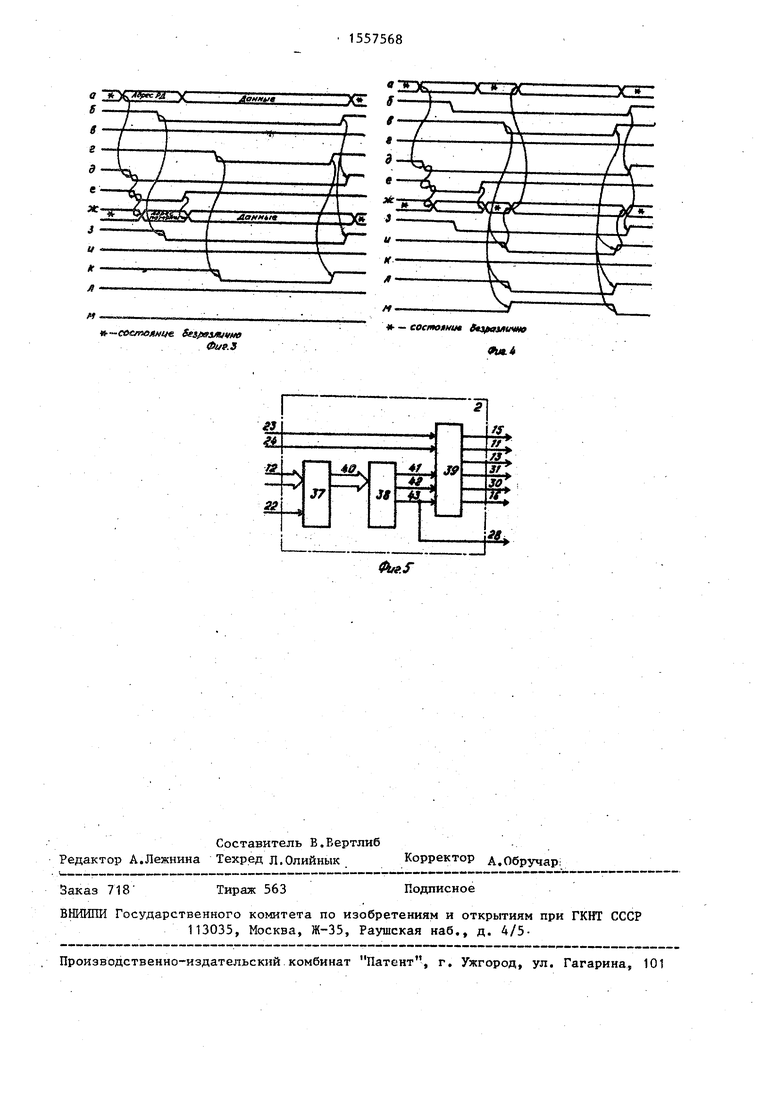

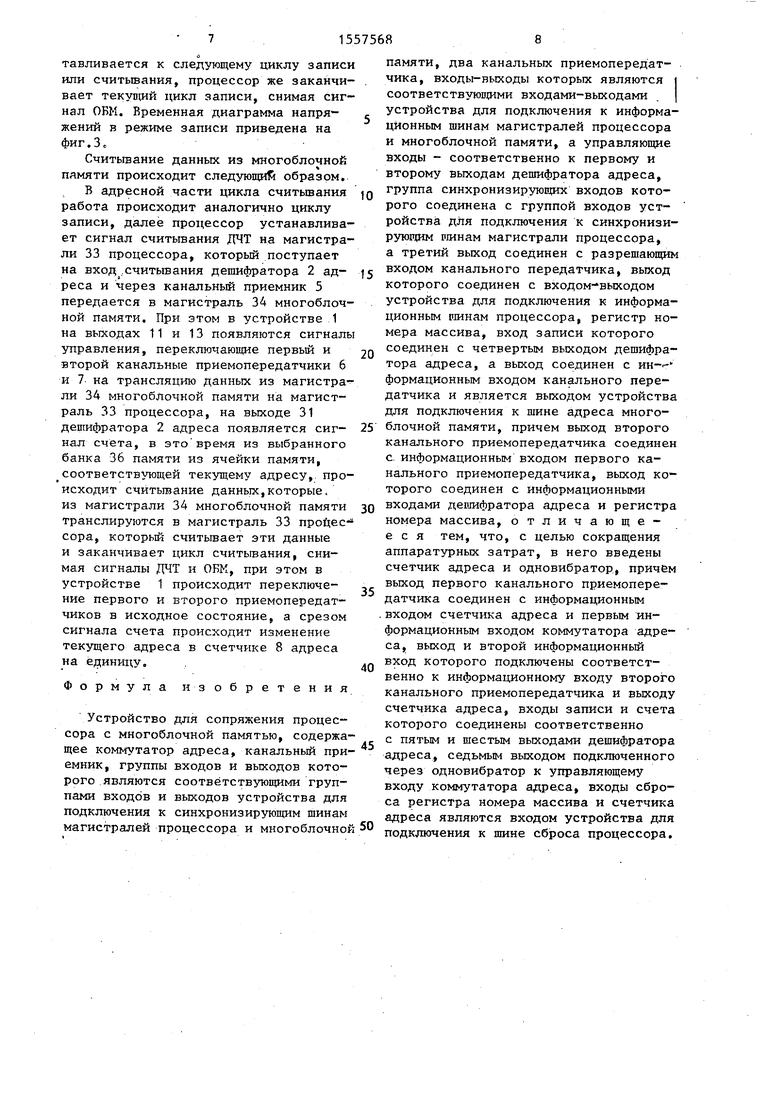

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - структура комплекса, использующего устройство; на Фиг.З и 4 - временные диаграммы работы устройства в циклах записи и считывания; на фиг.5 - пример функциональной схемы дешифратора адреса.

Устройство 1 (фиг.1) содержит дешифратор 2 адреса, регистр 3 номера массива, канальный передатчик 4, канальный приемник 5, первый и второй канальные приемопередатчики 6 и 7, счетчик 8 адреса, коммутатор 9 адреса, одновибратор 10, первый выход 11 дешифратора 2 адреса, выход 12 ка- нального приемопередатчика 6, второй выход 13 дершфратора 2 адреса, выход 14 канального приемопередатчика 7, третий и четвертый выходы 15 и 16 дешифратора 2 адреса, выходы 17, 18 и 19 канального приемника 5, выход 20 регистра 3 номера массива, информационные входы-выходы 21 устройства 1, входы 22, 23 и 24 сигналов синхронизации адреса, считывания и записи группы входов канального приемника 5 информационные входы-выходы 25 второго канального приемопередатчика 7, выходы 26 счетчика 8 адреса, выходы 27 коммутатора 9 адреса, седьмой выход 28 дешифратора 2 адреса, выход 29 одновибратора 10, пятый и шестой выходы 30 и 31 дешифратора адреса, вход 32 сброса устройства 1, магистраль 33 процессора и магистраль 34 многоблоч- ной памяти процессора.

QS

Устройство 1 сопряжения предназначено для сопряжения процессора с многоблочной памятью (фиг.2), содержащей блоки 35 памяти, состоящие из узлов (банков) 36 памяти.

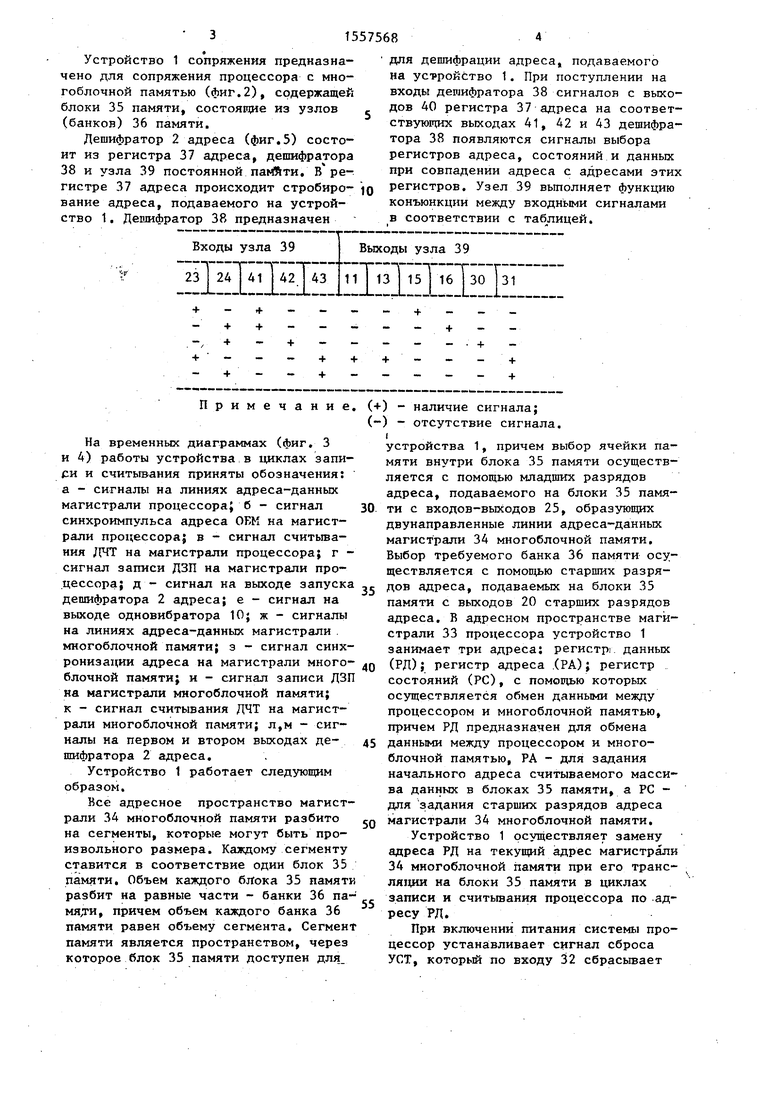

Дешифратор 2 адреса (фиг.5) состоит из регистра 37 адреса, дешифратора 38 и узла 39 постоянной памяти. В регистре 37 адреса происходит стробиро- вание адреса, подаваемого на устройство 1. Дешифратор 38 предназначен

для дешифрации адреса, подаваемого на устройство 1. При поступлении на входы дешифратора 38 сигналов с выходов АО регистра 37 адреса на соответствующих выходах 41, 42 и 43 дешифратора 38 появляются сигналы выбора регистров адреса, состояний и данных при совпадении адреса с адресами этих регистров. Узел 39 выполняет функцию конъюнкции между входными сигналами в соответствии с таблицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Устройство сопряжения процессора с многоблочной памятью | 1989 |

|

SU1702383A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

Изобретение относится к вычислительной технике и может быть использовано для увеличения объема памяти при построении вычислительных систем на базе микроЭВМ. Целью изобретения является сокращение аппаратурных затрат устройства при создании многоблочной памяти процессора. Поставленная цель достигается тем, что в устройство, содержащее коммутатор адреса, дешифратор адреса, регистр номера массива, канальный передатчик, канальный приемник, первый и второй канальные приемопередатчики, введены счетчик адреса и одновибратор. 5 ил., 1 табл.

Примечание.

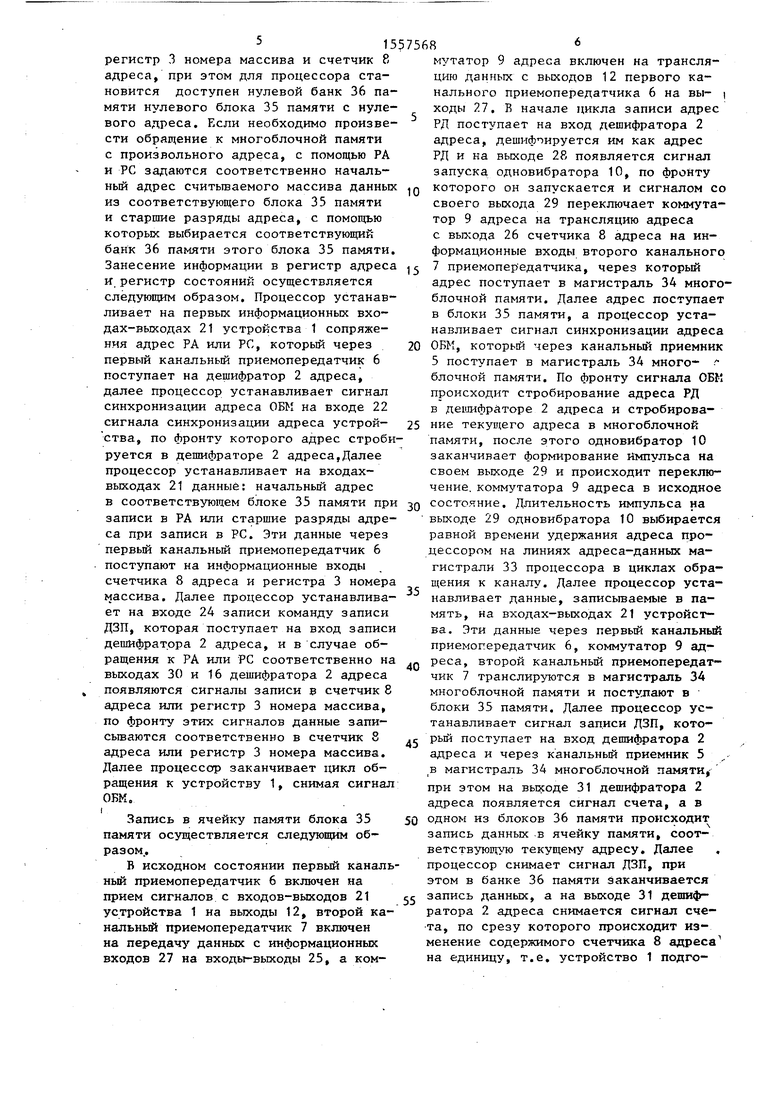

На временных диаграммах (фиг. 3 и 4) работы устройства в циклах записи и считывания приняты обозначения: а - сигналы на линиях адреса-данных магистрали процессора} б - сигнал синхроимпульса адреса OEM на магистрали процессора; в - сигнал считывания ДЧТ на магистрали процессора; г - сигнал записи ДЗП на магистрали процессора; д - сигнал на выходе запуска дешифратора 2 адреса; е - сигнал на выходе одновибратора 10; ж - сигналы на линиях адреса-данных магистрали многоблочной памяти; э - сигнал синхронизации адреса на магистрали многоблочной памяти; и - сигнал записи ДЗП на магистрали многоблочной памяти; к - сигнал считывания ДЧТ на магистрали многоблочной памяти; л,м - сигналы на первом и втором выходах дешифратора 2 адреса.

Устройство 1 работает следующим образом.

Все адресное пространство магистрали 34 многоблочной памяти разбито на сегменты, которые могут быть произвольного размера. Каждому сегменту ставится в соответствие один блок 35 памяти. Объем каждого блока 35 памятк разбит на равные части - банки 36 па- мя,ти, причем объем каждого банка 36 памяти равен объему сегмента. Сегмент памяти является пространством, через которое блок 35 памяти доступен для

(+) - наличие сигнала;

(-) - отсутствие сигнала, i

устройства 1, причем выбор ячейки памяти внутри блока 35 памяти осуществляется с помощью младших разрядов адреса, подаваемого на блоки 35 памя0 ти с входов-выходов 25, образующих двунаправленные линии адреса-данных магистрали 34 многоблочной памяти. Выбор требуемого банка 36 памяти осуществляется с помощью старших разря5 Дов адреса, подаваемых на блоки 35 памяти с выходов 20 старших разрядов адреса. В адресном пространстве магистрали 33 процессора устройство 1 занимает три адреса: регистр данных (РД); регистр адреса (РА); регистр состояний (PC), с помощью которых осуществляется обмен данными между процессором и многоблочной памятью, причем РД предназначен для обмена данными между процессором и многоблочной памятью, РА - для задания начального адреса считываемого массива данных в блоках 35 памяти, a PC - для задания старших разрядов адреса магистрали 34 многоблочной памяти.

Устройство 1 осуществляет замену адреса РД на текущий адрес магистрали 34 многоблочной памяти при его трансляции на блоки 35 памяти в циклах записи и считывания процессора по адресу РД.

При включении питания системы процессор устанавливает сигнал сброса УСТ, который по входу 32 сбрасывает

0

5

0

5

регистр 3 номера массива и счетчик 8 адреса, при этом для процессора становится доступен нулевой банк 36 памяти нулевого блока 35 памяти с нулевого адреса. Если необходимо произвести обращение к многоблочной памяти с произвольного адреса, с помощью РА и PC задаются соответственно начальный адрес считываемого массива данных из соответствующего блока 35 памяти и старшие разряды адреса, с помощью которых выбирается соответствующий банк 36 памяти этого блока 35 памяти.

Занесение информации в регистр адреса 7 приемопередатчика, через который

и регистр состоянии осуществляется следующим образом. Процессор устанавливает на первых информационных входах-выходах 21 устройства 1 сопряжения адрес РА или PC, который через первый канальный приемопередатчик 6 поступает на дешифратор 2 адреса, далее процессор устанавливает сигнал синхронизации адреса ОБМ на входе 22 сигнала синхронизации адреса устройства, по фронту которого адрес строби руется в дешифраторе 2 адреса,Далее процессор устанавливает на входах- выходах 21 данные: начальный адрес в соответствующем блоке 35 памяти при записи в РА или старшие разряды адреса при записи в PC. Эти данные через первый канальный приемопередатчик 6 поступают на информационные входы счетчика 8 адреса и регистра 3 номера массива. Далее процессор устанавливает на входе 24 записи команду записи ДЗП, которая поступает на вход записи дешифратора 2 адреса, и в случае обращения к РА или PC соответственно на выходах 30 и 16 дешифратора 2 адреса появляются сигналы записи в счетчик 8 адреса или регистр 3 номера массива, по фронту этих сигналов данные записываются соответственно в счетчик 8 адреса или регистр 3 номера массива. Далее процессор заканчивает цикл обращения к устройству 1, снимая сигнал ОБК„

Запись в ячейку памяти блока 35 памяти осуществляется следующим образом..

В исходном состоянии первый канальный приемопередатчик 6 включен на прием сигналов с входов-выходов 21 устройства 1 на выходы 12, второй канальный приемопередатчик 7 включен на передачу данных с информационных входов 27 на входы-выходы 25, а ком

мутатор 9 адреса включен на трансляцию данных с выходов 12 первого канального приемопередатчика 6 на вы- | ходы 27. В начале цикла записи адрес РД поступает на вход дешифратора 2 адреса, дешифрируется им как адрес РД и на выходе 28 появляется сигнал запуска одновибратора 10, по фронту которого он запускается и сигналом со своего выхода 29 переключает коммутатор 9 адреса на трансляцию адреса с выхода 26 счетчика 8 адреса на информационные входы второго канального

0

5

0

адрес поступает в магистраль 34 многоблочной памяти. Далее адрес поступает в блоки 35 памяти, а процессор устанавливает сигнал синхронизации адреса ОБМ, который через канальный приемник 5 поступает в магистраль 34 много- блочной памяти. По фронту сигнала ОБМ происходит стробирование адреса РД в дешифраторе 2 адреса и стробирование текущего адреса в многоблочной памяти, после этого одновибратор 10 заканчивает формирование импульса на своем выходе 29 и происходит переключение, коммутатора 9 адреса в исходное состояние. Длительность импульса на выходе 29 одновибратора 10 выбирается равной времени удержания адреса процессором на линиях адреса-данных магистрали 33 процессора в циклах обращения к каналу. Далее процессор устанавливает данные, записываемые в память, на входах-выходах 21 устройства. Эти данные через первый канальный приемопередатчик 6, коммутатор 9 адреса, второй канальный приемопередатчик 7 транслируются в магистраль 34 многоблочной памяти и поступают в блоки 35 памяти. Далее процессор устанавливает сигнал записи ДЗП, кото5 РЫЙ поступает на вход дешифратора 2 адреса и через канальный приемник 5 в магистраль 34 многоблочной памяти,- при этом на выходе 31 дешифратора 2 адреса появляется сигнал счета, а в

0 одном из блоков 36 памяти происходит запись данных в ячейку памяти, соответствующую текущему адресу. Далее . процессор снимает сигнал ДЗП, при этом в банке 36 памяти заканчивается

е запись данных, а на выходе 31 дешифратора 2 адреса снимается сигнал сче- та, по срезу которого происходит изменение содержимого счетчика 8 адреса1 на единицу, т.е. устройство 1 подго-

5

0

тавливается к следующему циклу записи или считывания, процессор же заканчивает текущий цикл записи, снимая сигнал ОБМ. Временная диаграмма напря- жений в режиме записи приведена на фиг.3„

Считывание данных из многоблочной памяти происходит следующим образом.

В адресной части цикла считывания работа происходит аналогично циклу записи, далее процессор устанавливает сигнал считывания ДЧТ на магистрали 33 процессора, который поступает на вход считывания дешифратора 2 ад- реса и через канальный приемник 5 передается в магистраль 34 многоблочной памяти. При этом в устройстве 1 на выходах 11 и 13 появляются сигналы управления, переключающие первый и второй канальные приемопередатчики 6 и 7 на трансляцию данных из магистрали 34 многоблочной памяти на магистраль 33 процессора, на выходе 31 дешифратора 2 адреса появляется сиг- нал счета, в это время из выбранного банка 36 памяти из ячейки памяти, Соответствующей текущему адресу, происходит считывание данных,которые, из магистрали 34 многоблочной памяти транслируются в магистраль 33 процес- сора, который считывает эти данные и заканчивает цикл считывания, снимая сигналы ДЧТ и ОБК, при этом в устройстве 1 происходит переключе- ние первого и второго приемопередатчиков в исходное состояние, а срезом сигнала счета происходит изменение текущего адреса в счетчике 8 адреса на единицу.

Формула изобретения

45

Устройство для сопряжения процессора с многоблочной памятью, содержащее коммутатор адреса, канальный приемник, группы входов и выходов которого являются соответствующими группами входов и выходов устройства для подключения к синхронизирующим шинам магистралей процессора и многоблочной 50

5 0

5

0

памяти, два канальных приемопередатчика, входы-выходы которых являются | соответствующими входами-выходами . | устройства для подключения к информационным шинам магистралей процессора и многоблочной памяти, а управляющие входы - соответственно к первому и второму выходам дешифратора адреса, группа синхронизирующих входов которого соединена с группой входов устройства для подключения к синхронизирующим шинам магистрали процессора, а третий выход соединен с разрешающим входом канального передатчика, выход которого соединен с входом-выходом устройства для подключения к информационным шинам процессора, регистр номера массива, вход записи которого соединен с четвертым выходом дешифратора адреса, а выход соединен с ин---1 формационным входом канального передатчика и является выходом устройства для подключения к шине адреса многоблочной памяти, причем выход второго канального приемопередатчика соединен с информационным входом первого канального приемопередатчика, выход которого соединен с информационными входами дешифратора адреса и регистра номера массива, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены счетчик адреса и одновибратор, причем выход первого канального приемопередатчика соединен с информационным .входом счетчика адреса и первым информационным входом коммутатора адреса, выход и второй информационный вход которого подключены соответственно к информационному входу второго канального приемопередатчика и выходу счетчика адреса, входы записи и счета которого соединены соответственно с пятым и шестым выходами дешифратора адреса, седьмым выходом подключенного через одновибратор к управляющему входу коммутатора адреса, входы сброса регистра номера массива и счетчика адреса являются входом устройства для подключения к шине сброса процессора.

/Ч I

V

Л.

jj

V

/

л

$/./

Tojjf;

Jtf

Wj

J

J4«

J

Jtf

Is

.J

a HDQEESHX s

ъ-состояние. fes/ftwwe/v/л 0i/f.5

- состояние 8 зртлично Ял

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (ЬЬ) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С МНОГОБЛОЧНОЙ ПАМЯТЬЮ | |||

Авторы

Даты

1990-04-15—Публикация

1988-06-20—Подача