у

Ј

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах цифровых вычислительных систем.

Цель изобретения - уменьшение аппаратурных затрат и потребляемой мощности блока.

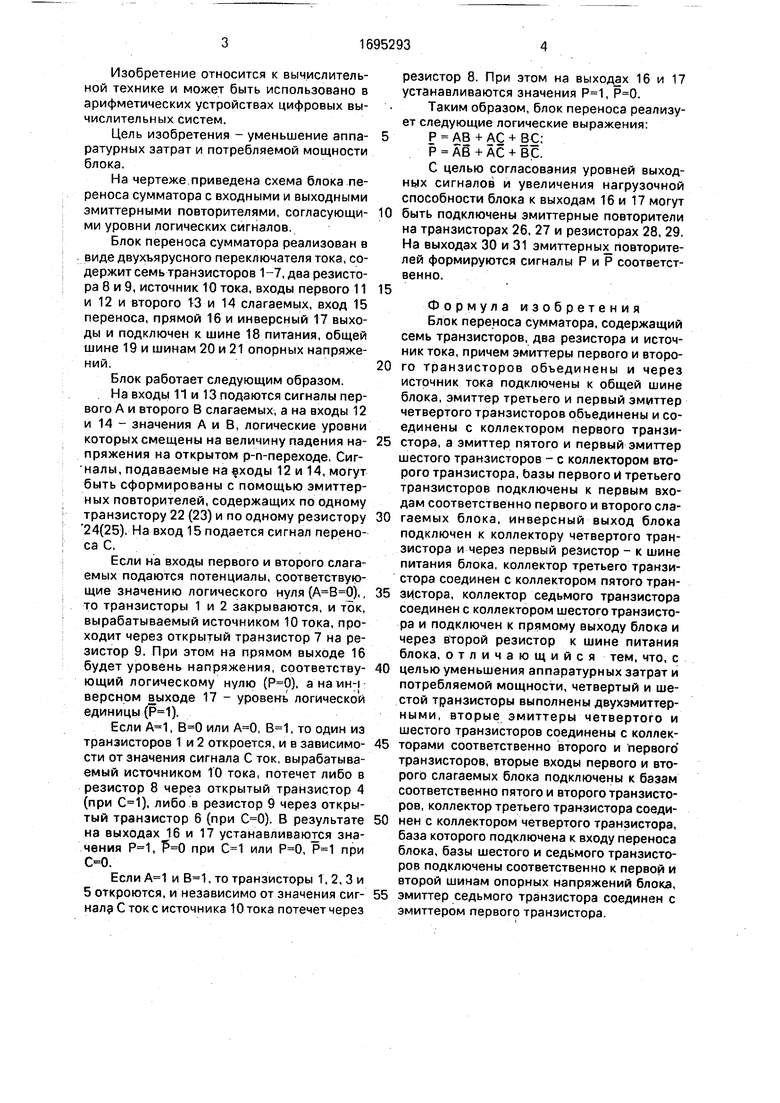

На чертеже приведена схема блока переноса сумматора с входными и выходными эмиттерными повторителями, согласующими уровни логических сигналов.

Блок переноса сумматора реализован в виде двухъярусного переключателя тока, содержит семь транзисторов 1-7, два резистора 8 и 9, источник 10 тока, входы первого 11 и 12 и второго 13 и 14 слагаемых, вход 15 переноса, прямой 16 и инверсный 17 выходы и подключен к шине 18 питания, общей шине 19 и шинам 20 и 21 опорных напряжений.

Блок работает следующим образом. На входы 11 и 13 подаются сигналы первого А и второго В слагаемых, а на входы 12 и 14 - значения А и В, логические уровни которых смещены на величину падения напряжения на открытом р-п-переходе. Сиг- налы, подаваемые на входы 12 и 14, могут быть сформированы с помощью эмиттер- ных повторителей, содержащих по одному транзистору 22 (23) и по одному резистору 24(25). На вход 15 подается сигнал переноса С.

Если на входы первого и второго слагаемых подаются потенциалы, соответствующие значению логического нуля (),, то транзисторы 1 и 2 закрываются, и ток, вырабатываемый источником 10 тока, проходит через открытый транзистор 7 на резистор 9. При этом на прямом выходе 16 будет уровень напряжения, соответствующий логическому нулю (), анамн-i версном выходе 17 - уровень логической единицы ().

Если , или , , то один из транзисторов 1 и 2 откроется, и в зависимости от значения сигнала С ток, вырабатываемый источником 10 тока, потечет либо в резистор 8 через открытый транзистор 4 (при ), либо в резистор 9 через открытый транзистор 6 (при ). В результате на выходах 16 и 17 устанавливаются значения , при или , при ОО.

Если и , то транзисторы 1, 2, 3 и 5 откроются, и независимо от значения сигнала С ток с источника 10 тока потечет через

резистор 8. При этом на выходах 16 и 17 устанавливаются значения , .

Таким образом, блок переноса реализует следующие логические выражения:

Р АВ + АС + ВС;

Р АВ +АС + ВС.

С целью согласования уровней выходных сигналов и увеличения нагрузочной способности блока к выходам 16 и 17 могут

быть подключены эмиттерные повторители на транзисторах 26, 27 и резисторах 28, 29. На выходах 30 и 31 эмиттерных повторите- лей формируются сигналы Р и Р соответственно.

Формула изобретения Блок переноса сумматора, содержащий семь транзисторов, два резистора и источник тока, причем эмиттеры первого и второго транзисторов объединены и через источник тока подключены к общей шине блока, эмиттер третьего и первый эмиттер четвертого транзисторов объединены и соединены с коллектором первого транзистора, а эмиттер пятого и первый эмиттер шестого транзисторов - с коллектором второго транзистора, оазы первого И третьего транзисторов подключены к первым входам соответственно первого и второго слагаемых блока, инверсный выход блока подключен к коллектору четвертого транзистора и через первый резистор - к шине питания блока, коллектор третьего транзистора соединен с коллектором пятого транзцстора, коллектор седьмого транзистора соединен с коллектором шестого транзистора и подключен к прямому выходу блока и через второй резистор к шине питания блока, отличающийся тем, что, с

целью уменьшения аппаратурных затрат и потребляемой мощности, четвертый и шестой транзисторы выполнены двухэмиттер- ными, вторые эмиттеры четвертого и шестого транзисторов соединены с коллекторами соответственно второго и первого транзисторов, вторые входы первого и второго слагаемых блока подключены к базам соответственно пятого и второго транзисторов, коллектор третьего транзистора соеди0 нен с коллектором четвертого транзистора, база которого подключена к входу переноса блока, базы шестого и седьмого транзисторов подключены соответственно к первой и второй шинам опорных напряжений блока,

5 эмиттер седьмого транзистора соединен с эмиттером первого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| Д-триггер с селектором на входе | 1989 |

|

SU1707741A1 |

| Логический элемент на переключении тока | 1988 |

|

SU1631714A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324103A1 |

| Амлитудный ограничитель импульсов | 1979 |

|

SU843205A1 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Ассоциативный запоминающий элемент | 1983 |

|

SU1130900A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах. Целью изобретения является уменьшение аппаратурных затрат и потребляемой мощности блока. Блок содержит семь транзисторов 1- 7, два резистора 8 и 9 и источник 10 тока, имеет входы первого 11, 12 и второго 13, 14 слагаемых, вход переноса 15, прямой 16 и инверсный 17 выходы и подключен к шине питания 18, общей шине 19 и шинам 20 и 21 опорных напряжений. 1 ил.

Авторы

Даты

1991-11-30—Публикация

1988-05-19—Подача