Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах для аппаратного вычисления функции Z VX2 + Y2c плавающей запятой.

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления корня квадратного в форме с плавающей запятой. ,

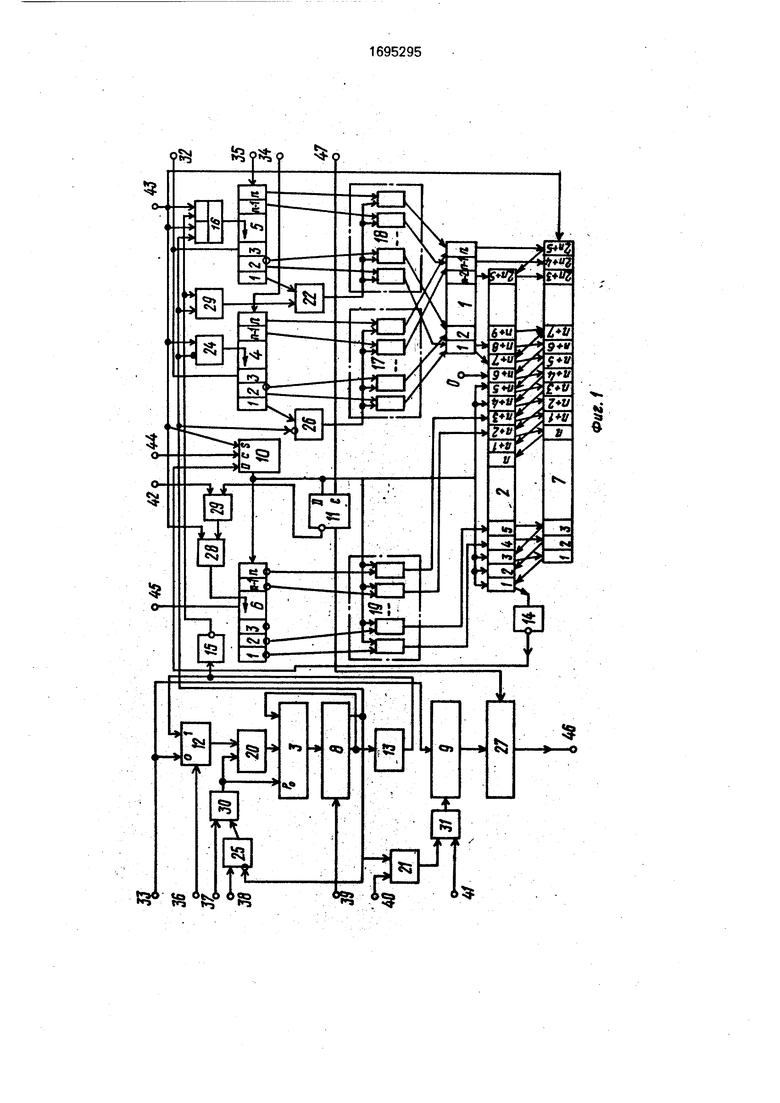

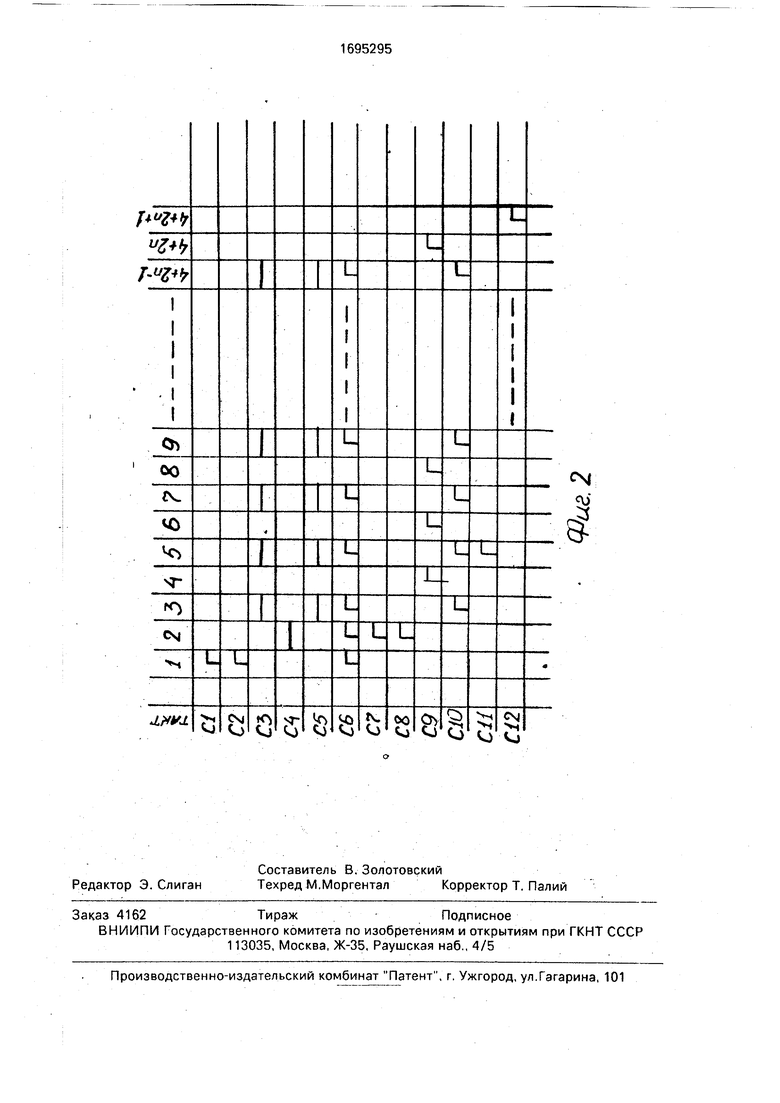

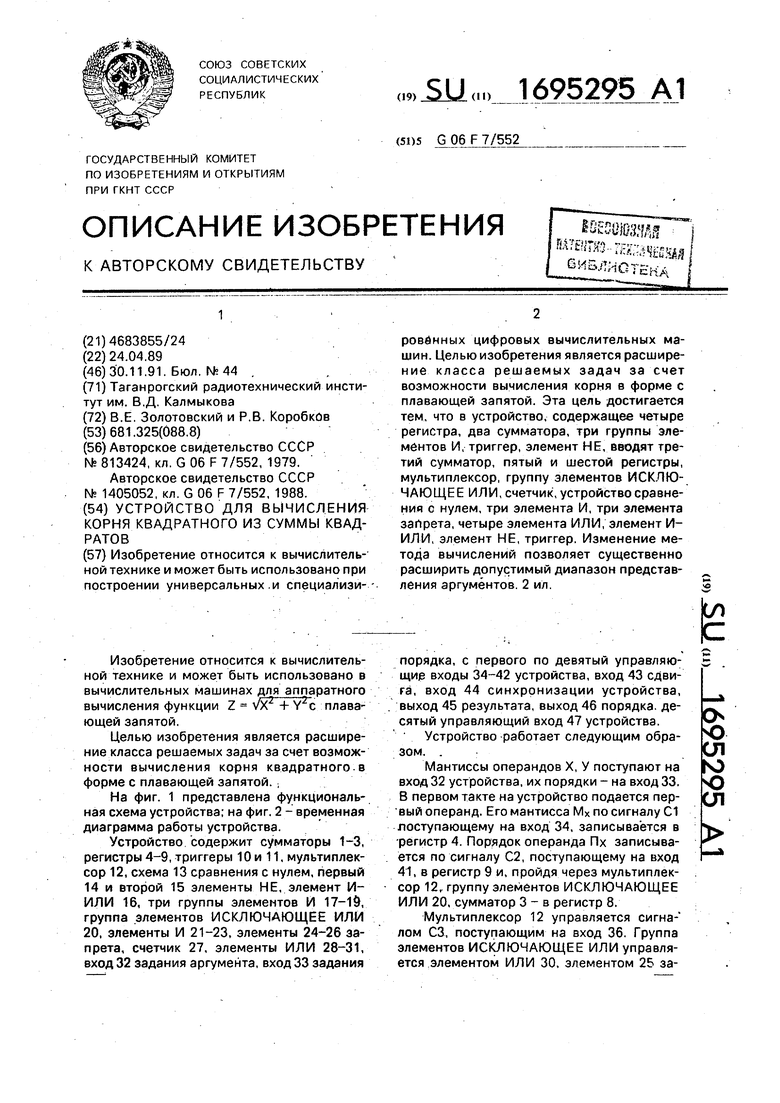

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит сумматоры 1-3, регистры 4-9, триггеры 10 и 11, мультиплексор 12, схема 13 сравнения с нулем, первый 14 и второй 15 элементы НЕ, элемент И- ИЛИ 16, три группы элементов И 17-19, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 20, элементы И 21-23, элементы 24-26 запрета, счетчик 27, элементы ИЛИ 28-31, вход 32 задания аргумента, вход 33 задания

порядка, с первого по девятый управляющие входы 34-42 устройства, вход 43 сдвига, вход 44 синхронизации устройства, выход 45 результата, выход 46 порядка десятый управляющий вход 47 устройства.

Устройство работает следующим образом. .

Мантиссы операндов X, У поступают на вход 32 устройства, их порядки - на вход 33. В первом такте на устройство подается первый операнд. Его мантисса Мх по сигналу С1 поступающему на вход 34, записывается в регистр 4. Порядок операнда Пх записывается по сигналу С2, поступающему на вход 41, в регистр 9 и, пройдя через мультиплексор 12Г группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 20, сумматор 3 - в регистр 8.

Мультиплексор 12 управляется сигна- лом СЗ, поступающим на вход 36. Группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ управляется элементом ИЛИ 30, элементом 25 запрета и управляющими сигналами С4, С5, поступающими на входы 37 и 38. Запись в регистр 8 управляется сигналом С6 по входу 39. Запись в регистр 9 управляется элементом ИЛИ 31, элементом И 21 и сигналом С7 по входу 40. К выходу регистра 8 подключена схема 13 сравнения с нулем. Во втором такте на входы 32 и 33 подается второй операнд. Его мантисса My по сигналу СЗ с входа 35 записывается в регистр 5, порядок Пу поступает на входы регистра 9 и мультиплексора 12. Выходы регистра А соединены с входами группы элементов И 17, управляемых элементом 26 запрета. Выходы регистра 5 соединены с входами группы элементов И 18, управляемых элементом И 22. Выходы групп элементов И 17

и 18 соединены с входами сумматора 1, выходы последнего - с входами сумматора 2.

К выходам последнего подключен регистр 7. Мантисса искомого результата Mz формируется в регистре 6, порядок flz - в счетчике 27. Вход управления сдвигом в регистре 6 управляется элементом И 23, элементом ИЛИ 28. Очередной разряд Mz формируется в триггере 10, представляющим собой От-триггер. Его вход D-соединен с выходом элемента НЕ 14, вход С соединен с входом 44, на который поступает сигнал С 9, вход S соединен с входом 43, на который поступает сигнал СЮ. Выход триггера 10 соединен с входом D триггера 11, вход С триггера 11 управляется сигналом С11 с входа 47. Элемент И 23 управляется сигналом С 12 с входа 42. Выходы регистра 6 соединены с входами группы элементов И 19. Выход схемы 13 сравнения с нулем через элемент НЕ 15 соединен с входом элемента И-ИЛИ 16. Элемент И 22 управляется элементом ИЛИ 29. Выход знакового разряда регистра 8 соединен с входом элемента 24 запрета. Мантисса результата Mz считывается с группы выходов 45, порядок Пг - с группы выходов 46.

Искомая величина Z должна вычисляться следующим образом:

М2-2П2 Л/1х-22Кх+Му-22Пу ,

Преобразуем полученное выражение. Пусть Пх Пу, тогда

Mz .2nZ 2ПХ VMЈ + (2-(ПХ - ПУ j;My)2

При Пх Пу имеем

Mz.2ny 2ny (2r(ny-nx).Mx)2

Следовательно, порядок результата равен большему порядку, мантисса числа, имеющего порядок меньшим, должна быть сдвинута на Пх-Пу (или Пу-Пх) разрядов вправо. По завершению вычислений мантисса результата может оказаться ненормализованной:

1 |Mzl 1,4.

Нормализация может потребовать сдвига мантиссы Z на один разряд вправо и увеличения порядка на одну единицу. По описанному алгоритму и работает предлагаемое устройство. В первом такте на входы

32 и 33 подается мантисса Мх и порядок Пх. По сигналу С1 MX запишется в регистр 4 (см. фиг. 2). Одновременно СЗ О, С4 О, С5 0, поэтому Пх проходит через мультиплексор 12, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 20, сумматор 3, поступает на входы регистра 8 (предварительно сброшенного в 0) и по сигналу С6 записывается в него. Одновременно Пх поступает на входы регистра 9 и по сигналу С2 записывается

в него.

Во втором такте на входы 32 и 33 подаются My, Пу. По сигналу С8 Мх запишется в регистр 5. Одновременно Пу проходит через мультиплексор 12 (СЗ 0) и поступает

на входы группы элементов ИСКЛЮЧАЮЩЕЕ ИЛ И 20. На входе 37 имеет С4 1. На первые входы сумматора 3 из регистра 8 поступает Пх, на вторые - инверсия Пу + 1 (устройство работает в дополнительных кодах). В сумматоре 3 формируется разность Пх-Пу, которая по сигналу С6 запишется в регистр 8. Знак результата поступает на элемент И 21, на вход 40 подается С7 1. Поэтому имеем: если Пх 5: Пу, RG 9 Пх;

если Пх Пу, RG 9 Пу. Т.е. в регистре 9 окажется записанным nz макс (Пх, Пу). В регистре 8 - разность Пх-Пу.

К началу третьего такта устройство готово к работе.

Выравнивание порядков X и У в явной форме не производится. Пусть Пх Пу, тогда sign (RG 8) 0, устройство сравнения с нулем генерирует 0. Поэтому элемент 26 запрета разрешает формирование первого

частичного квадрата MX ZKi(Mx). Элемент ИЛИ 29 генерирует 0. поэтому частичный квадрат My 2к(Му) равен 0. Пройдя через сумматор 1 iZ Ki(Mx), в третьем такте поступит на входы сумматора 2. На вторые

входы этого сумматора поступит код О (триггер 10 предварительно сброшен в 0), поэтому ZKi(Mx) пройдет через сумматор 2, не меняясь, и по сигналу СЮ запишется в регистр 7, триггер 10 перебросится в состо- ние 1. Одновременно в регистре 4 производится сдвиг влево. Выход схемы 13 сравнения с нулем соединен с младшим разрядом мультиплексора 12 направления 1. На остальные разряды направления 1 подаются нули. Сигнал СЗ 1, поэтому на выходе мультиплексора формируется число 0...001, сигнал С5 1 проходит через элемент 25 запрета, элемент ИЛИ 30 и поступает на входы группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 20. Число 0...01 поступает на входы сумматора 3 со знаком минус и разность Пх-Пу уменьшается на 1. По сигналу Сб уменьшенная разность записывается в регистр 8.

В четвертом такте (пусть разность Пх - - Пу - 1 еще не равна нулю) формируется первый разряд Mz- Разряды результата в устройстве формируются точно так же, как и в известном устройстве, с той лишь разницей, что старший разряд результата дополнительного записывается в триггер 11 по сигналу С11. Из группы элементов И 17 второй частичный квадрат ZKz (Mx), пройдя через сумматор 1, поступает на первые входы сумматора 2. На вторые его входы поступает первый частичный квадрат результата ZKi (Mz), при условии, что он равен 1, со знаком минус. Инверсия знака сумматора 2 поступает на вход D триггера 10 и по сигналу С9 в последний запишется точное значение первого разряда результата.

В пятом такте по сигналу С11 точное значение первого разряда результата запишется в триггер 11 По сигналу С10 первый разряд результата запишется в регистр б, триггер 10 установится в 1, содержимое регистра 8 опять уменьшится на 1. Такты 6, 7, 8, 9,..,,п выполняются аналогично тактам 4 и 5 (но сигнал С11 0). Как только RG 8 О, схема 13 сравнения с нулем генерирует сигнал 0. На вход мультиплексора 12 поступает число 0...000 и содержимое регистра 8 остается равным нулю. Элемент НЕ 15 генерирует сигнал 1, который проходит через элемент ИЛИ 29, в группе элементов И 18 начинается формирование частичных квадратов My, в регистре 5 по сигналам СЮ будут производится сдвиги. Если Пх Пу, то sign RG8 1 и элементы 26 и 24 запрета запретят формирование частичных квадратов и сдвиги в регистре 4. Элементы ИЛИ 29 и И 22 разрешат формирование частичных квадратов My, элемент И-ИЛИ 16 разрешит сдвиги в регистре 5. В остальном величина Mz будет формироваться так же, как и в предыдущем случае (диаграмма управляющих сигналов при этом не меняется). Сигнал С5 теперь не проходит через элемент 25 запрета и число 0...001

поступает на вход сумматора 3 с знаком плюс. В каждом цикле разность Пх-Пу по модулю уменьшается на 1. Как только RG8 0, начнется формирование частичных

5 квадратов Мх и сдвиги в регистре 4. В такте 4 + 2п завершится формирование последнего (п + 1)-го разряда Mz. Старшие п разрядов будут записаны в регистре 6, младший (п + 1)-й - в триггере 10. В следу10 ющем такте производится нормализация результатов. Для осуществления нормализации на вход 42 подается сигнал С12. Если Mz 1, в триггере 11 записан код 1, и сигнал С12 не проходит через элемент И 23. Старший

5 разряд Mz остается в разряде 1 регистра 6. Порядок из регистра 9 в комбинационном счетчике увеличивается на 1. Если Mz 1, Т 11 0, сигнал С12 проходит через элемент И 23. В регистре 6 происходит левый

0 сдвиг, младший разряд Mz из триггера 10 переписывается в разряд п регистра 6, Так как Mz 1 /2, для нормализации достаточно только одного сдвига. Порядок из регистра 9 в этом случае проходит через

5 счетчик 27, не меняясь.

Формула изобретения Устройство для вычисления корня квадратного из суммы квадратов, содержащее

0 первый и второй сумматоры, три группы элементов И, с первого по четвертый регистры, первые триггер и элемент НЕ, причем информационные входы первого и второго регистров соединены с входом за5 дания аргументов устройства, а первые управляющие входы - с одноименными управляющими входами устройства, прямые выходы разрядов с второго по n-й и инверсные выходы вторых разрядов перво0 го и второго регистров (где п - разрядность аргументов) подключены к первым входам элементов И соответственно первой и второй групп, выходы элементов И которых соединены с входами первого и второго

5 слагаемых первого сумматора, выходы младшмх (п-1)-го и n-го разрядов которого соединены с входами младших (2п + 4)-го и (2п + 5)-го разрядов четвертого регистра, выходы старших разрядов первого сум0 матора соединены с входами младших разрядов второго сумматора, входы синхронизации и установки первого триггера подключены к входам синхронизации и сдвига устройства соответственно, а ин5 формационный вход первого триггера соединен с выходом первого элемента НЕ,. вход которого соединен с выходом старшего разряда второго сумматора, выход первого триггера подключен к информационному входу третьего регистра, первым

входам элементов И третьей группы и входам первого, второго, третьего, (п + 3)-го, (п + 4)-го и (п +- 5)-го разрядов второго сумматора, инверсные выходы разрядов третьего регистра соединены с вторыми входами элементов И третьей группы, выходы элементов И которой подключены к входам разрядов, начиная с четвертого по (п + 2)-й второго сумматора, разрядные выходы четвертого регистра соединены с вторыми входами второго сумматора, разрядные выходы которого соединены с входами четвертого регистра со сдвигом на два разряда в сторону старших разрядов, управляющий вход четвертого регистра соединен с входом сдвига устройства, выходы третьего регистра соединены с выходом результата устройства, отличающееся тем, что, с целью расширения класса решающих задач за счет возможности вычисления корня в форме с плавающей запятой, в него введены третий сумматор, пятый и шестой регистры, комбинационный счетчик, второй триггер, схема сравнения с нулем, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, мультиплексор, четыре элемента ИЛИ, второй элемент НЕ, три элемента запрета, элемент И-ИЛИ, три элемента И, причем вход сдвига устройства подключен к первым входам первого элемента запрета и первого элемента ИЛИ, а также к первому и второму входам элемента И-ИЛИ, выход знакового разряда пятого регистра соединен с первыми входами первого элемента И, второго и третьего элементов запрета, с первым входом второго элемента ИЛИ, вторым входом первого элемента запрета и третьим входом элемента И-ИЛИ, четвертый вход которого объединен с вторым входом второго элемента ИЛИ и подключен к выходу второго элемента НЕ, вход которого и первый информационный вход мультиплексора объединены и подключены к выходу схемы сравнения с нулем, вход которой объединен с информационным входом третьего сумматора и подключен к информационному выходу пятого регистра, информационный вход которого соединен с выходом третьего сумматора, второй информационный вход которого соединен с

выходами элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ группы, информационные входы эле ментов ИЛИ которой соединены с выходом

мультиплексора, а управляющие входы и

вход младшего разряда третьего сумматора подключены к выходу третьего элемента ИЛИ, первый вход которого соединен с выходом второго элемента запрета, информационный вход шестого регистра и второй

информационный вход мультиплексора соединены с входом задания порядка аргумента устройства, управляющий вход и выход шестого регистра подключены к выходу четвертого элемента ИЛИ и информационному входу комбинационного счетчика соответственно, управляющий вход последнего из которых подключен к прямому выходу второго триггера, а выход является выходом порядка результата устройства,

первый вход четвертого элемента ИЛИ соединен с выходом первого элемента И, выходы первого элемента запрета и элемента И-ИЛИ соединены с вторыми управляющими входами соответственно первого и

второго регистров, выход первого разряда первого регистра соединен с вторым входом третьего элемента запрета, выход f которого подключен к вторым входам элементов И первой группы, выходы второго элемента ИЛИ и первого разряда второго регистра соединены соответственно с первым и вторым входами второго элемента И, выход которого подключен к вторым входам элементов И второй группы,

первый вход второго триггера соединен с выходом первого триггера,.а инверсный выход- с первым входом третьего элемента И, выход которого подключен к второму входу первого элемента ИЛИ, выход которого

соединен с управляющим входом третьего регистра, управляющий вход мультиплексора, вторые входы третьего элемента ИЛИ, второго элемента запрета, управляющий вход пятого регистра, вторые входы

первого элемента И, четвертого элемента и третьего элемента И соединены соответственно с третьего по девять управляющими входами устройства, второй вход второго триггера подключен к десятому уп0 равляющему входу устройства

9 & 9

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1988 |

|

SU1564617A2 |

| Устройство для выравнивания порядков чисел | 1982 |

|

SU1030798A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1465884A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления корня в форме с плавающей запятой. Эта цель достигается тем, что в устройство, содержащее четыре регистра, два сумматора, три группы элементов И, триггер, элемент НЕ, вводят третий сумматор, пятый и шестой регистры, мультиплексор, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик, устройство сравнения с нулем, три элемента И, три элемента запрета, четыре элемента ИЛИ, элемент И- ИЛИ, элемент НЕ, триггер. Изменение метода вычислений позволяет существенно расширить допустимый диапазон представления аргументов. 2 ил

9

С

J

3

CM

$

| Устройство для вычисления корняКВАдРАТНОгО из СуММы КВАдРАТОВ | 1979 |

|

SU813424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения корня из суммы квадратов | 1985 |

|

SU1405052A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-04-24—Подача