1

Изобретение относится к вычислительной технике и может--быть исполь- зованр в вычислителях для вычисления функции у с плавающей запятой.

Цель изобретения - расширение диапазона вычисления экспоненциальной функции.

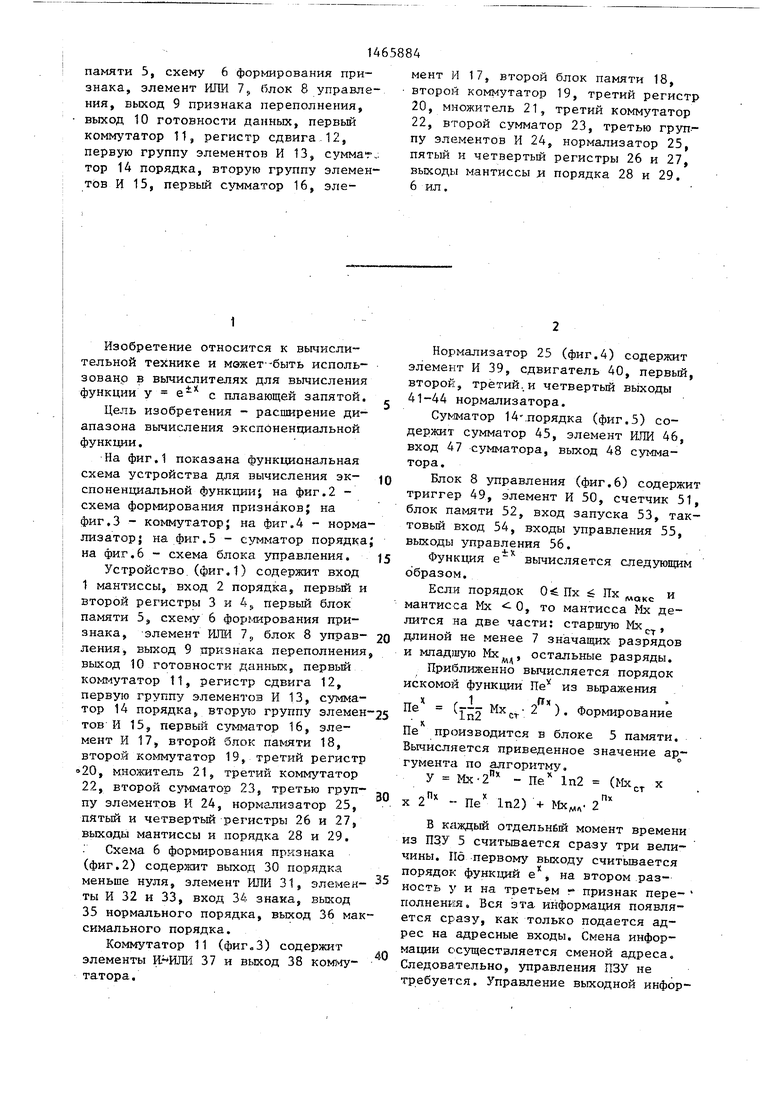

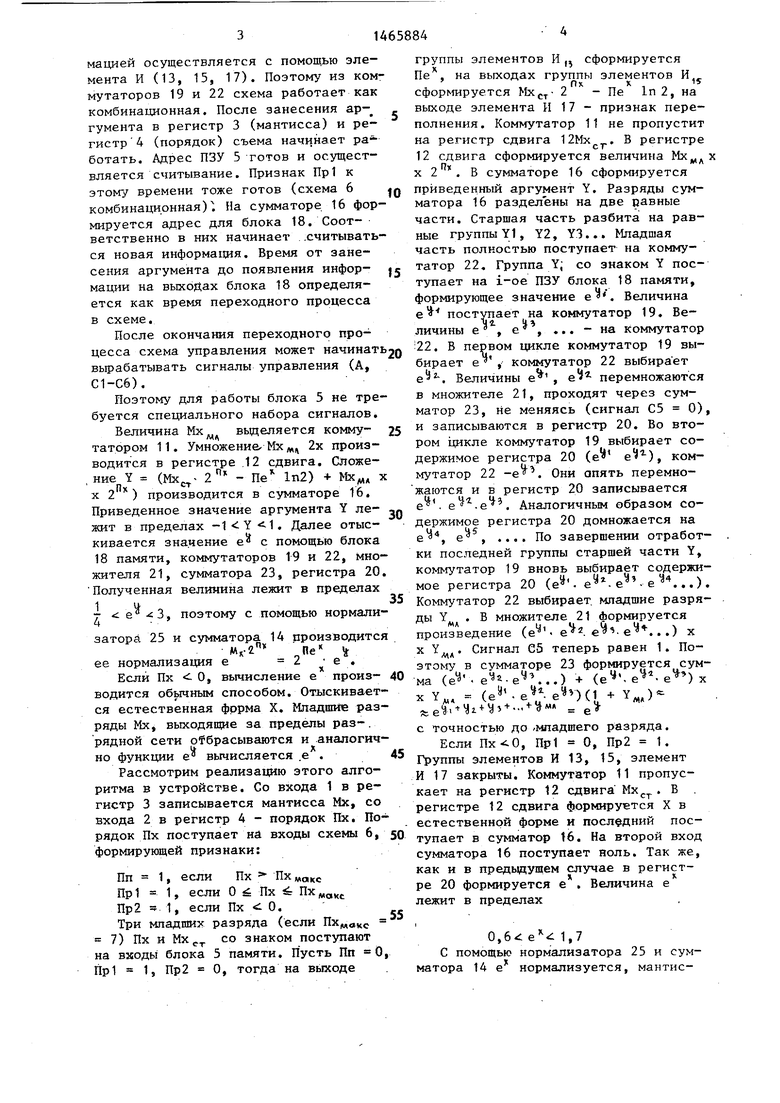

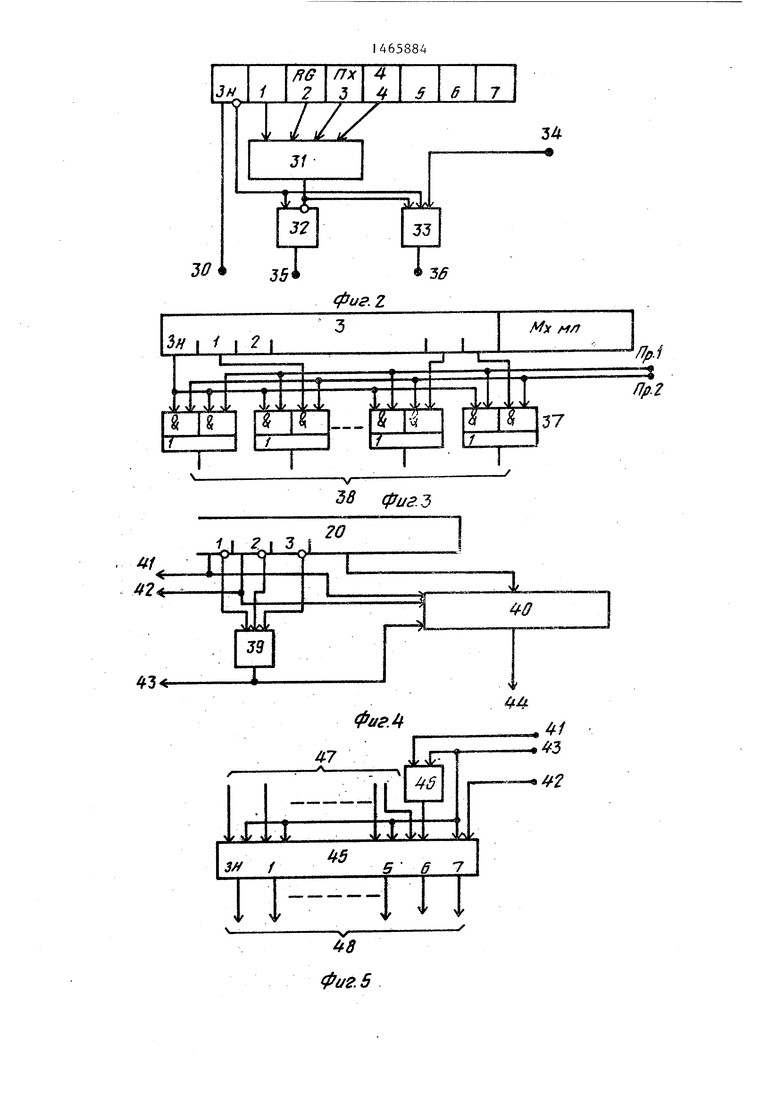

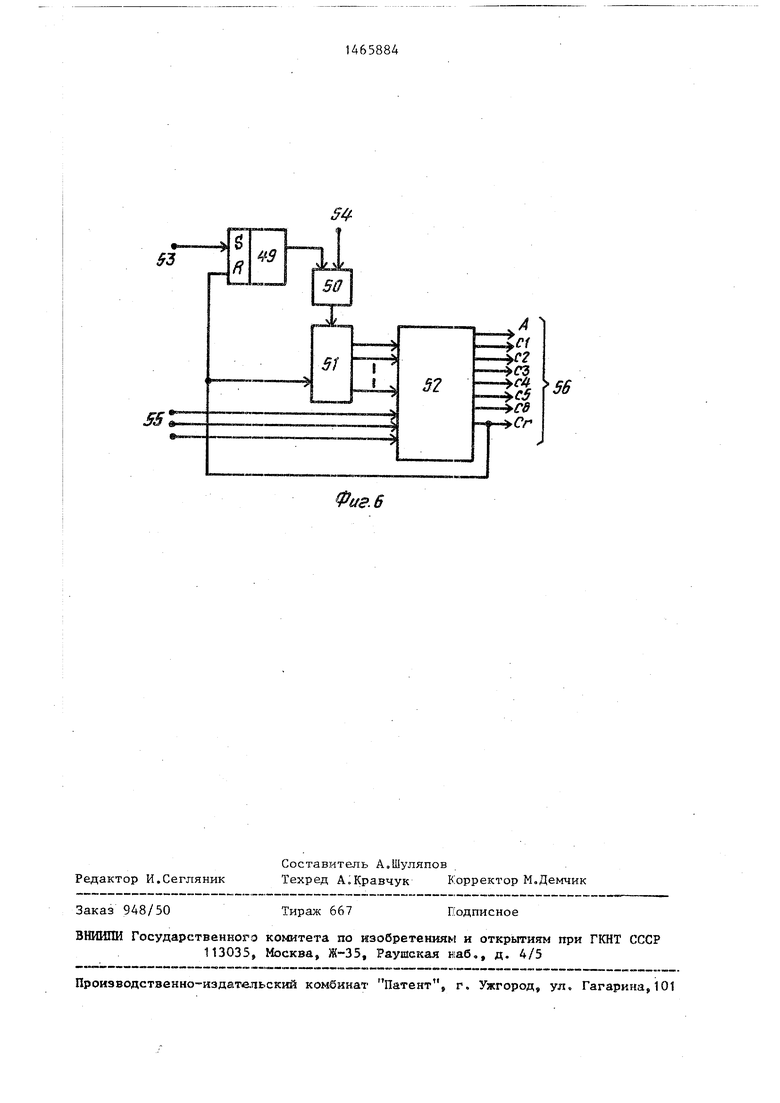

На фиг,1 показана функциональная схема устройства для зэычисления эк- споненциальной фyнкции на фиг.2 - схема формирования признаков; на фиг.З - коммутатор; на фиг.4 - нормализатор; на фиг.5 - с /мматор порядка на фиг.6 - схема блока управления.

Устройство.(фиг.1) содержит вход 1 мантиссы, вход 2 порядка, первый и второй регистры 3 и 4., первый блок памяти 5, схему 6 формирования признака, элемент ИЛИ 7., блок 8 управ- Ленин, выход 9 признака переполнения выход 10 готовности данных, первый коммутатор 11, регистр сдвига 12, первую группу элементов И 13, сумматор 14 порядка, вторую группу элемен тов И 15J первый сумматор 16, элемент И 17, второй блок памяти 18, второй коммутатор 19, третий регистр , множитель 21, третий коммутатор 22, второй сумматор 23, третью группу элементов И 24, нормализатор 25, питый и четвертый регистры 26 и 27, выходы мантиссы и порядка 28 и 29.

Схема 6 формирования щ г1знака (фиг.2) содержит выход 30 порядка меньше нуля, элемент ИЛИ 31, элемен- ты И 32 и 33, вход 34 знака, вьпсод 35 нормального порядка, выход 36 максимального порядка.

Коммутатор 11 (фиг.З) содержит элементы И.«ИШi 37 и выход 38 ком1чу- татора.

Нормализатор 25 (фиг.4) содержит элемент И 39, сдвигатель 40, первый, второй, третий,и четвертый выходы 41-44 нормализатора.

Сумматор 14.порядка (фиг.5) содержит сумматор 45, элемент ИЛИ 46, вход 47 сумматора, выход 48 сумматора.

Блок 8 управления (фиг.6) содержит триггер 49, элемент И 50, счетчик 51, блок памяти 52, вход запуска 53, тактовый вход 54, входы управления 55, выходы управления 56.

4 V

Функция е- вычисляется следующим о бразом.

Если порядок 0 Пх :б Пх Q и мантисса Мх 0, то мантисса Мх делится на две части: старшую Мх длиной не менее 7 значащих разрядов и Мх, остальные разряды.

Приближенно вычисляется порядок искомой функции Пе из вьфажения

2 ). Формирование

Пе (jl- MX

Пе производится в блоке 5 памяти. Вычисляется приведенное значение аргумента по алгоритму.

Мх-2

Пх

- Пе 1п2 (Мх X

Пх

X 2 -- Пе 1п2) Ч Мх,. 2

В каждый отдельной момент времени из ПЗУ 5 считьюается сразу три вели- чины. По первому выходу считьшается порядок функгдий е, на втором разность у и на третьем - признак пере- полненкя. Вся эта информация появляется сразу, как только подается адрес на адресные входы. Смена информации осуществляется сменой адреса. Следовательно, управления ПЗУ не требуется. Управление выходной информацией осуществляется с помощью элемента И (13, 15, 17). Поэтому из коммутаторов 19 и 22 схема работает как комбинационная. После занесения ар- гумента в регистр 3 (мантисса) и регистр 4 (порядок) съема начинает работать. Адрес ПЗУ 5 готов и осуществляется считывание. Признак Пр1 к этому времени тоже готов (схема 6 комбинационная). На сумматоре. 16 формируется адрес для блока 18. Соответственно в них начинает .считываться новая информация. Время от занесения аргумента до появления инфор- мации на выходах блока 18 определяется как время переходного процесса в схеме.

После окончания переходного процесса схема управления может начинать вырабатывать сигналы управления (А, С1-С6).

Поэтому для работы блока 5 не требуется специального набора сигналов.

Величина Мх выделяется комму- татором 11. Умножение MX м 2х производится в регистре .12 сдвига. Сложе- , ние Y ( 2 - Пе 1п2) + МХд, х X 2 ) производится в сумматоре 16, Приведенное значение аргумента Y ле- жит в пределах . Далее отыскивается значение е с помощью блока 18 памяти, коммутаторов 19 и 22, множителя 21, сумматора 23, регистра 20. Полученная велинина лежит в пределах

1 U

J- : е 3, поэтому с помощью нормализатора 25 и сумматора 14 производится

W,-i Пе« IT ее нормализация е 2 - е ,

Если Пх О, вычисление е произ - водится обычным способом. Отыскивается естественная форма X. Мпадппге разряды MX, выходящие за пределы раз-. рядной сети ofбpacывaютcя и аналогично функции е вычисляется .е .

Рассмотрим реализацию этого алгоритма в устройстве. Со входа 1 в регистр 3 записывается мантисса Мх, со входа 2 в регистр 4 - порядок Их. Порядок Пх поступает на входы схемы 6, формирующей признаки:

Пп 1, если Пх Пх

макс

Пр 1 1, если О Пх Пх д.

Пр2 -1, если Пх 1 0.

Три младших разряда (если 7) Пх и МХр. со знаком поступают на входы блока 5 памяти. Пусть Пп 0, Пр1 1, Пр2 О, тогда на выходе

группы элементов И ,j сформируется Пе, на выходах группы элементов И...

П X

сформируется 2 - Пе In 2, на выходе элемента И 17 - признак переполнения. Коммутатор 11 не пропустит на регистр сдвига 12Мх.. В регистре 12 сдвига сформируется величина Мх X 2 . В сумматоре 16 сформируется приведенный аргумент Y. Разряды сумматора 16 разделены на две равные части. Старшая часть разбита на равные группы у1, Y2, Y3... Младшая часть полностью поступает на коммутатор 22. Группа Y; со знаком Y поступает на i-oe ПЗУ блока 18 памяти, формирующее значение е« . Величина е поступает на коммутатор 19. Величины е, , ... - на коммутатор :22. В первом цикле коммутатор 19 выбирает , коммутатор 22 выбирает е. Величины , е перемножаются в множителе 21, проходят через сумматор 23, не меняясь (сигнал С5 0) и записываются в регистр 20. Во втором 1щкле коммутатор 19 выбирает содержимое регистра 20 (е ), коммутатор 22 . Они опять перемно- жаются и в регистр 20 записывается . .. Аналогичным образом содержимое регистра 20 домножается на

. Л

По завершении отработки последней группы старшей части Y, коммутатор 19 вновь выбирает содержимое регистра 20 (. ... ) Коммутатор 22 выбирает, младшие разря

40 45

50

,

55

ды Y

В множителе 21 формируется

WA и,ч U Ч ч

произведение ( е . е «.. .) х

X Y. Сигнал С5 теперь равен 1. Поэтому в сумматоре 23 формируется сум- (еЧ . е .е ..) -f ( ) х

ма X Y

« (1

+ Y«.)

м«

. е с точностью до -младшего разряда. Если , Пр1 О, Пр2 1. Группы элементов И 13, 15, элемент И 17 закрыты. Коммутатор 11 пропускает на регистр 12 сдвига Мх.. В . регистре 12 сдвига формируется X в естественной форме и последний поступает в сумматор t6. На второй вход сумматора 16 поступает ноль. Так же, как и в предьщущем случае в регистре 20 формируется е . Величина е лежит в пределах

0,6-ie 1,7

С помощью нормализатора 25 и сумматора 14 е нормализуется, мантисса Me записывается в регистр 26 порядок Пе - в регистр 27.

Формула изобрете

н и я

25

30

Устройство для вычисления экспоненциальной функции, содержащее первый и второй регистры, первый и второй сумматоры, первый блок памяти, регистр сдвига, коммутатор и элемент И, причем выходы мпадших разрядов первого регистра соединены с первым информационным входом регистра сдвига

ого соединен с выходом первого комму- |татора, выход регистра сдвига соеди- |нен с входом первого слагаемого первого сумматора, отличающеес я тем, что, с ,. .„.„

апазона вычисления экспоненциальной функции, в него введены регистры с третьего по пятый, второй блок памяти, второй и третий коммутаторы, мно- :штель, сумматор порядка, нормализатор, блок управления, схема формирог;. :зания признаков, .группы элементов И : первой по третью и элемент ИЛИ, (1ричем вход -мантиссы устройства соединен с информационным входом перво- о регистра, выход знакового разряда Которого соединен с входом первого Доля адресного входа первого блока йамяти и информационными.входами пер- 1ЮГО коммутатора, выход знакового разряда первого регистра соединен с jJepBbiM входом схемы формирования при- наков, первый выход которого соеди- ен с первым входом ..элемента ИЛИ, 1|ыход которого соединен с входом при- нака переполнения блока управления i| выходом признака переполнения уст- 1|ойства, вькод знакового разряда вто- Itoro регистра соединен с вторым входом схемы формирования признака, пер- йым управляющим входом регистра сдви- , выходы младших разрядов .второго регистра соединены с входом второго г|оля адресного входа первого блока г{амяти, третьим входом схе;мы формирования признака, с вторым управляю- ° п1им входом регистра сдвига, второй Е|ЫХОД схемы формирования признака соединен с входом первого признака бло- Kia управления, первым управляющим

55

входом первого коммутатора, управляющими входами элементов И первой и второй групп и управляющим входом 5 элемента И, третий выход схемы формирования признаков соединен с входом второго признака блока управления и вторым управляющим входом первого коммутатора, выход порядка функции ё 10 первого блока памяти соединен с информационным входом сумматора порядка, выход которого соединен с информационным входом четвертого регистра выход

- . I;::Z °;: :I-TT:.::°разности первого блока памяти соединен с входом второго слагаемого первого сумматора, выходы знака и стар- целью расширения ди- .„ Разрядов которого соединены с ад« экспоненн а™1Г ° 1 Тс гГ° ° ° ° «

выход старших разрядов которого соединен с первым информационным входом второго коммутатора, выход которого соединен с первым информационным входом множителя, выход которого соединен с входом первого слагаемого второго сумматора, выход которого соединен с .входом третьего регистра, выход кото- рогб соединен с входом нормализатора, входом элементов И третьей группы и вторым информационным «ходом второго коммутатора, выходы ютадших разрядов второго блока памяти соединены с первым информационным входом третьего коммутатора, второй информационный - вход Которого соединен с выходом знака первого сумматора, выходы мпадших разрядов которого соединены с третьим информационным входом третьего коммутатора, выход которого соединен с вторым ин(|)ормационным входом множителя, выход нормализатора соединен с информа1 онным входом пятого регистра, выход которого соединен с выходом мантиссы устройства, выходы с первого по восьмой блока управления соединены соответственно с управляющими входами третьего коммутатора, множителя, третьего, четвертого и пятого регистров, элементов И третьей группы, второго коммутатора и выходом roTOBHocTi-t результата устройства, выход переполнения первого блока памяти соединен с входом элемента И, выход которого соединен с вторым входом элемента ИЛИ.

35

40

465884 6

входом первого коммутатора, управляющими входами элементов И первой и второй групп и управляющим входом 5 элемента И, третий выход схемы формирования признаков соединен с входом второго признака блока управления и вторым управляющим входом первого коммутатора, выход порядка функции ё 10 первого блока памяти соединен с информационным входом сумматора порядка, выход которого соединен с информационным входом четвертого регистра выход

. I;::Z °;: :I-TT:.::°34-в

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1564617A2 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

Изобретение относится к вычислительной технике и может быть исп- пользовано в вычислителях для вычисления функции у е- с плавающей запятой. Цель изобретения - расширение диапазона вычисления экспоненциальной функции. Устройство содержит вход 1 мантиссы, вход 2 порядка, первый и второй регистры 3 и 4, первый блок

3

J5

фиг.2

«

|/ d/

л .3

4i фиг 5

53

Т

Ъ6

My M/J

/./

J-i

i

J

I

37

/.

Фаг. 6

Редактор И.Сегляник

Составитель А.Шуляпов

Техред А.КравчукВ орректор М.Демчик

Заказ 948/50

Тираж 667

ВНШШИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-издате.11ь,ский комбинат Патент, г. Ужгород, ул. Гагарина, 101

ГСодписное

| Устройство для вычисления функции двоичной экспоненты | 1984 |

|

SU1238066A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1411740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-15—Публикация

1986-11-19—Подача