(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРНЯ

КВАДРАТНОГО ИЗ СУММЫ КВАДРАТСЖ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов | 1981 |

|

SU1001094A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1983 |

|

SU1116428A2 |

| Устройство для вычисления функции @ = @ + @ | 1983 |

|

SU1136153A1 |

| Устройство для вычисления квадратного корня из суммы квадратов трех чисел | 1985 |

|

SU1262488A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1986 |

|

SU1327097A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Устройство для вычисления зависимости @ | 1983 |

|

SU1145341A1 |

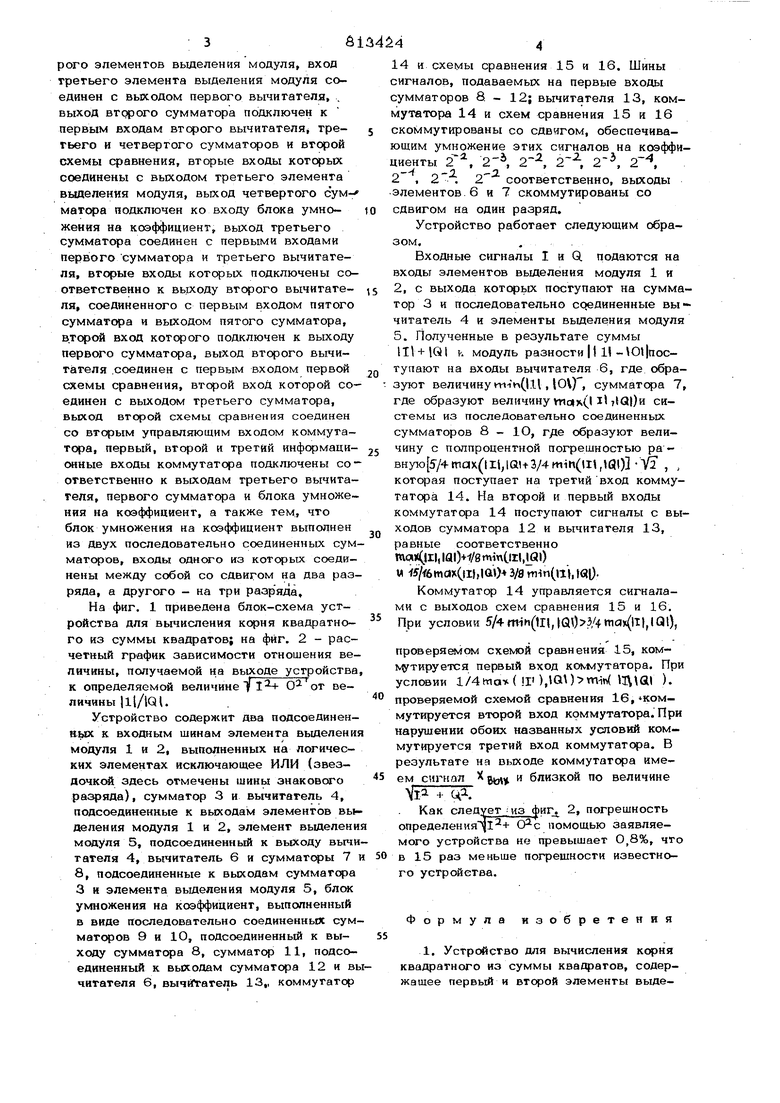

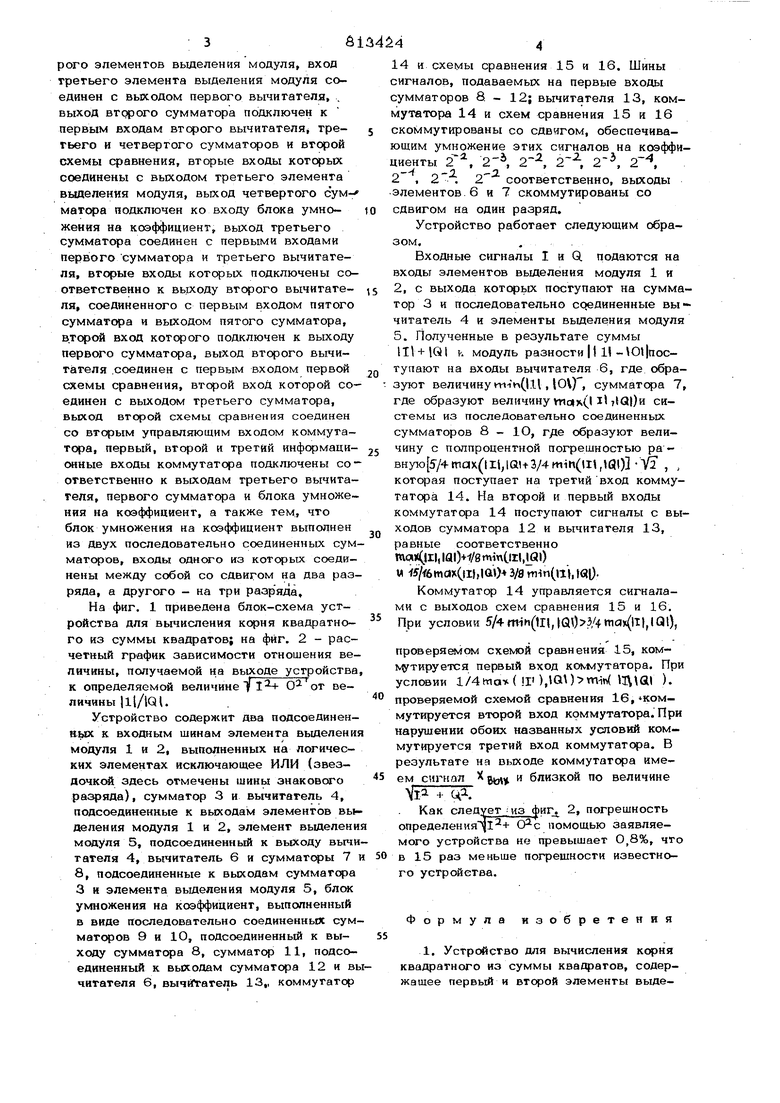

- Изобретение относится к измерительнсй технике и может быть использовано в системах обработки в реальном юмени, где требуется определять расстояния по заданным координатам на плоскости иди в пространстве, либо амплитуды комплексных сигналов, например в цифровых спектроанализаторах. Известны устрсйства, обеспечивающие определение величины корня KBai aTHCUo из суммы Двух величин, как универсальные ЭВМ, так и специализиро ванные устройства Ц . Однако известные устройства либо сложны, либо имеют недостаточное быстродействие (вследствие мнсяготактовости вычисления) или малую точность. Наиболее близким к предлагаемому является устройство, содержащее первый и второй элементы выделения модуля, входы которых соединены со входами устрЫ1ства, коммутатор, подсоединенный первым управляющим входом к выходу первой схемы сравнения и первый сумматор 27. Недостатком известного устрсЛства является низкая точность определения G . Так; есгги при I ll О или kil о погрешность определенияУ -t-Q равна нулю, то при 111 2|О|или i QI 2 она составляем около 12%. Цель изобретения - повышение точности определения Т/1 + Q. Поставленная цель достигается тем, что в устр«Лство для вычисления корня квадратного из суммы кваЩ)атов, содержащее первый и второй элементы выделения модуля, входы которых соеданены со входами устройства, коммутатор, поя соединенный управпяоошим входом к выходу первой схемы сравнения и первый сумматор, введены сумматоры, третий элемеит выделения модуля, вычига|Тели, вторая схема с ашсёния и блок умножения на коэффициент, причем вхооы второго сумматора к первого вычигателя подключены к выходам первого и вго рого элементов вьщеления модуля, вход третьего элемента вьшеления модуля соединен с выходом первого вычитателя, выход второго сумматора подключен к первым входам второго вычитaтeлЯi третьего и четвертого сумматоров и второй схемы сравнения, вторые входы котсрых соединены с выходом третьего элемента выделения модуля, выход четвертого сум- матора подключен ко входу блока умножения на коэффициент, выход третьего сумматора соединен с первыми входами первого сумматора и третьего вычитателя, вторые входы которых подключены соответственно к выходу вычитателя, соединенного с первым входом пятого сумматора и выходом пятого сумматора, второй вход которого подключен к выходу первого сумматора, выход второго вычитателя .соединен с первым входом первой схемы сравнения, второй вход которой соединен с выходом третьего сумматора, вькод второй схемы сравнения соединен со вторым управляющим входом коммутатора, первый, второй и третий информационные входы коммутатора подключены соответственно к выходам третьего вычита- геля, первого сумматора и блока умножения на коэффициент, а также тем, что блок умножения на коэффициент выполнен из двух последовательно соединенных сум маторов, входы описало из которых соединены между собой со сдвигом на два разряда, а другого - на три раэряда. На фиг. 1 приведена блок-схема устройства для вычисления корня квадратного из суммы квадратов; на фиг. 2 - расчетный график зависимости отношения величины, получаемой на выходе устройства к определяемой величине f 1 О от величины lll/lQl. Устройство содержит два подсоединенных к входным шинам элемента вьшелени модуля 1 и 2, выполненных на логических элементах исключающее ИЛИ (звездочксй здесь отмечены шины знакового разряда), сумматор 3 и вычитатель 4, подсоединенные к выходам элементов выделения модуля 1 и 2, элемент вьшелени модуля 5, подсоединенный к выходу вычи тателя 4, вычитатель 6 и сумматс ы 7 8, подсоединенные к выходам сумматсра 3 и элемента вьшеления модуля 5, блок умножения на коэффициент, выполненный в виде последовательно соединенных сум маторов 9 и 1О, подсоединенный к выходу сумматора 8, сумматор 11, подсоединенный к выходам сумматора 12 и вы читателя 6, вычйГгатель 13,, коммутатор 6 44 14 и схемы сравнения 15 и 16. Шины игналов, подаваемых на первые входы сумматоров 8. - 12; вычитателя 13, коммутатора 14 и схем сравнения 15 и 16 скоммутированы со сдвигом, обеспечивающим умножение этих сигналов на коэффиие нты , 2- 2, 2, 2, 2. 2 , 2 . 2 соответственно, выходы элементов. 6 и 7 скоммутированы со сдвигом на один разряд. Устройство работает следующим образом., Входные сигналы I и Q. подаются на входы элементов вьшеления модуля 1 и 2, с выхода которьсх поступают на сумматор 3 и последовательно соединенные вы - читатель 4 и элементы вьшеления модуля 5. Полученные в результате суммы llV+lQt к модуль разности И II- О поступают на входы вычитателя 6, где образуют величину (lH , tOV), сумматора 7, где образуют величину maix(l зЬ(С1|)и системы из последовательно соединенных сумматоров 8 - 1О, r/ie образуют величину с полпроцентной погрешностью равную 5/4тах(|Ц,|аи-3/4т111(1И,С103- V , , которая поступает на третий вход коммутатора 14. На второй и первый входы коммутатора 14 поступают сигналы с выходов сумматора 12 и вычитателя 13, равные соответственно , laO+te minOii.naO М fS/lumaxOlbiaO 3/8 min(ll|, Ш)Коммутатор 14 управляется сигналами с выходов схем сравнения 15 и 16. При условии 5/4 mih(lH,lGH)3/4ma)((lT|,IQl), проверяиу ом схемой сравнения 15, ком- котируется первый вход ко мутатора. При успшии 1/4ма( Г ),Q)mit( ). проверяемой схемой сравнения 16,коммутируется второй вход коммутатора. При нарушении обоих названных условий коммутируется третий вход коммутатора. В результате на выходе коммутатора име®M Hlii2iL Bkrt близкой по величине Vi -f цг Как следует из Фиг. 2, погрешность определен помощью заявляемого устройства не превышает 0,8%, что в 15 раз меньше погрешности известного устройства. Формула изобретения 1. Устройство для вычисления корня квадратного из суммы квадратов, содержащее первый и второй элементы вьшеления модуля, входы которых соешнены со входами устройства, коммутатор, поо соединенный первым управляющим входом к выходу первой схемы сравнения, и пер.« вый сумматор, отличающееся тем, что, с целью повышения точности, в него введены сумматоры, третий элемент выделения модуля, вычитателн, вторая схема сравнения и блок умножения на коэффициент, причем вхо/хы второго сумматора и первснго вычитателя подключены к выходам первого и второго элементов вьшеления модуля, вход третьего элемента вьшеления модуля Соединен с выходом первого вычитателя, выход второго сумматора подключен к первым входам второго вычитателя, третьего и четвертото сумматоров и второй схемы сравнения, вторые входы которых соединены с выходом третьего элемента выделения модуля, выход четвертого сумматора подключен ко входу блока умножения на коэффициент, выход третьего сумматора соединен первыми входами первого сумматора и третьего вьиитателя, вторые входы которых подключены соответственно к выходу второго вычитателя.

соединенного с первым входом пятого сумматора и выходом пятого сумматора, второй вход которого подключен к выходу .первогоcyMM tdpa, выход вторсго вычи- тателя соединен с первым входом nepecrit схемы сравнения, второй вход ко/тарой соединен с выходом третьего сумматора, выход второй схемы сравнения соединен со вторым управляющим входом коммутатора, первый, второй и третий информационные входы коммутатора аодкшочены соответственно к выходам третьего вычитателя, первого сумматора и блока умножения на коэффициент.

Источники информации, принятые во внимание при экспертизе

f1 Л 0.3 p W 0,6 0.7 0,8

UJ.Z

Авторы

Даты

1981-03-15—Публикация

1979-04-02—Подача