динены с первым и вторым входами элемента ИЛИ этого блока и с выходом мультиплексора, первый и второй входы которого соединены соответственно с информационным входом уст-. ройства и с выходом дешифратора, группа входов которого соединена с группой выходов параллельного накапливающего сумматора блока управления выборкой команд, выход первого элемента ИЛИ которого соединен с первым входом третьего элемента ИЛИ этого блока и с входом запуска блока регистров команд, а в блоке управлейия выборкой команд выходы первого и второго мультиплексоров соединены соответственно с первым входом счетчика и входом параллельного накапливающего сум мтора, разрядный выход которого соединен с вторыми входами счетчика и третьего элемента ИЛИ, выход которого соединен с прямым входом элемента И, выходы сумматора по модулю два и второго элемента ИЛИ соединены с третьей грзтпой информационных входов второго мультиплексора , а в блоке управления вторые входы элементов И группы соединены с соответствующими выходами регистра сдвига, выходы элементов И группы соединены с первыми входами элементов ИЖ группы, вторые входы которых соединены с выходом элемента ИЛИ и с соответствующим установочным входом регистра сдвига, а в блоке хранения команд перехода выходы регистра сдви га соединены с вторыми входами соответствующих элементов И первой

1

группы, выходы которых соединены с первыми управляющими входами регистров первой и второй групп, вторье управляющие входы последних соединены с выводами соответствующих элементов И второй группы и с соответствующими входами элемента ИЛИ, выходы регистров первой группы соединены с вторьми входами соответствующих сумматоров по модулю два два группы, выходы которых соединены с входами соответствующих элементов И второй группы, выход каждого регистра второй грзттпы соединен с соответствующими входами всех элементов ИЛИ группы, выход элемента. НЕ соединен с вторыми управляющими входами всех регистров первой группы, выход элемента задержки соединен с входом регистра сдвига.

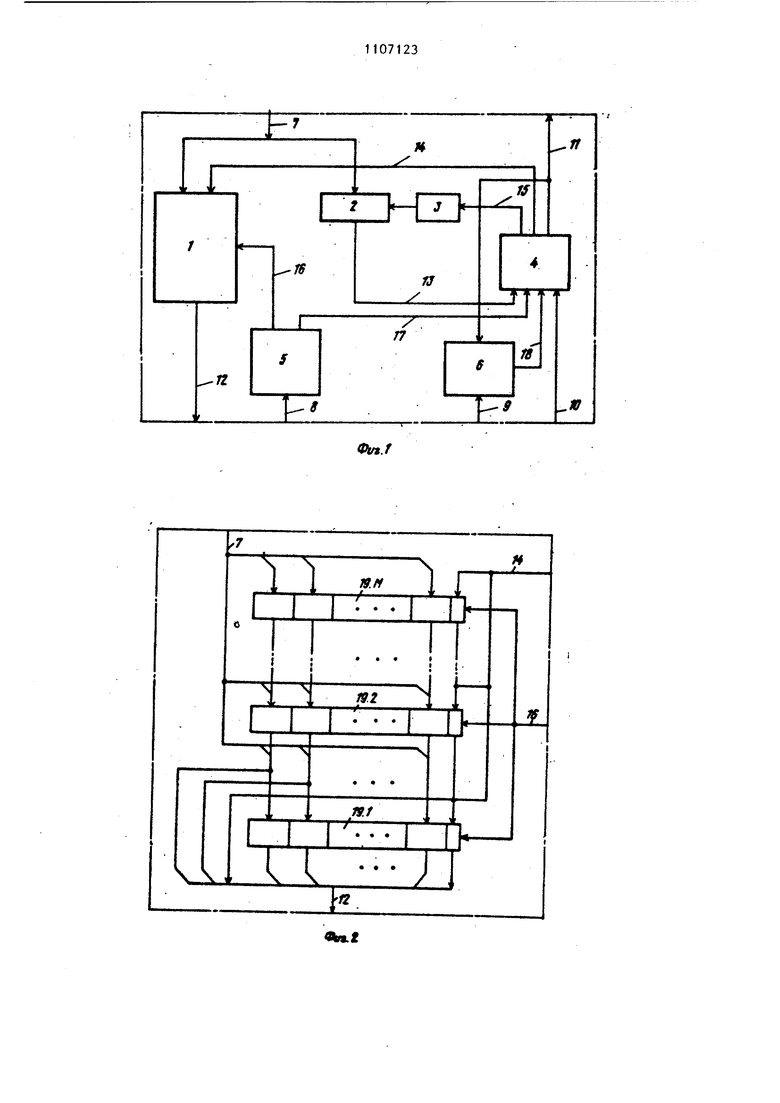

2. Устройство по П.1, о т л ичающееся тем, что блок регистров команд содержит группу регистров, информационные входы которых соединены с информационным входом блока и с первыми выходами предыдущих регистров группы, а первый управляющий вход каадого из регистров группы соединен с управляющим входом блока и с вторым выходом предьиущего регистра группы, вход запуска блока соединен с вторыми управляющими входами регистров группы, а выход блока соединен с выходами первого регистра группы, выходами первых тридцати двух разрядов и вторым разрядным выходом второго регистра группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

1. УСТРОЙСТВО ПРЕДВАРИТЕЛЬНОЙ ВЫБОРР КОМАНД, содержащее блок регистров команд, блок управления выборкой команд и блок управления, причем информационный вход устройства соединен с информационным входом блока регистров команд, выход которого является информационным выходом устройства, первый выход блока управления соединен с управляющим входом блока регистров команд, первый выход блока управления выборкой комавд является адресным выходом устройства, отличающееся тем, что, с целью повьппения производительности, в него введены мультиплексор, дешифратор и блок хранения команд перехода, содержащий регистр сдвига, элемент задержки,элемент НЕ, элемент Ш1И, две группы элементов И, группу сумматоров по модулю два, две групг : регистров,группу элементов ИЛИ, а блок управления выборкой команд содержит элемент И, три элемента ИЛИ, сумматор по модулю два, параллельный накаш1иваю1ций сумматор, два мультиплексора и счетчик, а блок управления содержит группу элементов ИЛИ, группу элементов И, элемент ИЛИ и регистр сдвига, -vpjj.j. ййддМ1 |У : А чем первые входы сумматоров по модулю два группы блока хранения команд перехода соединены с выходами счетчика, параллельного накапливающего сумматора, элемента И и первым выходом блока управления выборкой команд, входы адреса перехода устройства соединены с первьв и входами элементов И первой группы, с входами элемента НЕ и элемента задержки, с информационными входами регистров первой и второй групп блока хранения команд перехода, выход элемента ИЛИ и выходы элемен- . тов ИЛИ группы которого соединены g с первыми группами информационных входов первого и второго мультиплексоров, с первыми управляющими входами первого и второго мультиплексоров и с первым входом первого элемента ИЛИ блока управления выборкой § Команд, вторые группы информационных входов первого и второго мультиплексоров которого соединены с группой входов адреса команд устройства, вторым входом первого элемента ИЛИ, с вторыми и третьими управляющими входами первого и второго мультиплекЮ свров блока управления выборкой коСО манд, инверсный вход элемента И соединен с разрядным выходом регистра сдвига блока управления, выходы элементов ИЛИ группы которого соединены с первым выходом этого блока, первый и второй входы элемента ИЛИ, установочные входы регистра сдвига и первые входы элементов И группы которого соединены с установочным входом устройства, первый и второй входы сумматора по модулю два блока управления выборкой команд сое

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров вычислительны систем.

Известно устройство, осуществляющее предварительную выборку команд из оперативной памяти, содержащее четьч е буферных регистра по 64 разряда, узел селекции,-регистр кода команды, инкрементор, адресный сумматор, регистр слова состояния програмны и два регистра адреса оперативной памяти О.

Недостатком устройства является то, что при изменении последовательного порядка вьшолнения команд предварительная выборка оказывается выполненной неверно, что ведет к простоям процессора в ожидании окончания выборки требуемой команды и, следовательно, сниженшо производительности.

Наиболее близким к изобретению по технической сущности является устройство для буферизации команд, содержащее буфер команд, состоящий

из nejaBoro, второго и третьего буферных регистров, блок управления буфером команд, состоящий из блока анализа заполнения буфера и блока управления продвижением, блок управленяя выборкой, состояний из регистра адреса, блока наращивания адресов команд и блока управлегтя выборкой команд, причем первый выход блока управления выборкой соединен с первым выходом устройства, первый вход которого соединен с первым входом буфера команд, второй вход которого соединен с вторьм выходом блока управления выборкой, третий выход которого соединен с шестьм входом блока управления буфером, команд, первый выход которого соединен с третьим входом буфера команд, первый, второй, третий и четвертый выходы которого соединены соответственно с треты1м, четвертым, пятым и шесТЕМ выходами устройства, второй вход которого соединен с третьим входом блока управления выборкой и первым входом блока управления буфером команд, второй, трети и четвертый входы которого соединен соответственно с пятым, шестым и седьмым вьрсодами буфера команд, пятый вход соединен с вторым выходом блока управления выборкой, второй вход которого соединен с вторым выходом блока управления буфером ксманд, а первый вход и четвертый выход соединены соответственно с третьим входом и вторым выходом устройства 2.

Однако известное устройство осуществляет предварительную выборку только с последовательным наращиванием адресов команд, вследствие чего при нарушениях последовательного порядка выполнения команд возникают простои процессора, а следовательно, снижается его производительность.

Такое устройство реализует алгоритм частичной предварительной выборки, поскольку при наличии двух последовательных команд с длиной кода 6 байтов (формат) предварительная выборка следующих кома1Щ блокируется, и, кроме того, предварительная выборка производится только во время выполнения последней полностью выбранной в буфер команды, что при времени ее выполнения.

меньшем времени выборки из оперативной памяти, приводит к дополни- . тельным простоям процессора. Цепь изобретения - повыпение

производительности устройства.

Поставленная цель достигается тем, что в устройство, содержащее блок регистров команд, блок управления выборкой команд и блок управления, причем информационный вход устройства соединен с информационньм входом блока регистров команд, выход которого является информационным выходом устройства, первый выход

блока управления соединен с управляющим входом блока регистров команд первый выход блока управления выборкой команд является адресным выходом устройства, введены мультиплексор, дешифратор и блок хранения

команд перехода, содержап91й регистр сдвига, элемент задержки, элемент НЕ, элемент Ш1И, две группы элементов И, группу сумматоров по

модулю два, две группы регистров, . группу элементов ИЛИ, а блок управления выборкой команд содержит элемент И, три элемента ИЛИ, сумматор по модулю два, параллельный накашгавакаций сумматор, два мультиплексора и счетчик, а блок управления содерягит группу элементов ИЛИ, группу элементов И, элемент ИЛИ и регистр сдвига, причем первые входы сумматоров по модулю два группы бпока хранения команд перехода соединены с выходами счетчика, параллельного накапливающего сумматора, элемента И и первьм выходом блока управления выборкой команд, входы адреса перехода устройства соединены с первыми входами элементов И первой группы, с входами элемента НЕ и элемента задержки,с информационными вхо

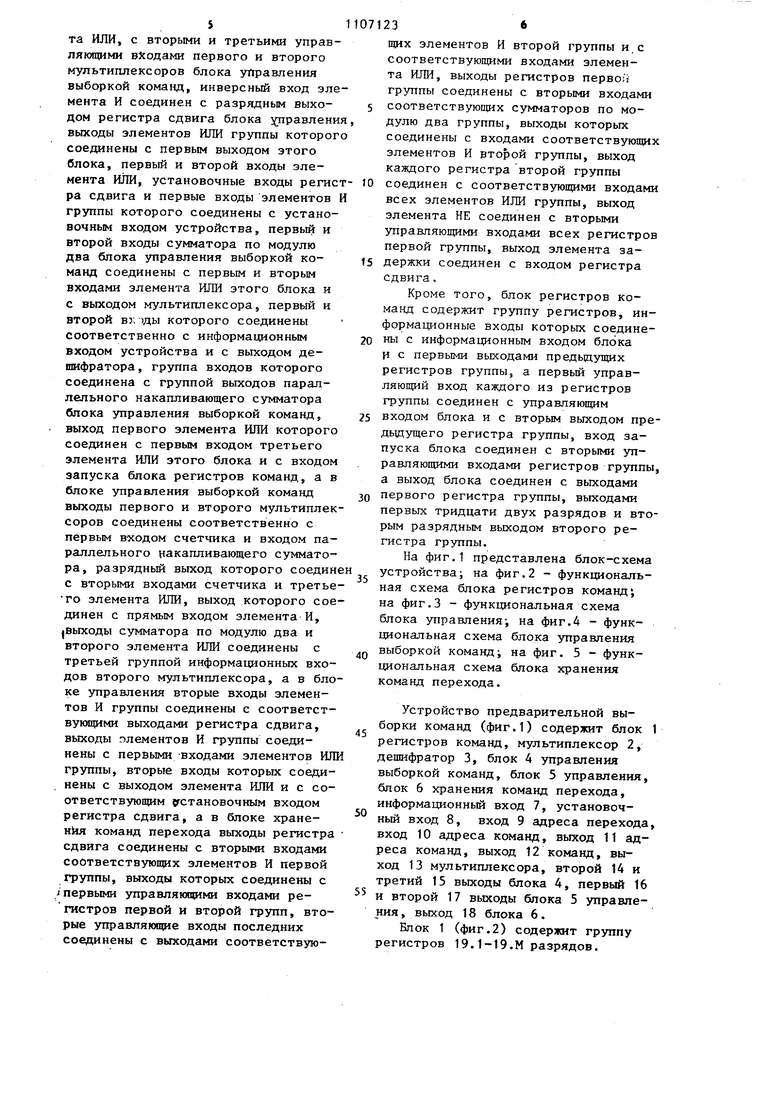

дами регистров первой и второй

fj)ynn блока хранения команд перехода, выход элемента ИЛИ и выходы элементов ИЛИ группы которого соединены с первьа и группами информацион входов первого и второго мультиплексоров, с первыьш управляющими входами первого и второго мультиплексоров и с первым входом первого элемента ИЛИ блока управления выборкой команд, вторые группы информационных входов первого и второго мультиплексоров которого соединены с группой входов адреса команд устройства, вторым входом первого элеменiта ИЛИ, с вторыми и третьими управлякяцими входами первого и второго мультиплексоров блока управления выборкой команд, инверсный вход эле мента И соединен с разрядным выходом регистра сдвига блока хпрэвлени выходы элементов ИЛИ группы которог соединены с первым выходом этого блока, первый и второй входы элемента ИЛИ, установочные входы регис ра сдвига и первые входы элементов группы которого соединены с установочным входом устройства, первый и второй входы сумматора по модулю два блока управления выборкой команд соединены с первым и вторым входами элемента ИЛИ этого блока и с выходом мультиплексора, первый и второй вз; )ды которого соединены соответственно с информационным входом устройства и с выходом дешифратора , группа входов которого соединена с группой выходов параллельного накапливающего сумматора блока управления выборкой команд, выход первого элемента ИЛИ которого соединен с первым входом третьего элемента ИЛИ этого блока и с входом запуска блока регистров команд, а в блоке управления выборкой команд выходы первого и второго мультиплек соров соединены соответственно с первым входом счетчика и входом параллельного накапливающего сумматора, разрядный выход которого соедин с вторыми входами счетчика и третье то элемента ИЛИ, выход которого сое динен с прямым входом элемента И, выходы сумматора по модулю два и второго элемента ИЛИ соединены с третьей группой информационных входов второго мультиплексора, а в бло ке управления вторые входы элементов И группы соединены с соответствукмдими выходами регистра сдвига, выходы элементов И группы соединены с первыми входами элементов ИЖ группы, вторые входы которых соеди нены с выходом элемента ИЛИ и с соответствующим установочным входом регистра сдвига, а в блоке хранения команд перехода выходы регистра сдвига соединены с вторыми входами соответствующих элементов И первой группы, выходы которых соединены с /первыми управляющими входами регистров первой и второй групп, вто рые управляющие входы последних соединены с выходами соответствую236щих элементов И второй группы и с соответствующими входами элемента ИЛИ, выходы регистров первой группы соединены с вторыми входами соответствующих сумматоров по модулю два группы, выходы которых соединены с входами соответствующих элементов И второй группы, выход каждого регистра второй группы соединен с соответствующими входами всех элементов ИЛИ группы, выход элемента НЕ соединен с вторыми управляющими входами всех регистров первой группы, выход элемента задержки соединен с входом регистра сдвига, Кроме того, блок регистров команд содержит группу регистров, информационные входы которых соединены с информационным входом блока И с первыми выходами предьдущих регистров группы, а первый управляющий вход каждого из регистров группы соединен с управляющим входом блока и с вторым выходом предыдущего регистра группы, вход запуска блока соединен с вторыми управляющими входами регистров группы, а выход блока соединен с выходами первого регистра группы, выходами первых тридцати двух разрядов и вторым разрядным выходом второго регистра группы. На фиг,1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока регистров команд; на фиг.З - функциональная схема блока управленияi на фиг.4 - функциональная схема блока управления выборкой команд; на фиг. 5 - функциональная схема блока хранения команд перехода. Устройство предварительной выборки команд (фиг.1) содержит блок 1 регистров команд, мультиплексор 2, дешифратор 3, блок 4 управления выборкой команд, блок 5 управления, блок 6 хранения команд перехода, информационный вход 7, установочный вход 8, вход 9 адреса перехода, вход 10 адреса команд, выход 11 адреса команд, выход 12 команд, выход 13 мультиплексора, второй 14 и третий 15 выходы блока 4, первый 16 и второй 17 выходы блока 5 управления , выход 18 блока 6. Влок 1 (фиг.2) содержит группу регистров 19.1-19.М разрядов. 7 Блок 5 управления (фиг.З) содержит группу элементов ИЛИ 20, группу элементов И 21, регистр 22 сдви га и элемент ИЛИ 23. Блок 4 управления выборкой команд (фиг.4) содержит элемент И 24 третий элемент ИЛИ 25, асинхронный счетчик 26, параллельный накапливаю щий сумматор 27, первый элемент ИЛИ 28, первый мультиплексор 29, второ мультиплексор 30, сумматор 31 по модулю два и второй элемент ИЛИ 32 Блок 6 (фиг.З) содержит кольцевой регистр 33 сдвига, элемент 34 задержки, элемент НЕ 35, первую гр пу элементов И 36.1-36.L, первую группу элементов И 37.1-37.L, груп пу сумматоров 38.1-38.L по модулю два,группу регистров 39.1-39,L, вторую группу регистров 40.1-40.L по К разрядов каждый, элемент ИЛИ группу элементов ИЛИ 42.1-42.К. Клок 1 (фиг.2) предназначен для приема, хранения и передачи на вьпс устройства предварительно выбранны из оперативной памяти команд. Блок 5 управления (фиг.З) предназначен для управления приемом и продвижением информации в блоке Блок 4 управления выборкой кома (фиг.4) предназначен для формирования адреса оперативной памяти и сигнала запуска выборки команд по этому ащресу. Мультиплексор 2 предназначен дл вьщеления из входного потока отдел ных команд. о Дишифратор 3 предназначен для управления мультиплексором 2. Блок 6 (фиг.5) предназначен для хранения адресов вьтолняющихся команд перехода, нарушавших последовательный порядок вьшолнения коман и адресов, на которые они передава ли управление. Устройство работает следующим образом. В начале работы устройства сигналом с входа 8 устройства устанав ливают в 1 все разряды реверсивного регистра 22 сдвига блока 5 управления (фиг.З). Затем после ус тановки на выходе 11 устройства ад реса памяти, поступающего на четвертый вход 10 блока 4 управления выборкой команд вместе с управления, запускается выборка командной информации сигналом, поступающим на первый выход 11 бло 38 ка управления выборкой с элемента И 24 (фиг.4), при этом сигнал на втором входе 17 блока 4 управления выборкой команд отсутствует, так как в блоке 1 есть свободные регистры (буфер пуст). По окончании выборки командная информация поступает в блок 1 и в мультиплексор 2. Если информация, поступающая в блок 1, выбрана из памяти по адресу, поступившему в блок 4 управления выборкой команд с третьего 18 или четвертого 10 входов, то вместе с командной информацией в младший разряд соответствующего регистра 19 группы блока 1 заносится 1, которая является признаком того, что адрес находящейся в этом регистре командной информации не является .последовательным продолжением адреса информации, выбранной из оперативной памяти перед этим. По окончании выборки с помощью дешифратора 3 по значениям младших разрядов адреса мультиплексор 2 пропускает на свой выход 13 стар- . шие разряды кода операции, определяющие длину команды, адрес которой установлен на первом выходе 11 блока 4 управления выборкой команд. Этот адрес подается также и на первый вход блока 6 (фиг.З). Если этот адрес есть в одном из региспров 39 группы, то на выход 18 поступает сигнал совпадения с выхода элемента ИЛИ 41 и адрес команды, которая подлеямт выборке и помещению в следующий регистр блока 1, с выходов соответствующего регистра 40 груйпы. По сигналу совпадения, поступающему на третий вход 18 блока 4 управления выборкой команд, первый 29 и второй 30 мультиплексоры (фиг.4) передают адрес комавды на асинхронный счетчик 26 и параллельный накапливающий сумматор 27 вместе с сигналом начальной установки, формируется сигнал запуска выборки и записывается 1 в младший разряд соответствующего регистра 19 группы блока 1. Если в блоке 6 совпадения нет, то на основании значений старших разрядов кода операции, поступаю1Щ х на первый вход 13 блока 4 управления выборкой команд, сумматор 31 по модулю два и элемент ИЛИ 32 формируют код длины команды, который через второй мультиплексор 30 поступает на вход параллельного накапливающего сумматора 27, складьшается с установленным там адресом, образу адрес следующей командьь Если при этом в сумматоре 27 возникает сигнал переноса, который подается на вход асинхронного счетчика 26 и фор мирует адрес слова памяти, подлежащего выборке, то формируется сигнал запуска выборки из оперативной памя ти. Если переноса нет, новый адрес поступает на входы дешифратора 3 (младшие разряды) и блока 6, и процесс повторяется. Если по окончании очередной выборки из оперативной памяти блок 1 окажется полностью заполненным, блок 5 управления выдает сигнал (с инверсного выхода последнего разряд реверсивного регистра сдвига) на второй выход 17, который, поступая на второй вход блока 4 управления выборкой команд,блокирует вьщачу сигнала запуска выборки на первый выход 11 блока 4 до тех пор, пока не освободится хотя бы один регистр 19 группы в блоке 1. Параллельно с описанным процессом выполняются команды в арифметико-логическом устройстве (йе показано) процессора, поступающие с выхода 12 блока 1. Если в процессе обработки выполняется команда перехода и если она нарушает последовательный порядок обработки команд, то соответствующий сигнал, ее адрес и адрес, на который она передает уп равление, вьщаются на второй вход 9 блока 6 и записываются в соответствукицие регистры 39 и 40 групп бло ка 6 (на время записи) сигналом, поступающим на четвертый вход блока 4 управления выборкой команд, блоки руются первый и второй мультиплексо ры (фиг.4), а если, кроме того, в младшем разряде второго регистра 19.2 группы блока 1 установлен О то адрес перехода передается на четвертый вход 10 блока управления 2310 выборкой и запускается выборка нового слова памяти и вьдается сигналi на вход 8 блока 5 управления, который поступает на установочный четвертый вход реверсивного регистра 22 сдвига (фиг.З) и устанавливает все разряды регистра 22 в 1, если же в младшем разряде второго регистра 19.2 группы блока 1 установлена 1, то, вьздается сигнал на вход 8 блока 5 управления, по которому производится сдвиг информации в блоке t на один регистр вниз. Если выполненная команда перехода не нарушает последовательности и если в мпадшем разряде второго регистра 19.2 группы содержится 1, то на вход 8 блока 5 управления постзтает сигнал, по которому в реверсивном регистре сдвига устанавливаются в 1 все разряды, кроме первого. Если команд перехода, нарушающих последовательньй порядок выполнения команд, в пределах первого регистра 19.1 группы блока 1 не встретилось, то по окончании обработки всех команд, начало которых находится в первом регистре 19.1 группы, поступает сигнал на вход 8 блока 5 управления, по которому производится сдвиг информации в блоке 1 на один регистр вниз. После каждой выборки по сигналу Конец выборки, которьй подается на вход 8 блока 5 управления, вьщаются сигналы приема на первый выход 16 и происходит сдвиг информации в реверсивном регистре сдвига на один разряд вверх. Таким образом, при заданных параметрах процессора и характеристиках нагрузки использование предлагаемого устройства позволяет повысить производительность процессора . на 20-22% при незначительном увеличении объема оборудования 4

Г6

ff

Н

fj

иЛ7

9

0vn.J

iL

26

29

Ь...1

1в

27

J&

31

J2

JT

-и

Ф1П,4

tP

Л/ JK/ Л/

4ai

mm TfT

IT

4вг

4/ I I 42/1 412

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент СЩ № 1081986, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для буферизации команд | 1976 |

|

SU610109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-11—Подача