Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЭВМ и вычислительных системах с микропрограммным управлением.

Целью изобретения является расширение области применения устройства за счет обеспечения работы устройства в режиме прерывания по приорите- ту.

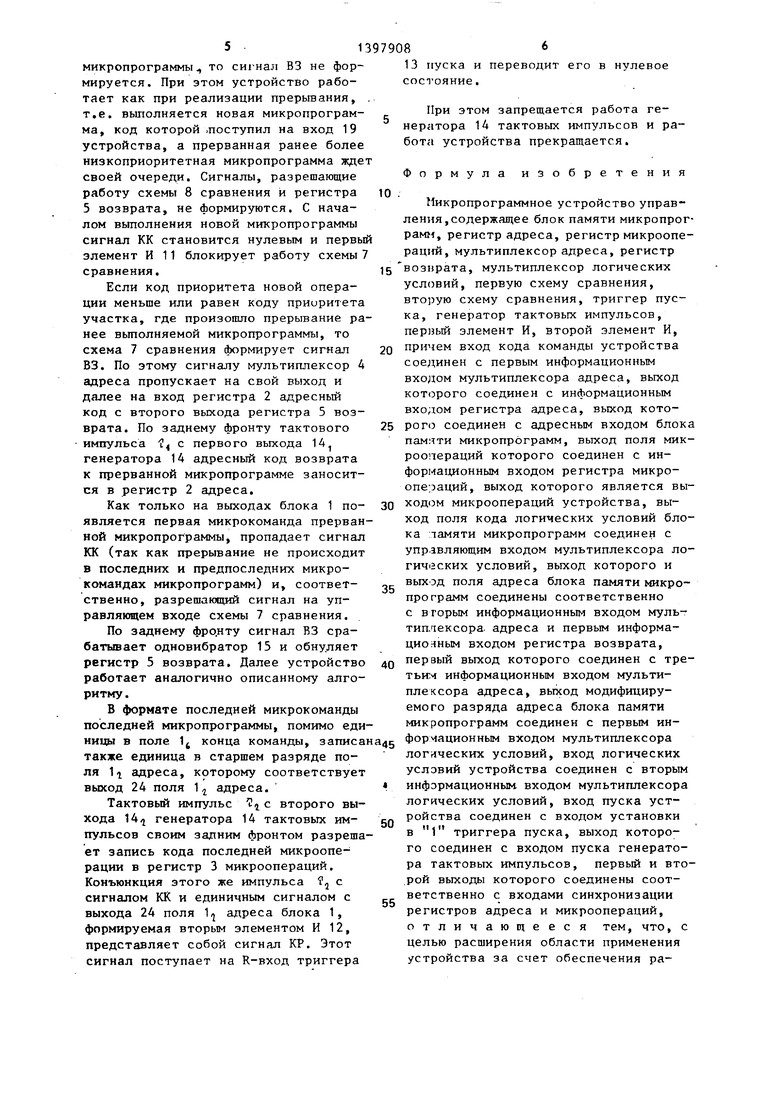

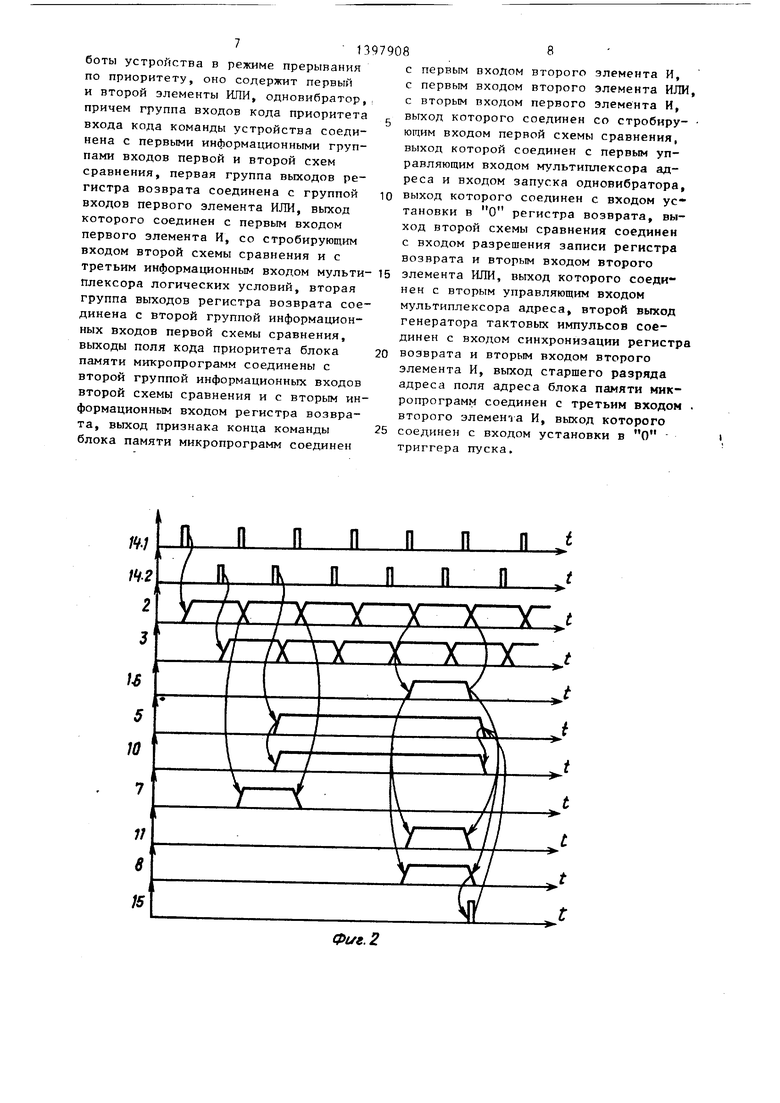

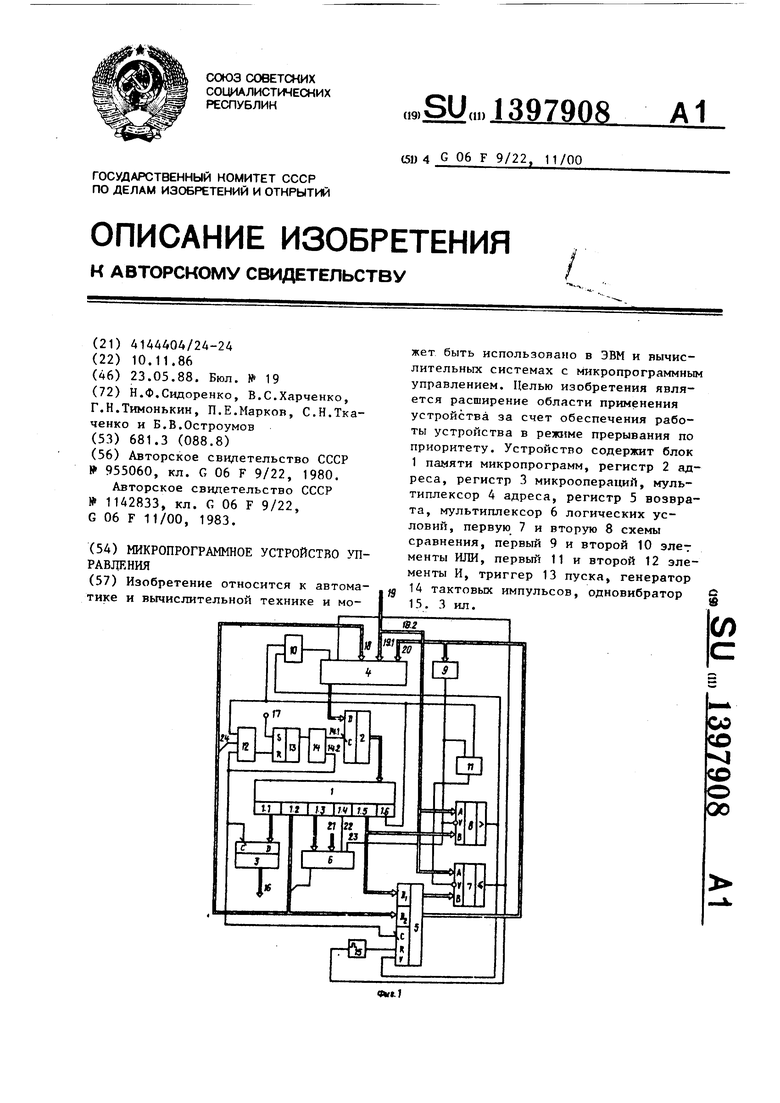

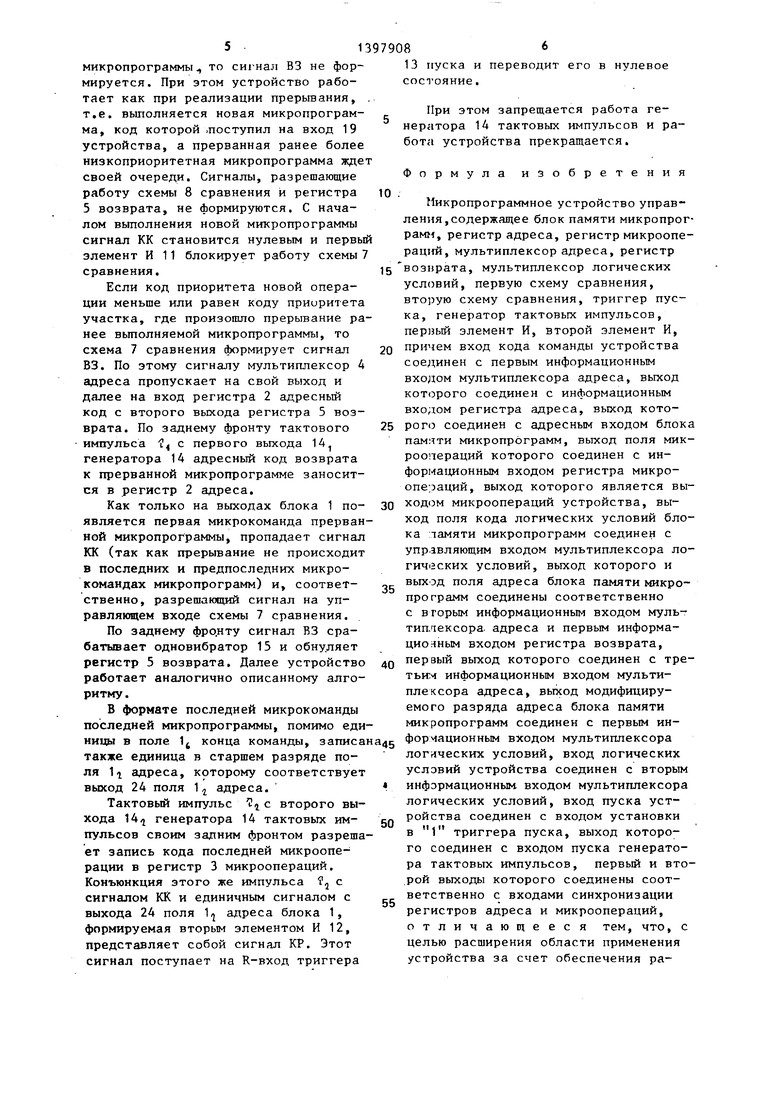

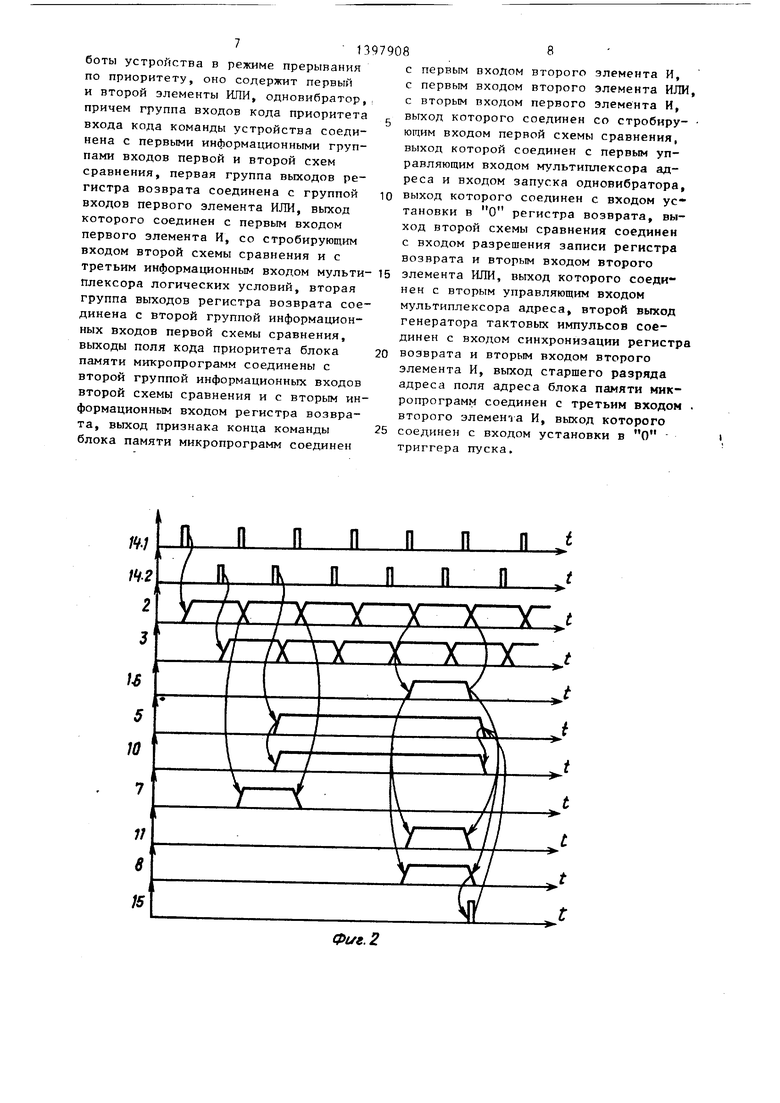

На фиг.1 приведена функциональная схема микропрограммного устройства управления; на фиг.2 - временная диаграмма работы устройства в ре жиме прерывания; на фиг.З - алгоритм функционирования устройства.

Микропрограммное устройство управления содержит блок 1 памяти микропрограмм, поле 1, микроопераций блока памяти микропрограмм, поле 1, адреса блока памяти микропрограмм, поле Ij кода логических условий блока памяти микропрограмм, выход 1 младшего разряда адреса блока памяти микропрограмм, поле 1 кода приоритета блока памяти микропрограмм, поле 1 конца команды блока памяти микропрограмм, регистр 2 адреса, регистр 3 микроопераций, мультиплексор 4 адреса, регистр 5 возврата, мультиплексор 6 логических условий, первую 7 и вторую 8 схемы сравнения, первьй 9 и второй 10 элементы ИЛИ, первый 11 и второй 12 элементы И, триггер 13 пуска, генератор 14 тактовых импульсов, первый 14, и второй 14 выходы генератора 14 тактовых импульсов, одновибратор 15-, выхо 16 микроопераций устройства, вход 17 пуска устройства, второй информационный вход 18 мультиплексора, входы адреса 19 и приоритета 19 входа 19 кода операций устройства, третий информационный вход 20 мультиплексора 4 адреса, вход 21 кода логических условий устройства, первьш 22 и третий 23 информационные входы мультиплексора 6 логических условий, выход 24 старшего разряда поля Ц адреса блока памяти микропрограмм.

Устройство работает следующим образом.

Смена кодов операции на входе 19 устройства происходит между импуль

сами

и

Ч

осуществляется с учетом сигналов КК (поле 1 блока 1) и ПР (выход схемы 8 сравнения) (выходы генератора 14 схемы 8 сравнения и поQ

5

0 5

0

5

ля 1 блока 1 как внешние выходы устройства условно не показаны) ..

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии. В поле 1 нулевой ячейки блока 1 записана 1.

Единичный сигнал с выхода этого поля через элемент ИЛИ 10 поступает на первый управляющий вход мультиплексора 4 адреса, на его втором управляющем входе единичный сигнал отсутствует, поэтому мультиплексор 4 адреса, согласно алгоритму своей работы, пропускает на информационный вход регистра 2 адреса адресный код новой операции с входа 19, адресного кода входа 19 кода операций устройства.

В режиме работы без реализации прерываний по сигналу Пуск с входа 17 устройства триггер 13 пуска устанавливается в единичное состояние и включает генератор 14. По заднему фронт/ первого тактового импульса Г, с вьгхэда 14, генератора 14 в регистр 2 адрэса заносится присутствующий на его информационном входе адрес первой микрокоманды первой микропрограммы. Этот адрес поступает затем на вход блока 1. В результате на выходе его поля 1, появляется код микроопераций, на выводе поля 1 - адрес очередной микрокоманды, на выходе поля Ц (если это макрокоманда ветвления) - код проверяемого логического условия, на поля 1 - младший разряд адреса следующей микрокоманды (если эта микрокоманда линейная), на вы

ходе лоля 1 код приоритета следующей микрокоманды. Сигнал с выхода поля 1 блока 1 во всех микрокомандах микропрограммы, кроме последней, равен нулю.

По заднему фронту тактового импульса t с выхода 14 генератора 14 тактовых импульсов код операций записывается в регистр 3 микроопераций и затем поступает на выход микроопераций у::тройства.

Если считанная микрокоманда содержи г в поле логических условий нулевэй код, то мультиплексор 6 логических условий пропускает на свой выход значение сигнала с выхода поля 1 младшего разряда адреса блока 1 памяти.

Если считана микрокоманда ветвления, го по коду логических условий

из поля 1j блока 1 мультиплексор 6 логических условий пропускает на свой выход в качестве значения младшего разряда адреса значение проверяемого логического условия. Таким образом, осуществляется модификация младшего разряда адреса.

Так как на выходе поля 1 конца

команды сигнал уже нулевой, то мультиплексор 4 адреса пропускает на сво выход и далее на информационный вход регистра 2 адреса со своего первого информационного входа адрес очередно микрокоманды с выходов поля 1 блока 1 и мультиплексора 6 логических условий .

На инверсном управляющем входе схемы 8 сравнения присутствует нулевой разрешающий сигнал с выхода элемента ИЛИ 9, так как регистр 5 возврата в нулевом состоянии. На управляющем входе схемы 7 сравнения разрешающий сигнал отсутствует.

В поле 1g конца команды блока 1 фор- мата последней микрокоманды микропрограммы записана единица.Сигнал КК,поступая через элемент ИЛИ 10 на первый управляющий вход, управляет работой

код HOBOPI поступившей операции. Сигнал ПР поступает также на управляющий вход регистра 5 возврата, разрешая запись в него адресного и приоритетного кодов следующей микрокоманды прерываемой микропрограммы с соответствующих выходов блока 1 . Запись происходит по заднему фронту такто

14

I

вого импульса f с второго выхода генератора 14 тактовых импульсов. Только после этого новый тактовый импульс , с первого выхода 14, генератора 14 своим задним фронтом разрешает запись в регистр 2 адреса адресного кода попой микропрограммы. С записью информации в регистр 5 возврата элемент ИЛИ 9 формирует единичный сигнал РВ. Этот сигнал, поступая на инверсный управляющий вход схемы 8 сравнения, блокирует ее работу, запрещая таким образом вторичное прерывание, пока не выполнено первое. Сигнал РВ поступает также на вход 23 мультиплексора 6 логических условий. Далее устройство выполняет микропрограмму прерывания аналогично прежней прерванной микропрограмме. Микропрограмма прерывания может использовать

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

Изобретение относится к автоматике и вычислительно технике и может быть использовано в ЭВМ и вычислительных системах с микропрограммным управлением. Пелью изобретения является расширение области применения устройства за счет обеспечения работы устройства в режиме прерывания по приоритету. Устройство содержит блок 1 памяти микропрограмм, регистр 2 адреса, регистр 3 микроопераций, мультиплексор 4 адреса, регистр 5 возврата, мультиплексор 6 логических условий, первую 7 и вторую 8 схемы сравнения, первый 9 и второй 10 элет менты ИЛИ, первьп 11 и второй 12 элементы И, триггер 13 пуска, генератор 14 тактовых импульсов, одновибратор 15. 3 ил. с S (Л со со о о 00

мультиплексора 4, который при поступ- 30 рабочие микропрограммы, состоящие из

лении этого сигнала пропускает на свой выход и далее на вход регистра 2 адреса адресный код новой операции.

Далее цикл работы устройства в режиме без прерываний повторяется. В режиме прерывания устройство работает только тогда, когда новая операция, адресный код которой поступает на адресный вход 19, входа 19 кода операций устрор1ства, имеет более высокий приоритет, чем следующая за текущей микрокоманда выполняемой микропрограммы.

Так как на инверсном управляющем входе схемы 8 сравнения имеется разрешающий нулевой сигнал с поступлением на вход А схемы 8 сравнения кода приоритета более высокого, чем код приоритета следующей микрокоманды текущей микропрограммы, поступающий на вход схемы В, на выходе схемы 8 сравнения появляется единичный сигнал ПР. Он через элемент ИЛИ 10 поступает на первый управляющий вход мультиплексора 4 адреса (на втором управляющем входе единичный сигнал отсутствует) .

Мультиплексор 4 адреса пропускает на вход регистра 2 адреса адресный

5

0

микрокоманд, более низко приоритетных микропрограмм. При этом в поле 1j логических условий формата последних микрокоманд таких микропрограмм должен быть записан нулевой код. По этому коду мультиплексор 6 логических условий пропускает на свой выход в качестве значения младшего разряда адреса следующей микрокоманды сиг нал ВЗ.

Если сигнал единичный (при вьтол- нении микропрограммы прерьгоания), то адресация происходит к микрокоманде возврата, к микропрограмме прерывания. Если сигнал ВЗ нулевой, т.е. выполняется не микропрограмма прерывания, то адресация происходит к следующей микрокоманде текущей микропрограммы.

В поле конца команды последней микрокоманды записана единица. Конъюнкция этого сигнала КК с единичным сигналом РВ, формируемая первым элементом И 11, разрешает работу схемы g сравнения. Если код приоритета на входе А схемы 7 вновь поступившей на вход 19 кода операций устройства микропрограммы больше кода приоритета на входе В схемы 7 прерванного участка

5

0

микропрограммы то си1 нал ВЗ не формируется. При этом устройство работает как при реализации прерывания, т.е. выполняется новая микропрограм- ма, код которой поступил на вход 19 устройства, а прерванная ранее более низкоприоритетная микропрограмма жде своей очереди. Сигналы, разрешающие работу схемы 8 сравнения и регистра 5 возврата, не формируются, С началом выполнения новой микропрограммы сигнал КК становится нулевым и первы элемент И 11 блокирует работу схемы 7 сравнения,

Если код приоритета новой операции меньше или равен коду приоритета участка, где произошло прерывание ранее вьтолняемой микропрограммы, то схема 7 сравнения формирует сигнал ВЗ, По этому сигналу мультиплексор А адреса пропускает на свой выход и далее на вход регистра 2 адресный код с второго выхода регистра 5 возврата. По заднему фронту тактового импульса 7 с первого выхода 14 генератора 14 адресный код возврата к прерванной микропрограмме заносится в регистр 2 адреса.

Как только на выходах блока 1 по- является первая микрокоманда прерванной микропрограммы, пропадает сигнал КК (так как прерывание не происходит в последних и предпоследних микрокомандах микропрограмм) и, соответ- ственно, разрешающий сигнал на управляющем входе схемы 7 сравнения.

По заднему фронту сигнал ВЗ срабатывает одновибратор 15 и обнуляет регистр 5 возврата. Далее устройство работает аналогично описанному алгоритму,

В формате последней микрокоманды последией микропрограммы, помимо единицы в поле 1j конца команды, записа также единица в старшем разряде поля Ц адреса, которому соответствует выход 24 поля 1j адреса,

Тактовый импульс второго выхода 14,1 генератора 14 тактовых им- пульсов своим задним фронтом разрешает запись кода последней микрооперации в регистр 3 микроопераций. Конъюнкция этого же импульса Т, с

сигналом КК и единичным сигналом с выхода 24 поля 1,j адреса блока 1, формируемая вторым элементом И 12, представляет собой сигнал КР, Этот сигнал поступает на R-вход триггера

5

0 5

0 5

0

5

Q

5

13 пуска и переводит его в нулевое состояние.

При этом запрещается работа генератора 14 тактовых импульсов и работа устройства прекращается.

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микропрограмм, регистр адреса, регистр микроопераций, мультиплексор адреса, регистр возврата, мультиплексор логических условий, первую схему сравнения, вторую схему сравнения, триггер пуска, генератор тактовых импульсов, элемент И, второй элемент И, причем вход кода команды устройства соединен с первым информационным входом мультиплексора адреса, выход кот(5рого соединен с информационным входом регистра адреса, выход кото- рого соединен с адресным входом блока памяти микропрограмм, выход поля микроопераций которого соединен с информационным входом регистра микроопераций, выход которого является вы- ХОД15М микроопераций устройства, выход поля кода логических условий блока ламяти микропрограмм соединен с управляющим входом мультиплексора логических условий, выход которого и выход ПОЛЯ адреса блока памяти микропрограмм соединены соответственно с вторым информационным входом мультиплексора, адреса и первым информа- циог1ным входом регистра возврата, первый выход которого соединен с тре- тьи;ч информационным входом мультиплексора адреса, выход модифицируемого разряда адреса блока памяти микропрограмм соединен с первым ин- формационньм входом мультиплексора логических условий, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, вход пуска устройства соединен с входом установки в 1 триггера пуска, выход которого соединен с входом пуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхронизации регистров адреса и микроопераций, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения работы устройства в режиме прерывания по приоритету, оно содержит первый и второй элементы ИЛИ, одновибратор, причем группа входов кода приоритета входа кода команды устройства соединена с первыми информационными группами входов первой и второй схем сравнения, первая группа выходов регистра возврата соединена с группой входов первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, со стробирующим входом второй схемы сравнения и с

10

с первым входом второго элемента И, с первым входом второго элемента ИЛ с вторым входом первого элемента И, выход которого соединен со стробиру Ю1ДИМ входом первой схемы сравнения, выход которой соединен с первым управляющим входом мультиплексора адреса и входом запуска однсвибратора выход которого соединен с входом ус тановки в О регистра возврата, вы ход второй схемы сравнения соединен с входом разрешения записи регистра возврата и вторым входом второго

третьим информационным входом мульти- 15 элемента ИЛИ, выход которого соедиПлексора логических условий, вторая группа выходов регистра возврата соединена с второй группой информационных входов первой схемы сравнения, выходы поля кода приоритета блока 20 памяти микропрограмм соединены с второй группой информационных входов второй схемы сравнения и с вторым информационным входом регистра возврата, выход признака конца команды 25 блока памяти микропрограмм соединен

ней с вторым управляющим входом мультиплексора адреса, второй выход генератора тактовых импульсов соединен с входом синхронизации регистр возврата и вторым входом второго элемента И, выход старшего разряда адреса поля адреса блока памяти микропрограмм соединен с третьим входом второго элемента И, выход которого соединен с входом установки в О триггера пуска.

Фиг. 2

с первым входом второго элемента И, с первым входом второго элемента ИЛИ, с вторым входом первого элемента И, выход которого соединен со стробиру- Ю1ДИМ входом первой схемы сравнения, выход которой соединен с первым управляющим входом мультиплексора адреса и входом запуска однсвибратора, выход которого соединен с входом установки в О регистра возврата, выход второй схемы сравнения соединен с входом разрешения записи регистра возврата и вторым входом второго

ней с вторым управляющим входом мультиплексора адреса, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра возврата и вторым входом второго элемента И, выход старшего разряда адреса поля адреса блока памяти микропрограмм соединен с третьим входом второго элемента И, выход которого соединен с входом установки в О триггера пуска.

пп

С

на V а /I о

Поступление лодй oneflQtfuti на ffxoff fS i/CfnpoL cmffc

Запись ff регистр S SosSpama адреса следу foofeu /iff fnefii/щей мп

запись адрвсмоео но постутлвшеео на SxodtA устроист&а pezucmp 2 offpeca

дыпоянение операции преры&а ия с уозмо)ннын использо амиен no9npoi- ijaMM из дриеих. операцгл

Конец

J

-записи 6pezucmp 2 адресного кода из реил ра 5 ffffsffflama, 1ЛУпаноА на регистра 5 оозбрага 6 исходное состояние

Считывание мн иу /73V 1

запись и) ЛОЛ я 2 адреса ЛЗУ1 моаа адреса следующей мн в pftucmp 2 адреса

-J

| Микропрограммное устройство управления | 1980 |

|

SU955060A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-23—Публикация

1986-11-10—Подача