15

Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления ЭВМ, а также для управления каналами ввода-вывода.g

Целью изобретения является повьше- ние быстродействия.

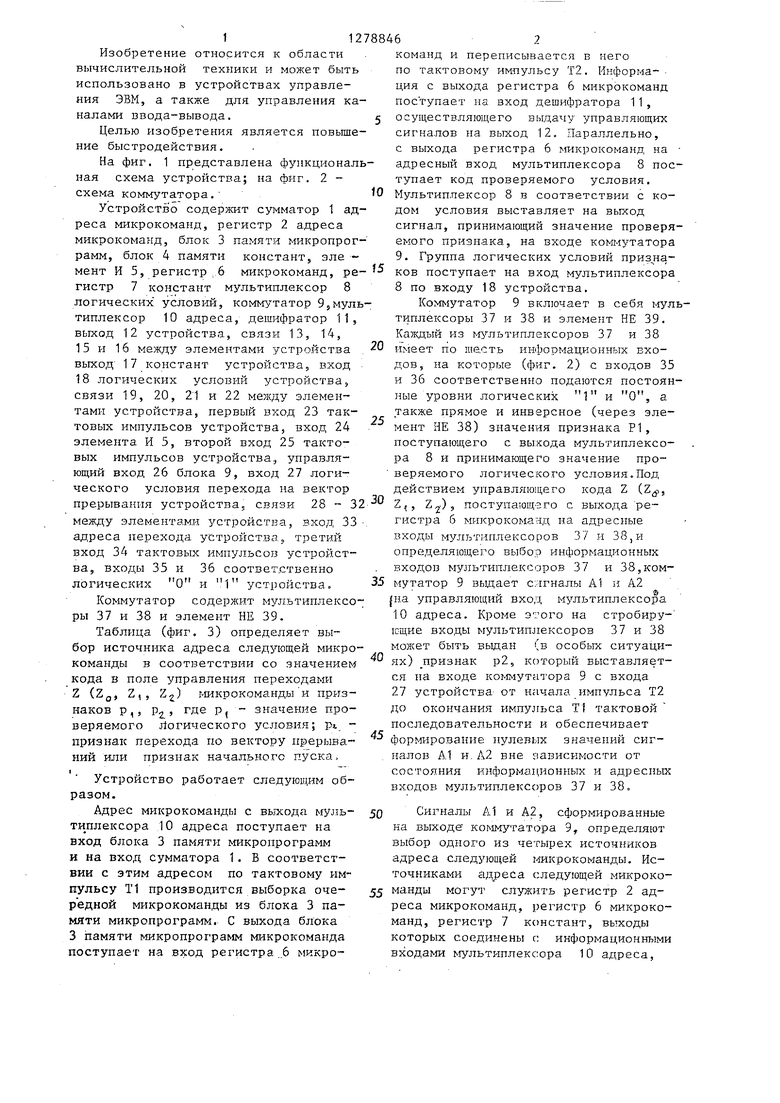

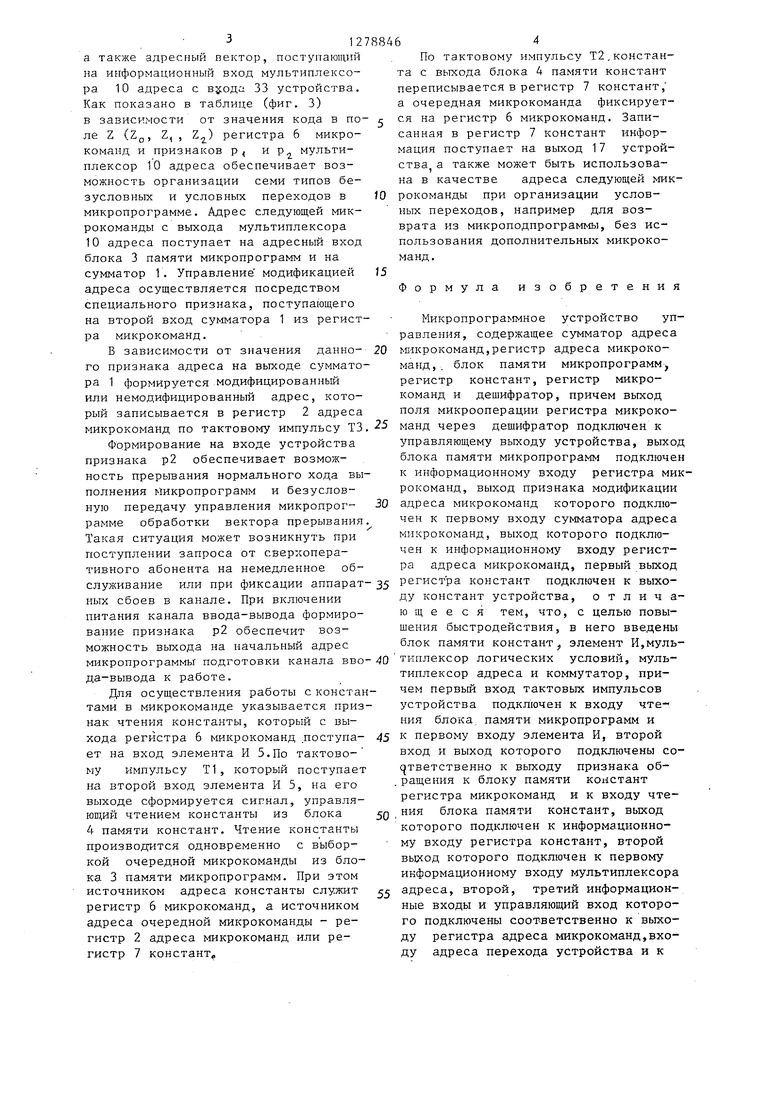

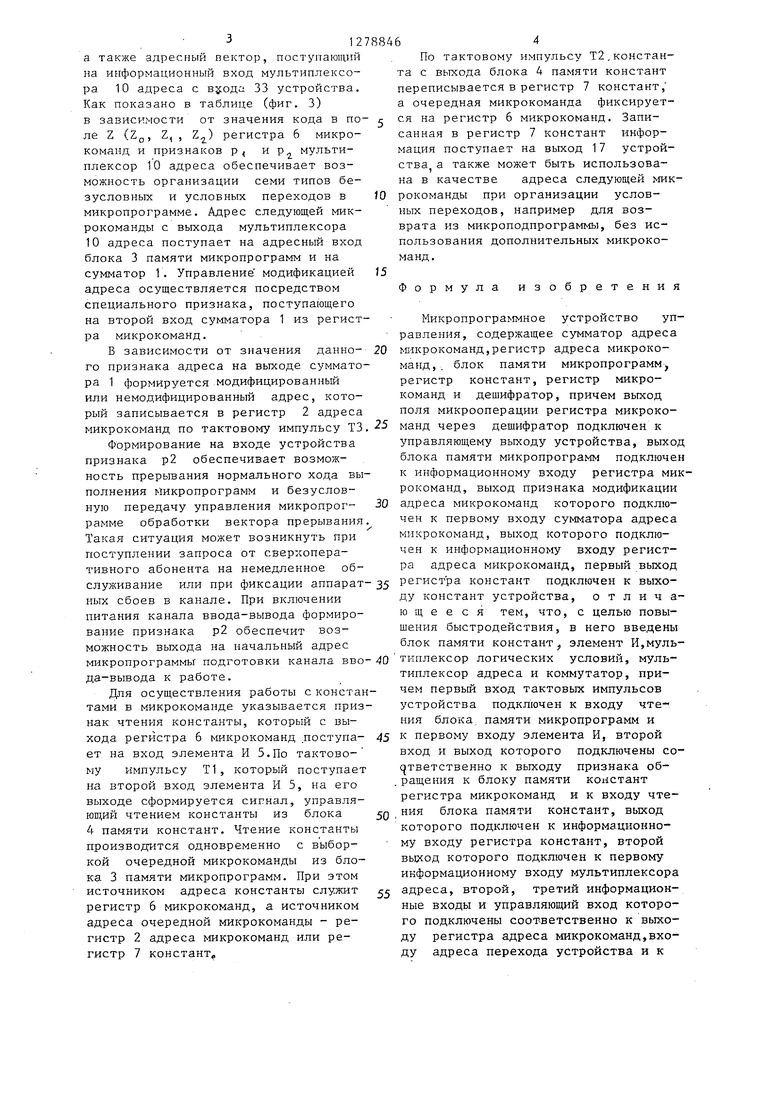

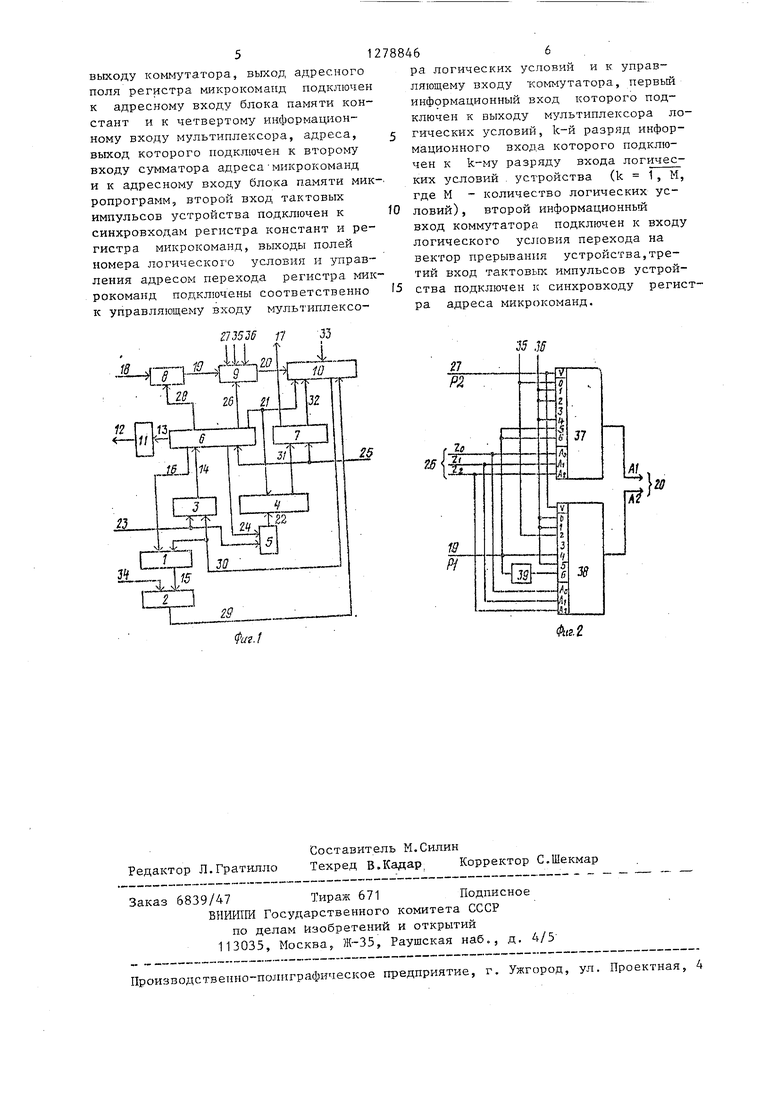

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - схема коммутатора.

Устройств о содержит сумматор 1 адреса микрокоманд, регистр 2 адреса микрокоманд, блок 3 памяти микропрог- рамм, блок 4 памяти констант, эле мент И 5, регистр,6 микрокоманд, регистр 7 констант мультиплексор 8 логических условий, коммутатор 9,мультиплексор 10 адреса, дешифратор 11, выход 12 устройства, связи 13, 14, 15 и 16 между элементами устройства . выход 17 констант устройства, вход 18 логических условий устройства, связи 19, 20, 21 и 22 между элементами устройства, первый вход 23 тактовых импульсов устройства, вход 24 элемента И 5, второй вход 25 тактовых импульсов устройства, управляющий вход 26 блока 9, вход 27 логического условия перехода па вектор прерывания устройства, связи 28 - 32 между элементами устройства, вход 33 адреса перехода устройства, третий вход 34 тактовых импульсов устройста, входы 35 и 36 соответственно огических О и 1 устройства.

Коммутатор содерлшт мультиплексо ы 37 и 38 и элемент НЕ 39.

Таблица (фиг. 3) определяет выор источника адреса следующей микрооманды в соответствии со значением ода в поле управления переходами

Z (г„, Z,, Z

20

25

30

35

2) в-шкрокоманды и приз- где Р( значение про- Pi, О

наков р,, pj, IMC к,

еряемого Логического условия;

признак перехода по вектору прерываний или признак начального пу ска.

Устройство работает следующим образом.

Адрес микрокоманды с вьжода муль- ти плексора 10 адреса поступает на вход блока 3 памяти микропрограмм и на вход сумматора 1. Б соответствии с этим адресом по тактовому импульсу Т1 производится выборка очередной микрокоманды из блока 3 памяти микропрограмм. С выхода блока 3 памяти микропрограмм микрокоманда поступает на вход регистра ..6 микро15

g

0

0

5

0

команд и переписывается в него по тактовому импульсу Т2. Информация с выхода регистра 6 микрокоманд поступает на вход дешифратора 11, осуществляющего выдачу управляющих сигналов на выход 12, Параллельно, с выхода регистра 6 микрокоманд, на адресный вход мультиплексора 8 поступает код проверяемого условия. Мультиплексор 8 в соответствии с кодом условия выставляет на выход сигнал, принимающий значение проверяемого признака, на входе комг-1утатора 9. Группа логических условий ков поступает на вход мультиплексора 8 по входу 18 устройства.

Коммутатор 9 включает в себя мультиплексоры 37 и 38 и элемент НЕ 39. Каждый из м льтиплексоров 37 и 38 имеет по шесть информационных входов, на которгле (фиг. 2) с входов 35 и 36 соответственно подаются постоянные уровни логических 1 и О, а также прямое и инверсное (через элемент НЕ 38) значения признака Р1, поступающего с выхода мультиплексора 8 и принимающего значение проверяемого логического условия.Под, действием управляющего кода Z (Z, Z, Z,-) s

35

поступающего с выхода регистра 6 м лкрокоман,ц на адресные входы мультиплексоров 37 и 38,и определяющего выбор информационных входов мультиплексоров 37 и 38,коммутатор 9 выдает сигналы А1 и А2 на управляющий вход мультиплексора 10 адреса. Кроме этого на стробиру- ющие входы мультиплексоров 37 и 38 молсет быть вьщан (в особых ситуаци ях) признак р2, который выставляется на входе коммутатора 9 с входа 27 устройства от начала импульса Т2 до окончания импульса Т1 тактовой последовательности и обеспечивает

форгдарование нулевых значений сигналов А.1 и, А2 вне зависимости от состояния информационных и адресных входов мультиплексоров 37 и 38.

0 Сигналы А-1 и А2, сформированные на выходе коммутатора 9, определяют выбор одного из четырех источников адреса следующей микрокоманды. Источниками адреса следующей микроко5 манды могут служить регистр 2 адреса микрокоманд, регистр 6 микрокоманд, регистр 7 констант, выходы которых соединены с информационными входами мультиплексора 10 адреса,

1278846

а также адресный вектор, поступающий на информационный вход мультиплексора 10 адреса с В5:ода 33 устройства. Как показано в таблице (фиг. 3) в зависимости от значения кода в поле Z (ZQ, Z, , Z,) регистра 6 микрокоманд и признаков р и р мультиплексор 10 адреса обеспечивает возможность организации семи типов безусловных и условных переходов в микропрограмме. Адрес следующей микрокоманды с выхода мультиплексора 10 адреса поступает на адресный вход блока 3 памяти микропрограмм и на сумматор 1 . Управление модификацией адреса осуществляется посредством специального признака, поступающего на второй вход сумматора 1 из регистра микрокоманд.

В зависимости от значения данно- го признака адреса на выходе сумматора 1 формируется.модифицированный или немодифицированный адрес, который записывается в регистр 2 адреса микрокоманд по тактовому импульсу ТЗ

Формирование на входе устройства признака р2 обеспечивает возможность прерывания нормального хода выполнения Микропрограмм и безусловную передачу управления микропрог- рамме обработки вектора прерывания Такая ситуация может возникнуть при поступлении запроса от сверхоперативного абонента на немедленное обслуживание или при фиксации аппарат ных сбоев в канале. При включении питания канала ввода-вывода формирование признака р2 обеспечит возможность выхода на начальный адрес

45

микропрограммы подготовки канала вво-40 типлексор логических условий, мульда-вывода к работе.

Для осуществления работы с константами в микрокоманде указывается признак чтения константы, который с выхода регистра 6 микрокоманд .поступает на вход элемента И 5.По тактовому импульсу Т1, который поступает на второй вход элемента И 5, на его выходе сформируется сигнал, управляющий чтением константы из блока 4 памяти констант. Чтение константы производится одновременно с выборкой очередной микрокоманды из блока 3 памяти микропрограмм. При этом источником адреса константы служит регистр 6 микрокоманд, а источником адреса очередной микрокоманды - регистр 2 адреса микрокоманд или регистр 7 констант.

50

55

типлексор адреса и коммутатор, причем первый вход тактовых импульсов устройства подключен к входу чтения блока, памяти микропрограмм и к первому входу элемента И, второй вход и выход которого подключены со- (тветственно к выходу признака об- .ращения к блоку памяти констант регистра микрокоманд и к входу чтения блока памяти констант, выход которого подключен к информационному входу регистра констант, второй выход которого подключен к первому информационному входу мультиплексора адреса, второй, третий информационные входы и управляющий вход которого подключены соответственно к выходу регистра адреса микрокоманд,входу адреса перехода устройства и к

По тактовому импульсу Т2,константа с выхода блока 4 памяти констант переписывается в регистр 7 констант, а очередная микрокоманда фиксируется на регистр 6 микрокоманд. Записанная в регистр 7 констант информация поступает на выход 17 устройства, а также может быть использована в качестве адреса следующей микрокоманды при организации условных переходов, например для возврата из микроподпрограммы, без использования дополнительных микрокоманд.

Формула изобретения

Микропрограммное устройство управления, содержащее сумматор адреса М1крокоманд,регистр адреса микрокоманд, . блок памяти микропрограмм, регистр констант, регистр микрокоманд и дешифратор, причем вьгход поля микрооперации регистра микрокоманд через дещифратор подключен к управляющему выходу устройства, выход блока памяти микропрограмм подключен к информационному входу регистра микрокоманд, выход признака модификации адреса микрокоманд которого подключен к первому входу сумматора адреса микрокоманд, выход которого подключен к инфopмaциoннo ry входу регистра адреса микрокоманд, первый выход регист ра констант подключен к выходу констант устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены блок памяти констант элемент И,муль

типлексор логических условий, муль

типлексор адреса и коммутатор, причем первый вход тактовых импульсов устройства подключен к входу чтения блока, памяти микропрограмм и к первому входу элемента И, второй вход и выход которого подключены со- (тветственно к выходу признака об- ращения к блоку памяти констант регистра микрокоманд и к входу чтения блока памяти констант, выход которого подключен к информационному входу регистра констант, второй выход которого подключен к первому информационному входу мультиплексора адреса, второй, третий информационные входы и управляющий вход которого подключены соответственно к выходу регистра адреса микрокоманд,входу адреса перехода устройства и к

51

выходу коммутатора, выход, адресного поля регистра микрокоманд подключен к адресному входу блока памяти констант и к четвертому информационному входу мультиплексора, адреса, выход которого подключен к втopo fy входу сумматора адреса-микрокоманд и к адресному входу блока памяти мик ропрограмм, второй вход тактовых импульсов устройства подключен к синхровходам регистра констант и регистра микрокоманд, выходы полей номера логического условия и управления адресом перехода регистра мик рокоманд подключены соответственно к управляющему входу мультиплексо2735-36 Г1

J3

Фаг.1

Составитель М.Силин Редактор Л.Гратилло Техред В.Кадар Корректор С.Шекмар

Заказ 6839/47 Тираж 671 Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

11роизводственно-по:1П1графическое предприятие, г. Ужгород, ул. Проектная, 4

788466

ра логических условий и к управляющему входу коммутатора, первый информационный вход которого подключен к выходу мультиплексора ло- 5 гических условий, k-й разряд информационного входа которого подключен к k-му разряду входа логичес- ких условий . устройства (k 1, М, где М - количество логических ус- 10 ловий), второй информационный

вход коммутатора подключен к входу логического условия перехода на вектор прерывания устройства,третий вход тактовьк импульсов устрой- i5 ства подключен к синхровходу регистра адреса микрокоманд.

Фиг..

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

Изобретение относится к вычислительной технике и может быть ис.пользовано в устройствах управления ЭВМ, а также для управления каналами ввода-вывода. Целью изобретения является повышение быстродействия. Устройство содержит сумматор адреса микрокоманд, регистр адреса микрокоманд, блок памяти микропрограмм,блок памяти констант, элемент И, регистр микрокоманд, регистр констант, мультиплексор логических условий,коммутатор, мультиплексор адреса и дешифратор. Поставленная цель достигается за счет совмещения выборки констант с выборкой очередной микрооперации, а также расширенных возможностей адресации. 2 ил.

| Устройство для сопряжения с абонентами | 1974 |

|

SU504199A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления каналом ввода-вывода | 1981 |

|

SU1005047A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-04—Подача