Изобретение относится к электросвязи и может быть использовано для оценки качества передачи информации.

Цель изобретения - повышение точности контроля.

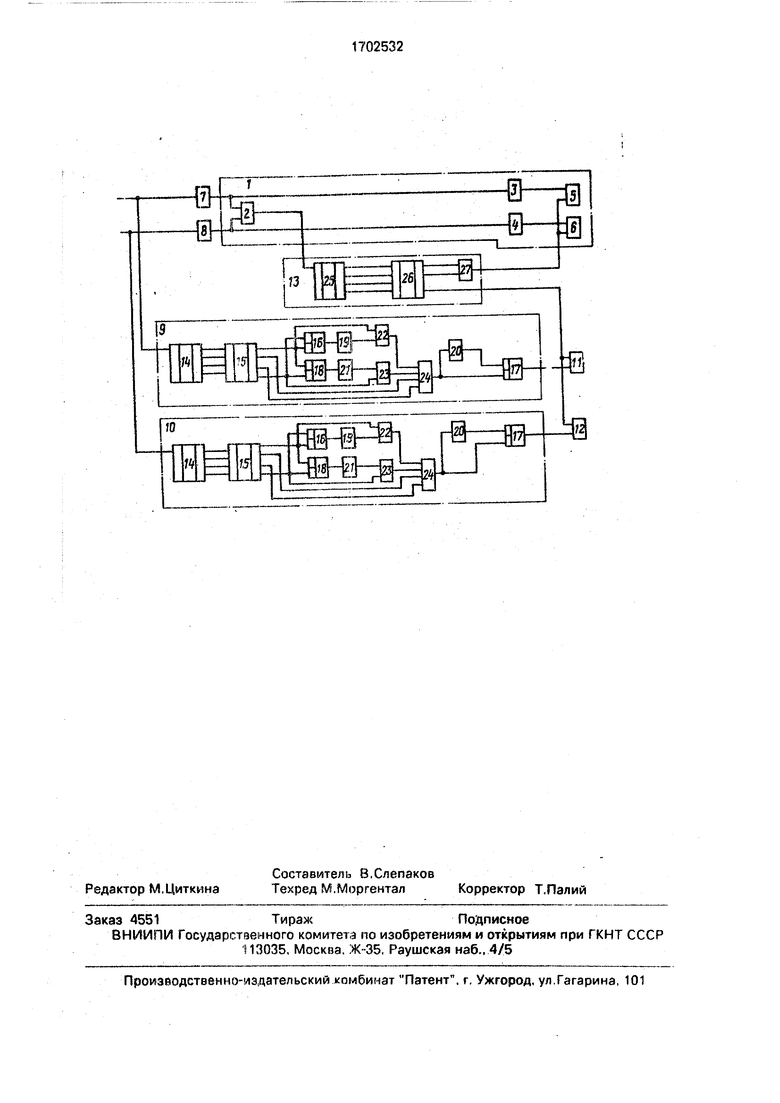

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство для контроля резервированного канала передачи дискретной информации содержит компаратор 1, включающий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, первый и второй элементы задержки 3, 4 и первый и второй элементы И 5 6, первый и второй регулируемые элементы задержки 7, 8. первый и второй блоки 9 10 выявления ошибки, первый и второй элементы совпадения 11, 12 и анализатор

13 причины несовпадения, причем каждый из блоков 9, 10 выявления ошибки включает регистр 14 сдвига, дешифратор 15, первый, второй и третий триггеры 16-18 первый, второй и третий элементы задержки 19-21. первый и второй элементы И 22, 23 и элемент ИЛИ 24, а анализатор 13 причины несовпадения включает регистр 25 сдвига, дешифратор 26 и элемент ИЛИ 27

Устройство работает следующим образом.

Сигналы с выходов основного и резервного каналов подают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 компаратора 1, предварительно сфазировав указанные сигналы посредством двух регулируемых элементов задержки 7 8 Поскольку при этом оба входных сигнала компаратора 1

V4 О Ю 01

со ю

представляют собой по сути один и тот же информационный сигнал, полученный с выходов двух разных каналов, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 будет присутствовать О в течение всего времени нормального функционирования обоих каналов, Возникший в каком-либо из них дефект приведет к несовпадению соответствующих друг другу битов входных сигналов компаратора 1, а это, в свою очередь, проявится в появлении на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 логической единицы или последовательности логических единиц количеством, равным количеству битов, значения которых не совпали друг с другом. Данную единицу или последовательность логических единиц используют в качестве сигнала дефекта. При этом такой дефект, как возникновение одиночной ошибки, будет проявляться в появлении на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 одиночной логической единицы, сопровождаемой достаточно длинной последовательностью нулей. При нарушении физической целостности одного из каналов на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 будет иметь место последовательность логических единиц, по структуре своей совпадающая с последовательностью единиц в информационном сигнале. Для четкой дифференциации обеих ситуаций по каналам (например, линиям волоконно-оптической системы передачи-ВОСП) в качестве информационного передают абсолютный би- импульсный сигнал. При этом условии сигнал дефекта в ВОСП, вызванный нарушением физической целостности одной из линий ВОСП, будет представлять собой чередование единиц и нулей, причем число повторений подряд того или иного двоичного символа ограничено двумя, а в возникновении сдвоенных единиц и сдвоенных нулей будет наблюдаться строгое чередование. Таким образом, сигнал дефекта в ВОСП, вызванный нарушением физической целостности одной из линий ВОСП, будет представлять собой последовательность единиц (одиночных и сдвоенных), разделенных одиночными и сдвоенными нулями. Следовательно, для распознавания причин возникновения сигнала дефекта в ВОСП остаточно проанализировать его структуру в течение времени передачи четырех двоичных символов. Для этой цели сигнал дефекта в ВОСП подают на вход анализатора 13 причины несовпадения, который выполнен на основе каскадного включения четырехразрядного регистра 25 сдвига и четырехвходового дешифратора 26. Сигнал дефекта в ВОСП подают на последовательный вход данных регистра 25. Допустим, что данные сдвигаются от последовательного входа вправо. Тогда единичный символ с выхода элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ. 2 компаратора 1 через промежуток времени, равный времени передачи трех двоичных символов, отобразится на последнем выходе регистра 25. Если проявившийся дефект связан с

0 возникновением одиночной ошибки, то при этом на остальных параллельных выходах регистра 25 будут присутствовать нули. При нарушении физической целостности линии ВОСП на параллельных выхо5 дах регистра 25 будут появляться комбинации двоичных символов, из которых характерными для данного типа дефекта будут те, в которых присутствуют две или три единицы - 0101 1010. 0110,

0 1001 и т.д.

Четырехбитовые параллельные слова с выходов регистра 25 подают на входы дешифратора 26, который преобразовывает входной четырехразрядный код в напряже5 ние логического уровня, появляющегося в том выходном проводе, десятичный номер которого соответствует двоичному коду. Комбинация 1000, свидетельствующая о появлении одиночной ошибки, проявится в по0 явлении на выводе № 8 (третьем выходе дешифратора 26) импульса, который используют в качестве сигнала ошибки в ВОСП и который, таким образом, задержан на временной интервал, занимаемый тремя

5 битами, относительно ошибки в информационном сигнале.

Для стабильной индикации нарушения физической целостности линии ВОСП достаточно использовать две комбинации

0 0101 и 0110, которые проявятся в появлении импульсов на выводах № 5 (0101) и № 6(0110) дешифратора 26 (соответственно его первый и второй выходы). Объединяя данные сигналы посредством элемента ИЛИ 27, с

5 выхода последнего снимают сигнал нарушения физической целостности линий ВОСП, импульсы которого, соответствующие упомянутым комбинациям, будут задержаны каждый на временной интервал, занимае0 мый двумя битами, относительно первого единичного символа соответствующей комбинации. Следовательно, каждый импульс сигнала дефекта в ВОСП может быть опознан как сигнал нарушения физической цело5 стности линии ВОСП только с задержкой на временной Интервал, занимаемый двумя битами, относительно своего появления и, следовательно, относительно соответствующих символов информационных сигналов на входах компаратора 1 Вследствие эюгс

посредством двух элементов задержки 3 и 4 с фиксированной величиной задержки, равной временному интервалу, занимаемому двумя битами, осуществляют задержку информационных сигналов перед подачей последних на входы элементов И 5, 6, на другие входы которых подают сигнал нарушения физической целостности линии ВОСП. Единица на выходе элемента И 5 или 6, связанного с одной из линий ВОСП, будет идентифицировать эту линию ВОСП как линию, в которой на момент фиксации нарушения физической целостности линии ВОСП передается сигнал высокого уровня. Следовательно, единица будет свидетельствовать о ее исправности и соответственно о неисправности второй линии. Вследствие этого сигнал на выходе элемента И 5, связанного с основной ВОСП, используют в качестве сигнала индикации нарушения физической целостности резервной линии ВОСП, и наоборот, сигнал на выходе элемента И б, связанного с резервной ВОСП, используют в качестве сигнала индикации нарушения физической целостности основной линии ВОСП.

Помимо этого фиксируют возникновение каждой одиночной ошибки в ВОСП по появлению соответствующего сигнала ошибки в ВОСП на выводе № 8 дешифратора 26. Одновременно в блоках 9 и 10 анализируют структуры сигналов в каждой линии ВОСП, выявляют некорректные для передаваемого информационного сигнала сочетания символов и по наличию последних делают вывод о присутствии ошибки в конкретной линии ВОСП.

При использовании абсолютного биим- пульсного сигнала в качестве информационного в структуре правильно переданного сигнала имеет место чередование нулей и единиц, перемежаемое сдвоенными единицами и сдвоенными нулями, которые между собой также строго чередуются. О наличии ошибки в сигнале в этом случае будет свидетельствовать появление последовательности единиц или нулей, состоящей из трех или более одинаковых символов подряд, а также наличие сдвоенной единицы или сдвоенного нуля, нарушающих строгое чередование сдвоенных символов. Таким образом, для выявления некорректных сочетаний символов достаточно проанализировать структуру информационного сигнала в течение времени передачи по крайней мере трех двоичных символов. Для этой цели информационные сигналы с выходов основной ВОСП и резервной ВОСП подают на четырехразрядные регистры 14 сдвига соответствующих блоков 9. 10 выявления ошибки, каскадно соединенные с соответствующими дешифраторами 15. Наличие в сигнале более двух одинаковых символов подряд выявляют по появлению активного уровня сигнала на вывод № 7 и г 8 (второй и третий выходы) дешифратора 15, десятичные номера которых соответствуют входным комбинациям символов 0111 и 1000 соответственно. По0 явление импульса на любом из данных выводов дешифратора 15 свидетельстсвует о наличии ошибки в соответствующей линии ВОСП.

Выявление сдвоенных единиц и сдвоен5 ных нулей производят по появлению сигнала на выводах №6 (0110) и №9(1001) первый и четвертый выходы дешифратора 15. Однако наличие сдвоенного символа в сигнале само по себе еще не свидетельствует об

0 ошибке. Для выявления нарушений в чередовании таких символов сигналы с выводов N 6 и № 9 дешифратора 15 подают каждый на разноименные входы первого и третьего триггеров 16 и 18 так, чтобы в каждом триг5 гере один сигнал был подан на вход установки, а второй - на вход сброса. В результате на выходах триггеров 16 и 18 формируют противофазные последовательности прямоугольных импульсов, фронты которых сов0 падают с моментами выявления сдвоенных символов. В отсутствие ошибки сдвоенные символы в информационном сигнале чередуются, следовательно, сигналы на выводах NS 6 и № 9 дешифратора 15 появляются

5 попеременно. Каждому из них в этом случае соответствуют перепады последовательностей прямоугольных импульсов на выходах триггеров 16 и 18. При возникновении ошибки, связанной с появлением лож0 ного сдвоенного символа, в соответствии с указанной структурой информационного сигнала сдвоенная единица (ноль) присутствует в информационном сигнале вместо сдвоенного нуля (единицы), таким обра5 зом, в информационном сигнале в данном случае имеют место три сдвоенных единицы (нуля) подряд, а следовательно, и три подряд импульса на выводе № 6 (№ 9) дешифратора 15. Из этих трех импульсов вто0 рому и третьему не будут соответствовать перепады последовательностей прямоугольных импульсов на выходах триггеров 16 и 18. Данная ситуация будет свидетельствовать о наличии ошибки в информаци5 онном сигнале. Для выявления данной ситуации и, следовательно, выявления ошибки в информационном сигнале последовательности прямоугольных импульсов с выходов триггеров 16 и 18 подают каждую через один из элементов задержки 19. 21 с

величиной задержки, равной временному интервалу, занимаемому двумя битами, на один из входов соответствующего элемента И 22,23. на другой вход которого подают тот сигнал с вывода дешифратора 15, который подан на вход установки данного триггера (16 или 18). При этом в отсутствие ошибки в информационном сигнале на выходах элементов И 22, 23 будет иметь место логический ноль. При наличии ошибки в информационном сигнале, нарушившей чередование сдвоенных символов и повлекшей за собой появление трех подряд импульсов на выводе ISfe 6 или № 9 дешифратора 15, на выходе соответствующего элемента И 22 или 23 получают сопутствующую ошибке в информационном сигнале пару импульсов, первый из которых на временной интервал, занимаемый одним-двумя битами, запаздывает относительно ошибки в информационном сигнале. Положение второго непредсказуемо. Однако, исходя из указанной выше структуры информационного сигнала, легко можно выявить тот факт, что второй импульс запаздывает относительно первого на временной интервал, занимаемый нечетным числом битов. Далее сигналы с выходов элементов И 22. 23 посредством элемента ИЛИ 24 объединяют с сигналами на выводах № 7 и ish 8 дешифратора 15, запаздывающими по отношению к ошибке в информационном сигнале на временной интервал, занимаемый битами числом от нуля до двух. Таким образом, каждая ошибка присутствующая в информационном сигнале, будет сопровождаться появлением с задержкой на временной интервал, занимаемый максимум двумя битами, однобитового импульса на выходе элемента ИЛИ 24, сопровождаемого в некоторых случаях парным ему импульсом, запаздывающим на временной интервал, занимаемый нечетным числом битов.

Для сопоставления данного сигнала с сигналом ошибки в ВОСП, задержанным, как было показано выше, на временной интервал, занимаемый тремя битами, относительно ошибки в информационном сигнале, в соответствии с выходным сигналом элемента ИЛИ 24 должен быть сформирован сигнал ошибки с длительностью, по крайней мере равной временному интервалу, занимаемому четырьмя битами. С этой целью сигнал с выхода элемента ИЛИ 24 подают на вход установки второго триггера 17 того же блока 9 или 10. На вход сброса второго триггера 17 подают тот же сигнал с выхода элемента ИЛИ 24, только задержанный посредством второго элемента задержки 20 на временной интервал, занимаемый таким количеством битов, которое равно выбранной длительности сигнала ошибки. При этом нужно принимать во внимание факт возможного появления в некоторых случаях

второго импульса на выходе элемента ИЛИ 24, соответствующего той же ошибке, которой соответствует первый импульс, и подаваемого на тот же вход установки второго триггера 17. Во избежание неопределенно0 го состояния на выходе второго триггера 17 из-за одновременной подачи на оба его входа логической единицы на вход сброса второго триггера 17 должен быть подан импульс, запаздывающий по отношению к

5 импульсу, поданному на вход установки, на временной интервал, занимаемый четным числом битов. Таким образом, величина задержки второго элемента задержки 20 должна быть равна временному интервалу,

0 занимаемому четным числом битов.-Допустим, величина задержки второго элемента задержки 20 равна временному интервалу, занимаемому четырьмя битами.

Таким образом, на выходе второго

5 триггера 17 формируют сигнал длительностью, равной веременному интервалу, занимаемому четырьмя битами, передний фронт которого на временной интервал, занимаемый максимум двумя битами, зэ0 держан относительно ошибки в информационном сигнале, и используют данный сигнал в качестве сигнала ошибки соответствующего блока 9 или 10 выявления ошибки. Сигналы ошибки с выходов блоков 9 и

5 10 подают на первые входы соответствующих элементов совпадения 11 и 12, на вторые входы которых подают сигнал ошибки в ВОСП. На выходах элементов совпадения 11 и 12 получают, таким образом, сигналы

0 индикации ошибки в основной ВОСП и резервной ВОСП соответственно.

Поскольку при этом раздельно по каждой из линий ВОСП производится индикация всех ошибок, возникающих в линиях

5 ВОСП в течение времени проведения контроля, и время проведения контроля, в свою очередь, не ограничено спецификой устройства, тем самым обеспечивается возможность контроля достоверности передачи

0 сигнала по каждой из линий ВОСП в отдельности и, следовательно, возможность обнаружения выхода из строя линий ВОСП по критерию качества передачи.

Формула изобретения

5 1. Устройство для контроля резервированного канала передачи дискретной информации, содержащее компаратор, включающий первый и второй элементы задержки, первый и второй элементы И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. первый и

второй входы которого являются соответственно первым и вторым входами компаратора, первым и вторым выходами которого являются выходы соответственно первого и второго элементов И. первые входы которых соединены с выходами соответственно первого и второго элементов задержки, отличающееся тем, что, с целью повышения точности контроля, введены первый и второй элементы совпадения, первый и второй регулируемые элементы задержки, первый и второй блоки выявления ошибки и анализатор причины несовпадения, при этом входы первого и второго элементов задержки соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является третьим выходом компаратора, третьим входом которого являются объединенные вторые входы первого и второго элементов И, входы первого и ворого регулируемых элементов задержки, являющиеся входами сигналов соответственно основного и резервного каналов передачи дискретной информации, соединены с входами соответственно первого и второго блоков выявления ошибки, выходы которых подключены к первым входам соответственно первого и второго элементов совпадения, а выходы первого и второго регулируемых элементов задержки подключены соответственно к первому и второму входам компаратора, третий выход которого подключен к его третьему входу через анализатор причины несовпадения, второй выход которого подключен к вторым входам первого и второго элементов совпадения.

2. Устройство по п. 1,отличающев- с я тем, что каждый блок выявления ошибки содержит последовательно соединенные регистр сдвига, дешифратор, первый триггер, первый элемент задержки, первый элемент И, элемент ИЛИ, второй элемент задержки и второй триггер, выход которого является выходом блока выявления ошибки, входом которого является вход регистра

сдвига, и последовательно соединенные третий триггер, третий элемент задержки и второй элемент И, выход которого подключен к второму входу элемента ИЛИ. выходи третий и четвертый входы которого соединены соответственно с входом сброса установки второго триггера и с вторым и третьим выходами дешифратора, четвертый выход которого подключен к второму входу второго элемента И, к входу сброса

установки третьего триггера и к входу сброса установки первого триггера, вход сброса установки которого соединен с входом сброса установки третьего триггера и с вторым входом первого элемента И.

3. Устройство по п. 1.отличающее- с я тем, что анализатор причины несовпадения содержит элемент ИЛИ и последовательно соединенные регистр сдвига и дешифратор, первый и второй выходы которого подключены соответственно к первому и второму входам элемента ИЛИ, выход которого является первым выходом анализатора причины несовпадения, входом и вторым выходом которого являются

соответственно вход регистра сдвига и третий выход дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аппаратурной трансляции | 1982 |

|

SU1056210A1 |

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1661814A1 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА | 2010 |

|

RU2460124C2 |

| АДАПТИВНЫЙ СПОСОБ ОБНАРУЖЕНИЯ И РАСПОЗНАВАНИЯ СИНХРОСИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2238612C2 |

| СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1985 |

|

SU1256670A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2239037C1 |

| Устройство для приема биимпульсных сигналов | 1989 |

|

SU1596477A1 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля. Устр-во содержит компаратор 1, включающий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, элементы задержки 3, 4 и элементы И 5, 6, регулируемые элементы задержки 7, 8, блоки 9, 10 выявления ошибки, элементы совпадения 11, 12 и анализатор 13 причины несовпадения, причем каждый из блоков 9, 10 включает регистр 14 сдвига, дешифратор 15, триггеры 16. 17, 18, элементы задержки 19, 20 21, элементы И 22, 23 и элемент ИЛИ 24, а анализатор 13 включает регистр 25 сдвига, дешифратор 26 и элемент ИЛИ 27 В результате обработки одинаковой информации, поступающей из основного и резервного каналов, индицируются раздельно ошибки, возникающие в каждом из каналов, и сигналы нарушения целостности каждого канала 1 з п ф-лы, 1 ил со

| Автомат для снятия облоя на штампованных каблуках | 1961 |

|

SU143224A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-12-30—Публикация

1989-12-08—Подача