Изобретение относится к вычислительной технике и может быть использовано для обеспечения более полной автоматизации процесса проектирования вычислительных систем (ВС), получения более адекватных оценок производительности проектируемых и эксплуатируемых ВС разной архитектуры, а также в качестве функционального узла системы автоматизированного проектирования (САПР) ВС.

Цель изобретения - расширение области применения и повышение достоверности отладки.

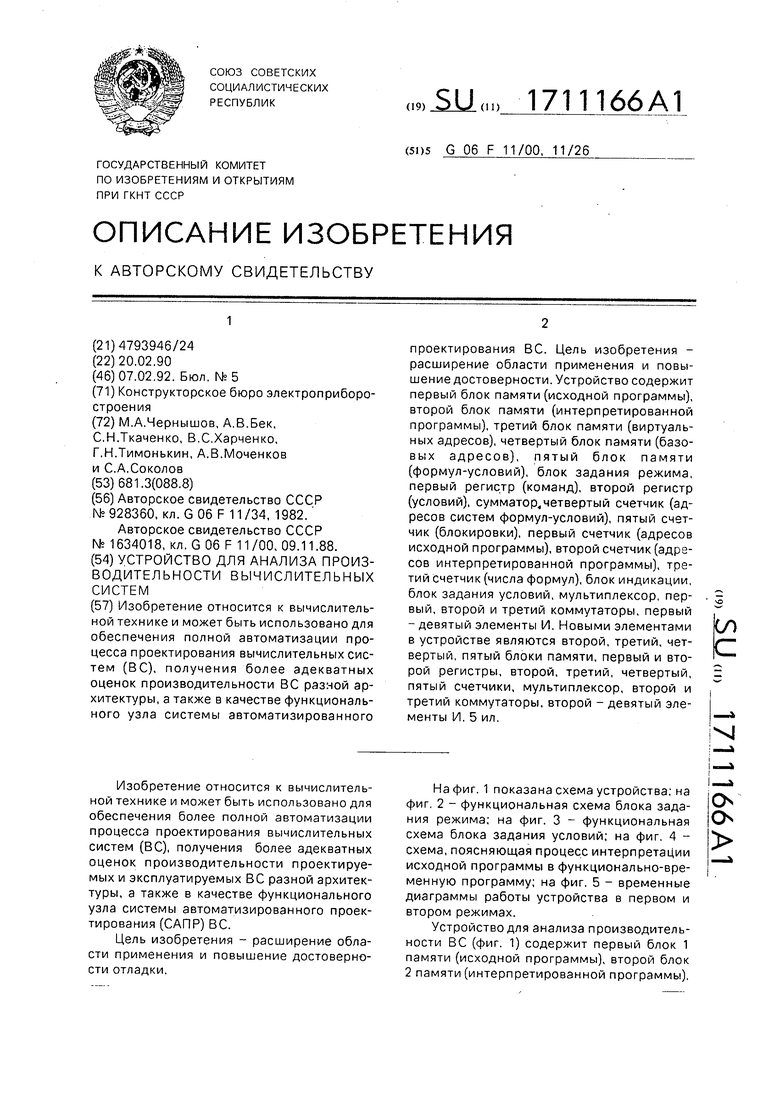

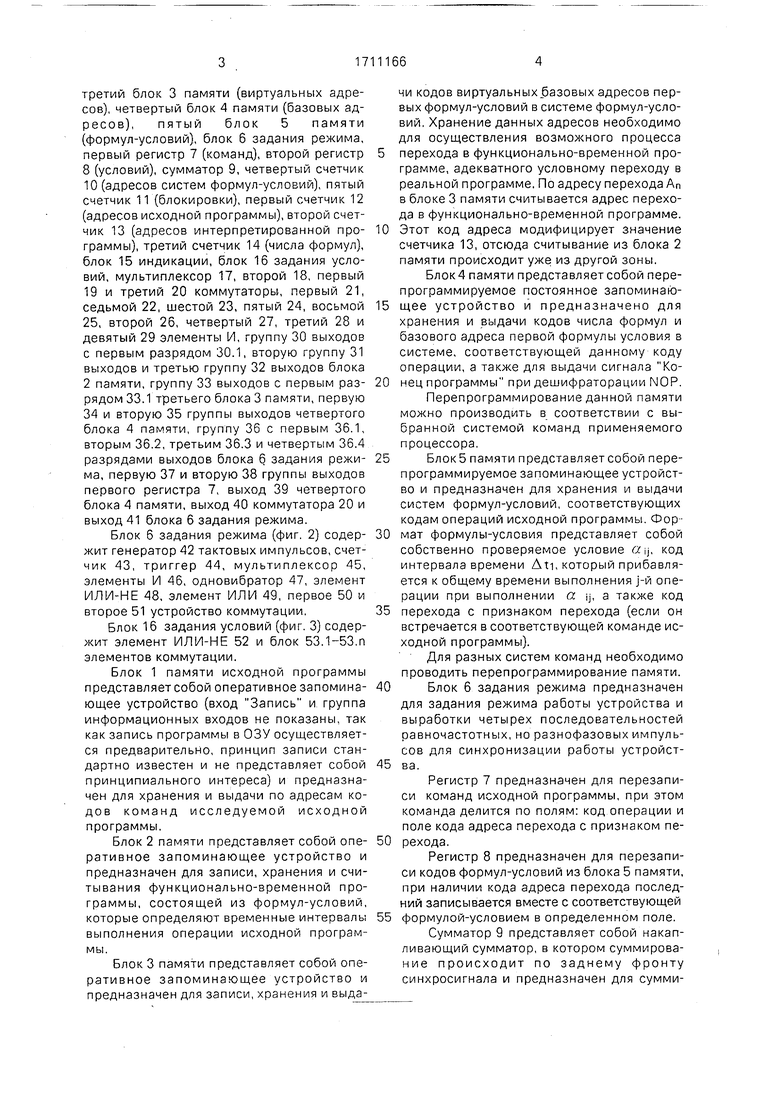

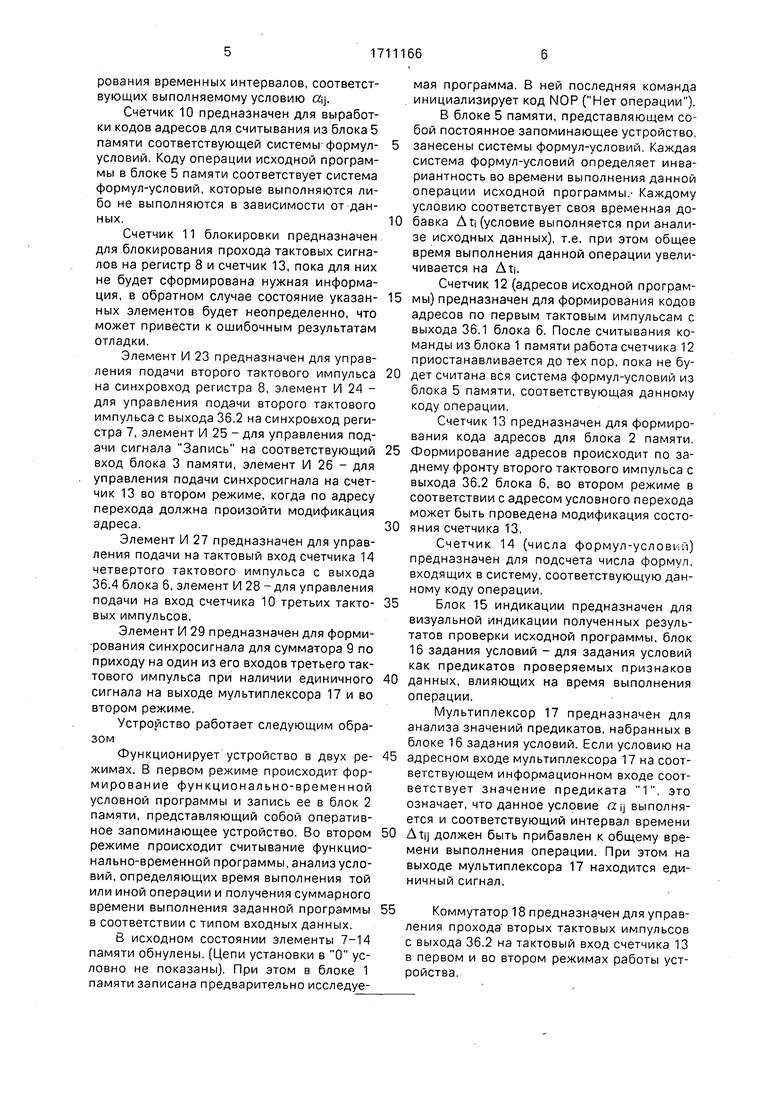

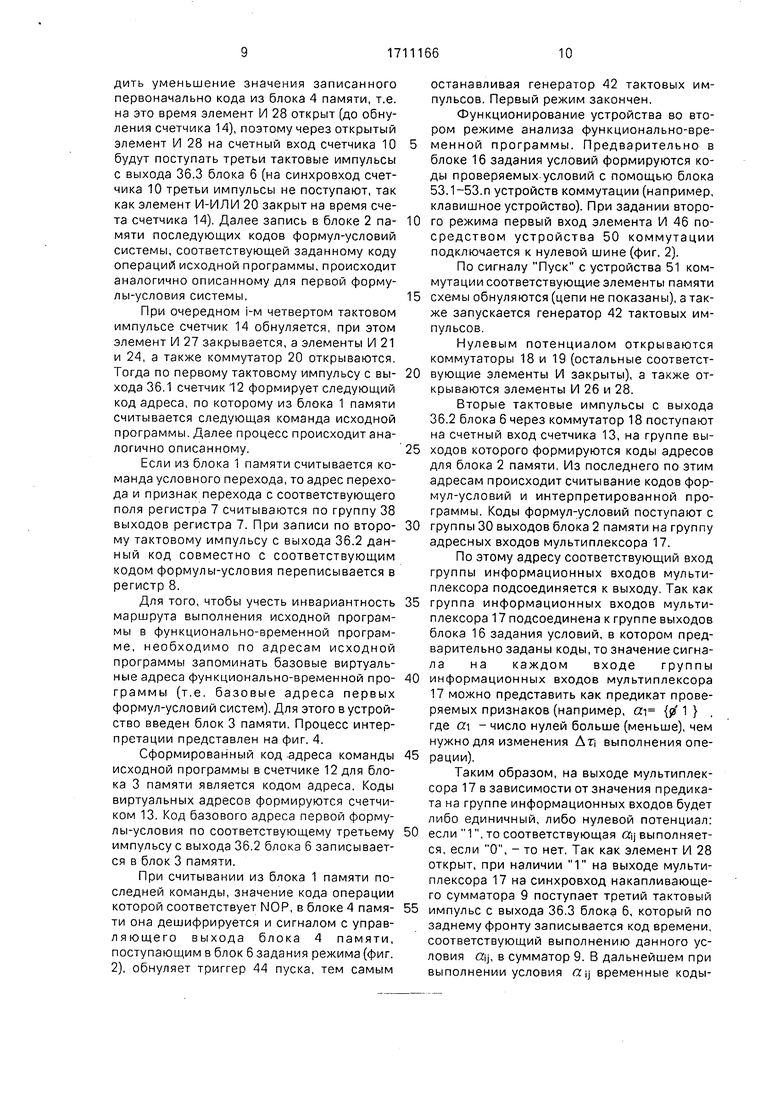

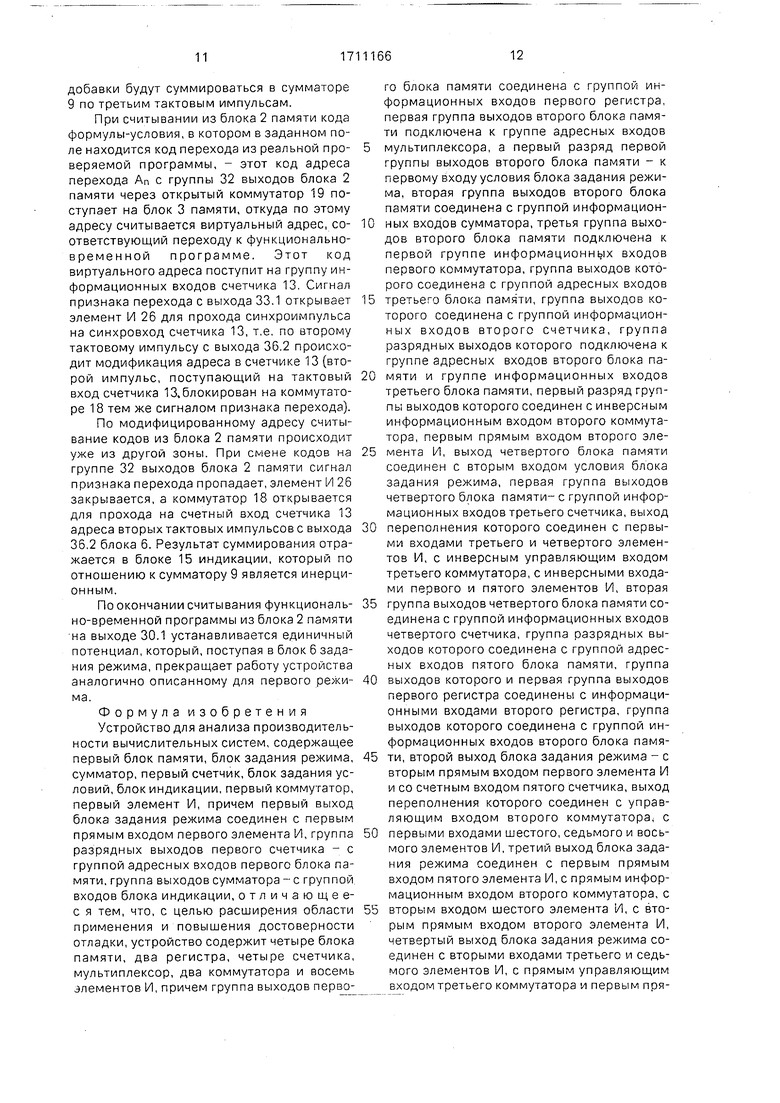

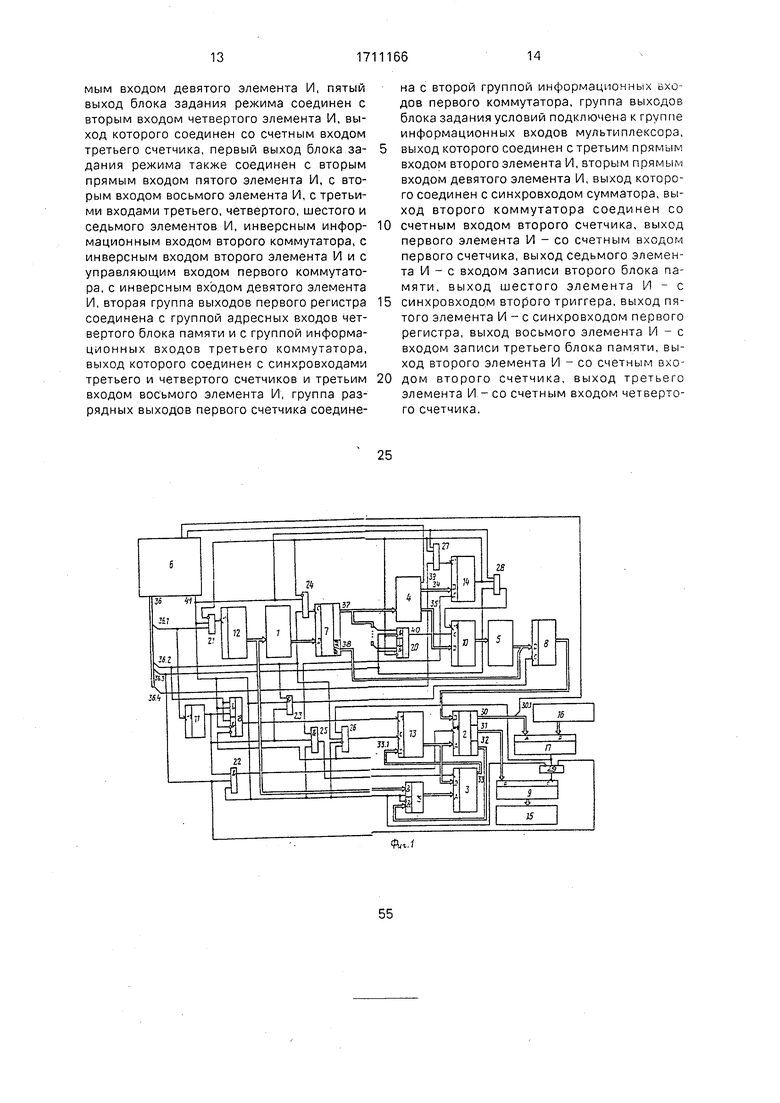

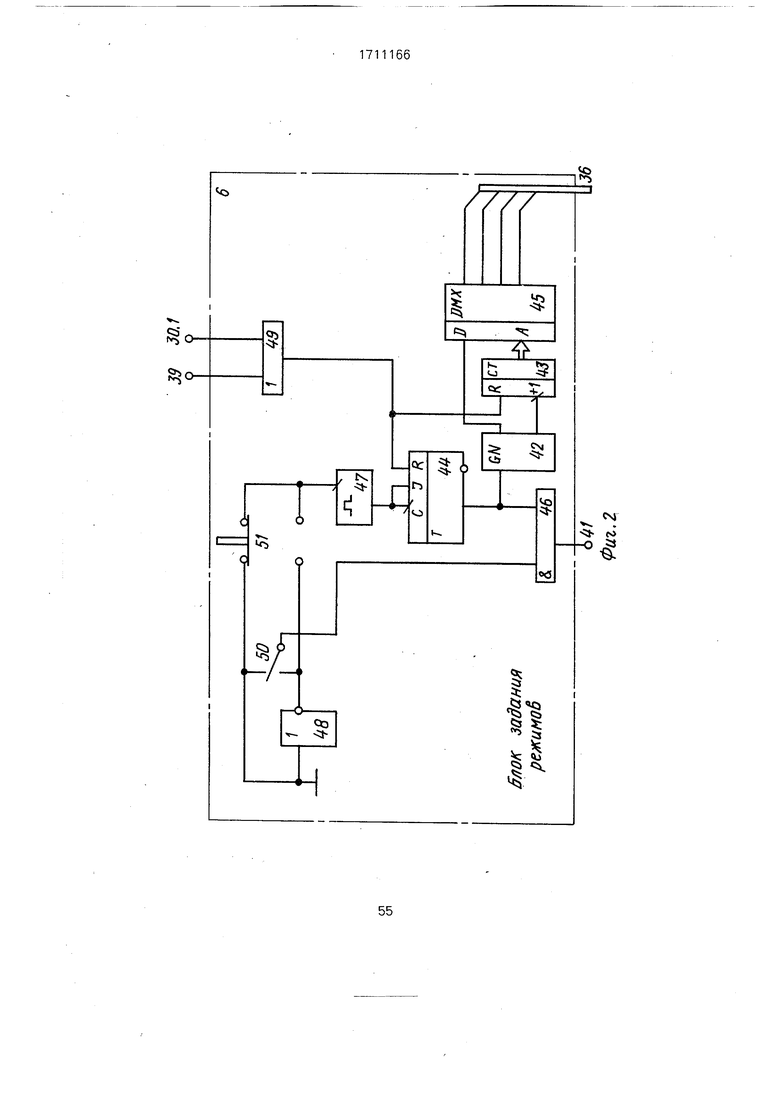

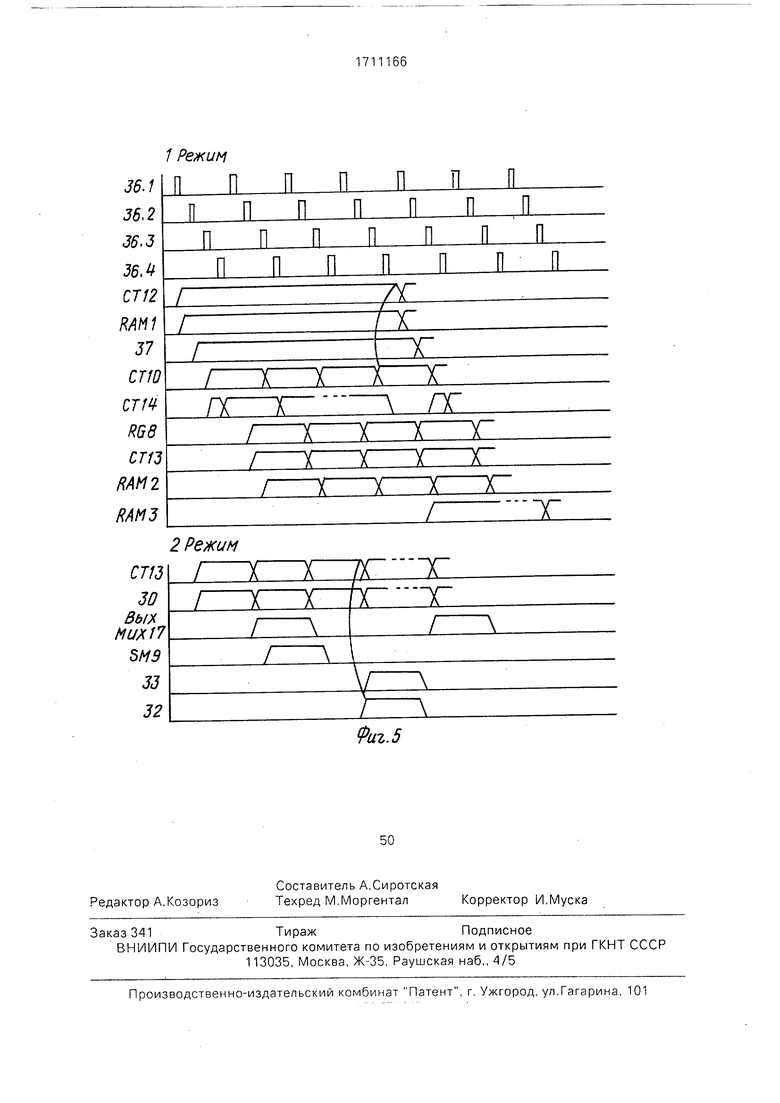

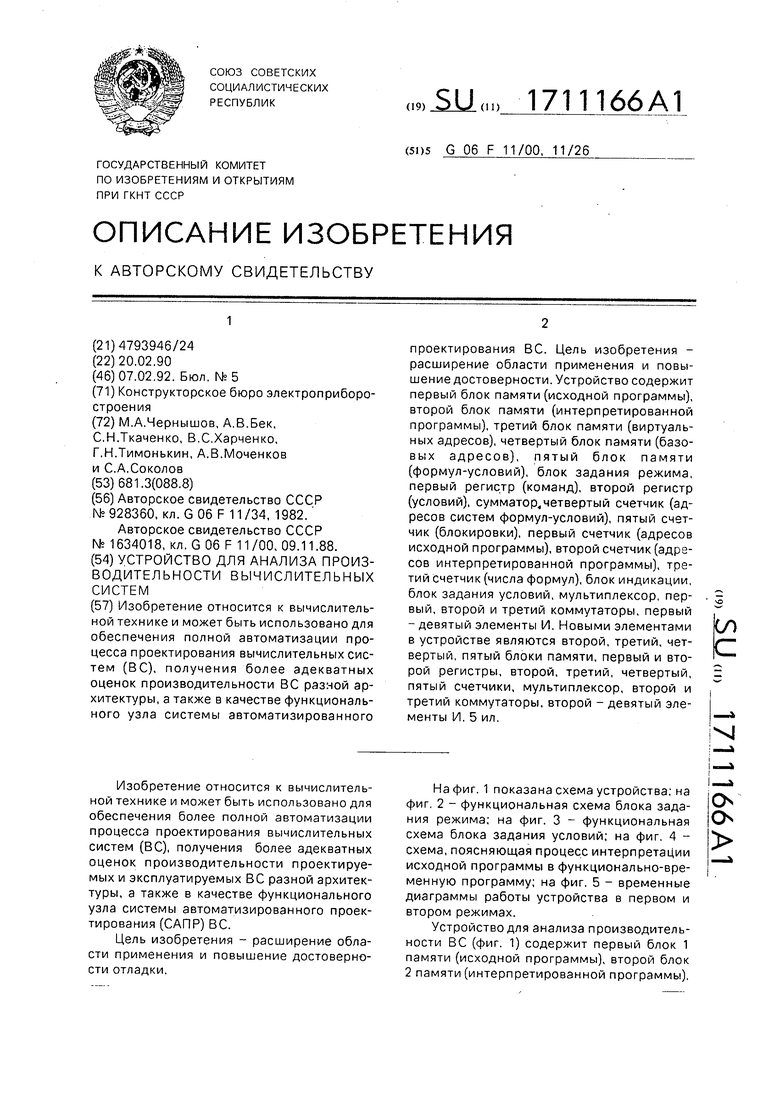

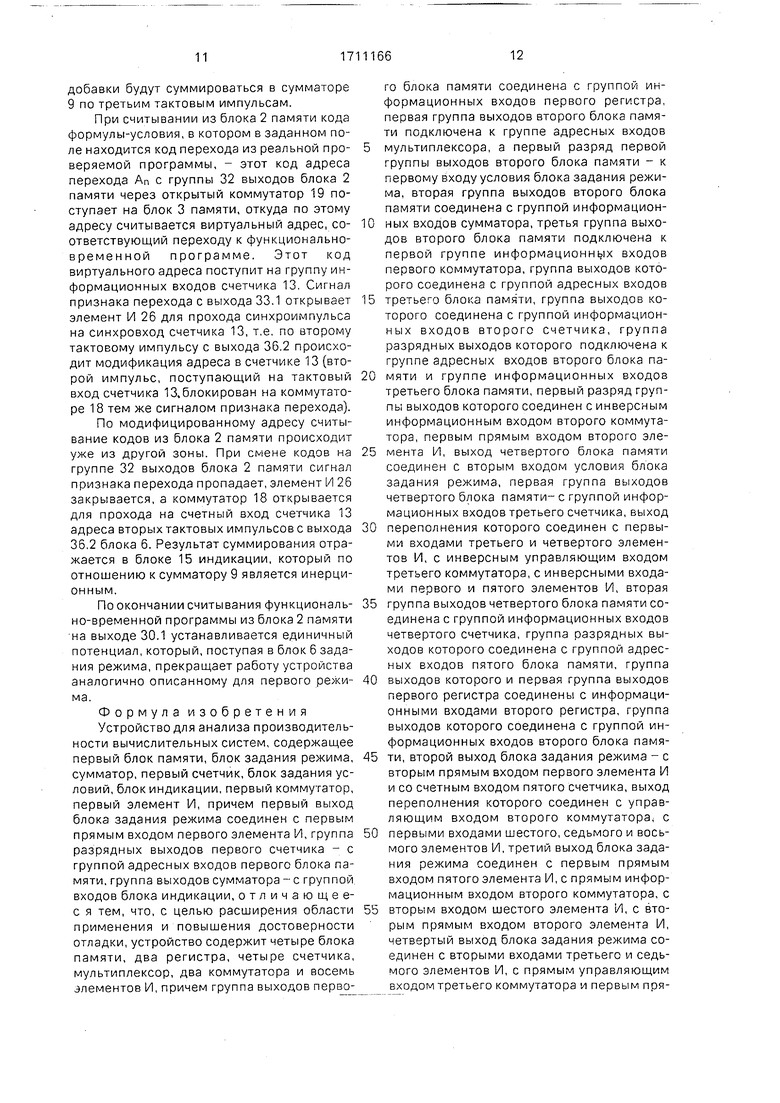

На фиг. 1 показана схема устройства; на фиг. 2 - функциональная схема блока задания режима; на фиг. 3 - функциональная схема блока задания условий; на фиг. 4 - схема, поясняющая процесс интерпретации исходной программы в функционально-временную программу; на фиг, 5 - временные , диаграммы работы устройства в первом и втором режимах.

Устройство для анализа производительности ВС (фиг. 1) содержит первый блок 1 памяти (исходной программы), второй блок 2 памяти (интерпретированной программы),

О

о

третий блок 3 памяти (виртуальных адресов), четвертый блок 4 памяти (базовых адресов), пятый блок 5 памяти (формул-условий), блок 6 задания режима, первый регистр 7 (команд), второй регистр 8 (условий), сумматор 9, четвертый счетчик 10 (адресов систем формул-условий), пятый счетчик 11 (блокировки), первый счетчик 12 (адресов исходной программы), второй счетчик 13 (адресов интерпретированной программы), третий счетчик 14 (числа формул), блок 15 индикации, блок 16 задания условий, мультиплексор 17, второй 18, первый 19 и третий 20 коммутаторы, первый 21, седьмой 22, шестой 23, пятый 24, восьмой 25, второй 26, четвертый 27, третий 28 и девятый 29 элементы И, группу 30 выходов с первым разрядом 30.1, вторую группу 31 выходов и третью группу 32 выходов блока 2 памяти, группу 33 выходов с первым разрядом 33.1 третьего блока 3 памяти, первую 34 и вторую 35 группы выходов четвертого блока 4 памяти, груп пу 36 с первым 36.1, вторым 36.2, третьим 36.3 и четвертым 36.4 разрядами выходов блока 6. задания режима, первую 37 и вторую 38 группы выходов первого регистра 7, выход 39 четвертого блока 4 памяти, выход 40 коммутатора 20 и выход 41 блока 6 задания режима.

Блок 6 задания режима (фиг. 2) содержит генератор 42 тактовых импульсов, счетчик 43, триггер 44, мультиплексор 45, элементы И 46, одновибратор 47, элемент ИЛИ-НЕ 48, элемент ИЛИ 49, первое 50 и второе 51 устройство коммутации.

Блок 16 задания условий (фиг. 3) содержит элемент ИЛИ-НЕ 52 и блок 53.1-53.п элементов коммутации.

Блок 1 памяти исходной программы представляет собой оперативное запоминающее устройство (вход Запись и. группа информационных входов не показаны, так как запись программы в ОЗУ осуществляется предварительно, принцип записи стандартно известен и не представляет собой принципиального интереса) и предназначен для хранения и выдачи по адресам кодов команд исследуемой исходной программы.

Блок 2 памяти представляет собой оперативное запоминающее устройство и предназначен для записи, хранения и считывания функционально-временной программы, состоящей из формул-условий, которые определяют временные интервалы выполнения операции исходной программы.

Блок 3 памяти представляет собой оперативное запоминающее устройство и предназначен для записи, хранения и выдачи кодов виртуальных базовых адресов первых формул-условий в системе формул-условий. Хранение данных адресов необходимо для осуществления возможного процесса

перехода в функционально-временной программе, адекватного условному переходу в реальной программе. По адресу перехода Ап в блоке 3 памяти считывается адрес перехода в функционально-временной программе.

Этот код адреса модифицирует значение счетчика 13, отсюда считывание из блока 2 памяти происходит уже из другой зоны.

Блок 4 памяти представляет собой перепрограммируемое постоянное запоминающее устройство и предназначено для хранения и выдачи кодов числа формул и базового адреса первой формулы условия в системе, соответствующей данному коду операции, а также для выдачи сигнала Конец программы при дешифраторации NOP. Перепрограммирование данной памяти можно производить в соответствии с выбранной системой команд применяемого процессора.

Блок 5 памяти представляет собой перепрограммируемое запоминающее устройство и предназначен для хранения и выдачи систем формул-условий, соответствующих кодам операций исходной программы. Формат формулы-условия представляет собой собственно проверяемое условие а, код интервала времени Ati, который прибавляется к общему времени выполнения j-й операции при выполнении а , а также код

перехода с признаком перехода (если он встречается в соответствующей команде исходной программы).

Для разных систем команд необходимо проводить перепрограммирование памяти.

Блок 6 задания режима предназначен для задания режима работы устройства и выработки четырех последовательностей равночастотных, но разнофазовых импульсов для синхронизации работы устройства.

Регистр 7 предназначен для перезаписи команд исходной программы, при этом команда делится по полям: код.операции и поле кода адреса перехода с признаком перехода.

Регистр 8 предназначен для перезаписи кодов формул-условий из блока 5 памяти, при наличии кода адреса перехода последний записывается вместе с соответствующей

формулой-условием в определенном поле.

Сумматор 9 представляет собой накапливающий сумматор, в котором суммирование происходит по заднему фронту синхросигнала и предназначен для суммирования временных интервалов, соответствующих выполняемому условию «ц.

Счетчик 10 предназначен для выработки кодов адресов для считывания из блока 5 памяти соответствующей системы формул- условий. Коду операции исходной программы в блоке 5 памяти соответствует система формул-условий, которые выполняются либо не выполняются в зависимости отданных.

Счетчик 11 блокировки предназначен для блокирования прохода тактовых сигналов на регистр 8 и счетчик 13, пока для них не будет сформирована нужная информация, в обратном случае состояние указан- ных элементов будет неопределенно, что может привести к ошибочным результатам отладки.

Элемент И 23 предназначен для управления подачи второго тактового импульса на синхровход регистра 8, элемент И 24 - для управления подачи второго тактового импульса с выхода 36.2 на синхровход регистра 7, элемент И 25 -для управления подачи сигнала Запись на соответствующий вход блока 3 памяти, элемент И 26 - для управления подачи синхросигнала на счетчик 13 во втором режиме, когда по адресу перехода должна произойти модификация адреса.

Элемент И 27 предназначен для управления подачи на тактовый вход счетчика 14 четвертого тактового импульса с выхода 36.4 блока 6, элемент И 28 - для управления подачи на вход счетчика 10 третьих такто- вых импульсов.

Элемент И 29 предназначен для формирования синхросигнала для сумматора 9 по приходу на один из его входов третьего тактового импульса при наличии единичного сигнала на выходе мультиплексора 17 и во втором режиме.

Устройство работает следующим образом

Функционирует устройство в двух ре- жимах. В первом режиме происходит формирование функционально-временной условной программы и запись ее в блок 2 памяти, представляющий со.бой оперативное запоминающее устройство. Во втором режиме происходит считывание функционально-временной программы, анализ условий, определяющих время выполнения той или иной операции и получения суммарного времени выполнения заданной программу в соответствии с типом входных данных

В исходном состоянии элементы 7-14 памяти обнулены. (Цепи установки в О условно не показаны). При этом в блоке 1 памяти записана предварительно исследуемая программа. В ней последняя команда инициализирует код NOP (Нет операции).

В блоке 5 памяти, представляющем собой постоянное запоминающее устройство, занесены системы формул-условий. Каждая система формул-условий определяет инвариантность во времени выполнения данной операции исходной программы.- Каждому условию соответствует своя временная добавка Atj (условие выполняется при анализе исходных данных), т.е. при этом общее время выполнения данной операции увеличивается на Ati.

Счетчик 12 (адресов исходной программы) предназначен для формирования кодов адресов по первым тактовым импульсам с выхода 36.1 блока 6. После считывания команды из блока Т памяти работа счетчика 12 приостанавливается до тех пор, пока не будет считана вся система формул-условий из блока 5 памяти, соответствующая данному коду операции.

Счетчик 13 предназначен для формирования кода адресов для блока 2 памяти. Формирование адресов происходит по заднему фронту второго тактового импульса с выхода 36.2 блока 6, во втором режиме в соответствии с адресом условного перехода может быть проведена модификация состояния счетчика 13.

Счетчик 14 (числа формул-условий) предназначен для подсчета числа формул, входящих в систему, соответствующую данному коду операции.

Блок 15 индикации предназначен для визуальной индикации полученных результатов проверки исходной программы, блок 16 задания условий - для задания условий как предикатов проверяемых признаков данных, влияющих на время выполнения операции.

Мультиплексор 17 предназначен для анализа значений предикатов, набранных в блоке 16 задания условий. Если условию на адресном входе мультиплексора 17 на соответствующем информационном входе соответствует значение предиката 1, это означает, что данное условие а выполняется и соответствующий интервал времени Atij должен быть прибавлен к общему времени выполнения операции. При этом на выходе мультиплексора 17 находится единичный сигнал.

Коммутатор 18 предназначен для управления прохода вторых тактовых импульсов с выхода 36.2 на тактовый вход счетчика 13 в первом и во втором режимах работы устройства.

Коммутатор 19 предназначен для управления процессом поступления кодов адресов для блока 3 памяти в первом и во втором режимах, коммутатор 20 - для управления подачей третьего тактового импульса с выхода 36.3 на синхровходы счетчиков 14 и 10.

Элемент И 21 предназначен для управления подачи первого тактового импульса с выхода 36.1 на тактовый вход счетчика 12, элемент И 22 - для управления подачи сигнала Запись на блок 2 памяти.

В блоке 4 памяти, представляющем собой постоянное запоминающее устройство, занесена информация в виде кодов. Код операции исходной программы является адресом, по которому из блока 4 памяти считывается код числа формул-условий и код адреса начальной формулы-условия системы, находящейся в блоке 5 памяти и соответствующей данному коду операции.

Функционирование устройства в первом режиме.

Первый режим задается в блоке 6 задания (фиг. 2) режима устройства 50 коммутации подачей единичного потенциального сигнала с выхода элемента ИЛИ-НЕ 48 на первый вход элемента И 46. Устройством 51 коммутации подается кратковременный сигнал на вход одновибратора 47, где по заднему фронту формируется импульсный сигнал, который подается на совмещенные установочные входы триггера 44 пуска. Единичный потенциал с выхода триггера 44 пуска запускает генератор 42 тактовых импульсов и формирует сигнал на выходе 41 блока 6 задания режима. Сигнал пуска для первого режима открывает соответствующие элементы И для пропуска тактовых сиг- налов на соответствующие элементы памяти.

Через открытый элемент И 21 на счетный вход счетчика 12 исходного адреса поступает первый тактовый импульс с выхода 36.1 группы 36 выходов блока 6 задания режима (элемент И 21 открыт) и по второму нулевому управляющему входу, так как на нем стоит нулевой потенциал с выхода обнуленного счетчика 14 числа формул-условий. По первому тактовому импульсу на группе выходов счетчика 12 исходного адреса формируется код адреса, по которому из блока 1 памяти считывается код первой команды исходной программы. Данный код по второму тактовому импульсу переписывается в регистр 7. Код операции, поступающий с группы 37 выходов регистра 7, является кодом адреса для блока 4 памяти, по которому из последнего считываются соответствующие коду операции исходной программы код числа формул-условий группы 34 выходов блока и код базового адреса первой формулы-условия системы условий с группы 35 выходов блока 4 памяти. Код числа формул-условий по третьему тактовому

импульсу, поступающему с выхода 36.3 блока 6 через открытый блок 20 элементов И, записывается в счетчик 14 числа формул-условий, а код базового адреса первой формулы системы по тому же тактовому импульсу

0 записывается в счетчик 10. С группы выходов счетчика 10 код базового адреса поступает на группу входов блока 5 памяти, откуда считывается код а. ц.первой формулы условия i-ro кода операции. По второму

5 тактовому импульсу с выхода 36.2 блока 6 данный код переписывается в регистр 8 и поступает на группу информационных входов блока 2 памяти функциональной временной программы.

0 По второму тактовому импульсу с выхода 36.2 блока счетчик 13 адреса интерпретированной программы формирует код адреса для блока 2 памяти. Данный второй тактовый импульс с выхода 36.2 блока 6 принад5 лежит второй серии последовательности четырех импульсов, различных по фазе. Первая серия импульсов в целях синхронизации работы устройства вырезается счетчиком 11, настроенным на заданное число

0 импульсов (в данном случае два). Сигнал переполнения по первому тактовому импульсу открывает коммутатор 18 для прохождения вторых импульсов с выхода 36.2 блока 6. Таким образом, код первой форму5 лы системы, соответствующий первому коду операции по адресу с группы выходов счетчика 13 по заднему фронту третьего тактового импульса второй серии импульсов с выхода 36.2 блока 6, записывается в блок 2

0 памяти,

Запись в блок 2 памяти следующих формул-условий системы, соответствующей первому коду операции исходной программы, происходит следующим образом. При

5 записи кода числа формул-условий в счетчике 14 на его выходе по заднему фронту третьего тактового импульса с выхода 36.3 блока 6 устанавливается единичный потенциал, который по переднему фронту откры0 вает элемент И 27, а закрывает элементы И 21 и 24 и коммутатор 20. Первый и второй тактовые импульсы с выходов 36.1 и 36.3 блока 6 не проходят на соответствующие входы счетчика 12 и регистра 7, т.е. считы5 вание следующей команды исходной программы приостанавливается.

По четвертому тактовому импульсу с выхода 36.4 блока 6, поступающему через открытый элемент И 27 на счетный вход счетчика 14, в счетчике 14 будет происходить уменьшение значения записанного первоначально кода из блока 4 памяти, т.е. на это время элемент И 28 открыт (до обнуления счетчика 14), поэтому через открытый элемент И 28 на счетный вход счетчика 10 будут поступать третьи тактовые импульсы с выхода 36.3 блока 6 (на синхровход счетчика 10 третьи импульсы не поступают, так как элемент И-ИЛИ 20 закрыт на время счета счетчика 14). Далее запись в блоке 2 памяти последующих кодов формул-условий системы, соответствующей заданному коду операций исходной программы, происходит аналогично описанному для первой формулы-условия системы.

При очередном i-м четвертом тактовом импульсе счетчик 14 обнуляется, при этом элемент И 27 закрывается, а элементы И 21 и 24, а также коммутатор 20 открываются. Тогда по первому тактовому импульсу с выхода 36.1 счетчик 12 формирует следующий код адреса, по которому из блока 1 памяти считывается следующая команда исходной программы. Далее процесс происходит аналогично описанному.

Если из блока 1 памяти считывается команда условного перехода, то адрес перехода и признак перехода с соответствующего поля регистра 7 считываются по группу 38 выходов регистра 7. При записи по второму тактовому импульсу с выхода 36.2 данный код совместно с соответствующим кодом формулы-условия переписывается в регистр 8,

Для того, чтобы учесть инвариантность маршрута выполнения исходной программы в функционально-временной программе, необходимо по адресам исходной программы запоминать базовые виртуальные адреса функционально-временной программы (т.е. базовые адреса первых формул-условий систем), Для этого в устройство введен блок 3 памяти. Процесс интерпретации представлен на фиг. 4.

Сформированный код адреса команды исходной программы в счетчике 12 для блока 3 памяти является кодом адреса. Коды виртуальных адресов формируются счетчиком 13. Код базового адреса первой формулы-условия по соответствующему третьему импульсу с выхода 36.2 блока 6 записывается в блок 3 памяти.

При считывании из блока 1 памяти последней команды, значение кода операции которой соответствует NOP, в блоке 4 памяти она дешифрируется и сигналом с управляющего выхода блока 4 памяти, поступающим в блок 6 задания режима (фиг. 2), обнуляет триггер 44 пуска, тем самым

останавливая генератор 42 тактовых импульсов. Первый режим закончен.

Функционирование устройства во втором режиме анализа функционально-временной программы. Предварительно в блоке 16 задания условий формируются коды проверяемых условий с помощью блока 53.1-53.п устройств коммутации (например, клавишное устройство). При задании второго4 режима первый вход элемента И 46 посредством устройства 50 коммутации подключается к нулевой шине (фиг. 2).

По сигналу Пуск с устройства 51 коммутации соответствующие элементы памяти

схемы обнуляются (цепи не показаны), а также запускается генератор 42 тактовых импульсов.

Нулевым потенциалом открываются коммутаторы 18 и 19 (остальные соответствующие элементы И закрыты), а также открываются элементы И 26 и 28.

Вторые тактовые импульсы с выхода 36.2 блока 6 через коммутатор 18 поступают на счетный вход счетчика 13, на группе выходов которого формируются коды адресов для блока 2 памяти. Из последнего по этим адресам происходит считывание кодов формул-условий и интерпретированной программы. Коды формул-условий поступают с

группы 30 выходов блока 2 памяти на группу адресных входов мультиплексора 17.

По этому адресу соответствующий вход группы информационных входов мультиплексора подсоединяется к выходу. Так как

группа информационных входов мультиплексора 17 подсоединена к группе выходов блока 16 задания условий, в котором предварительно заданы коды, то значение сигна- ла на каждом входе группы

информационных входов мультиплексора 17 можно представить как предикат проверяемых признаков (например, «1 {}(1 } , где а - число нулей больше (меньше), чем нужно для изменения Дт) выполнения операции).

Таким образом, на выходе мультиплексора 17 в зависимости от значения предиката на группе информационных входов будет либо единичный, либо нулевой потенциал:

если 1, то соответствующая « выполняется, если О, - то нет. Так как элемент И 28 открыт, при наличии 1 на выходе мультиплексора 17 на синхровход накапливающего сумматора 9 поступает третий тактовый

импульс с выхода 36.3 блока 6, который по заднему фронту записывается код времени, соответствующий выполнению данного условия а, в сумматор 9. В дальнейшем при выполнении условия а временные кодыдобавки будут суммироваться в сумматоре 9 по третьим тактовым импульсам.

При считывании из блока 2 памяти кода формулы-условия, в котором в заданном поле находится код перехода из реальной проверяемой программы, - этот код адреса перехода Ап с группы 32 выходов блока 2 памяти через открытый коммутатор 19 поступает на блок 3 памяти, откуда по этому адресу считывается виртуальный адрес, соответствующий переходу к функционально- временной программе. Этот код виртуального адреса поступит на группу информационных входов счетчика 13. Сигнал признака перехода с выхода 33.1 открывает элемент И 26 для прохода синхроимпульса на синхровход счетчика 13, т.е. по второму тактовому импульсу с выхода 36.2 происходит модификация адреса в счетчике 13 (второй импульс, поступающий на тактовый вход счетчика 13, блокирован на коммутаторе 18 тем же сигналом признака перехода).

По модифицированному адресу считывание кодов из блока 2 памяти происходит уже из другой зоны. При смене кодов на группе 32 выходов блока 2 памяти сигнал признака перехода пропадает, элемент И 26 закрывается, а коммутатор 18 открывается для прохода на счетный вход счетчика 13 адреса вторых тактовых импульсов с выхода 36.2 блока 6. Результат суммирования отражается в блоке 15 индикации, который по отношению к сумматору 9 является инерционным.

По окончании считывания функционально-временной программы из блока 2 памяти на выходе 30.1 устанавливается единичный потенциал, который, поступая в блок 6 задания режима, прекращает работу устройства аналогично описанному для первого режима.

Формула изобретения

Устройство для анализа производительности вычислительных систем, содержащее первый блок памяти, блок задания режима, сумматор, первый счетчик, блок задания условий, блок индикации, первый коммутатор, первый элемент И, причем первый выход блока задания режима соединен с первым прямым входом первого элемента И, группа разрядных выходов первого счетчика - с группой адресных входов первого блока памяти, группа выходов сумматора - с группой, входов блока индикации, отличающееся тем, что, с целью расширения области применения и повышения достоверности отладки, устройство содержит четыре блока памяти, два регистра, четыре счетчика, мультиплексор, два коммутатора и восемь элементов И, причем группа выходов первого блока памяти соединена с группой информационных входов первого регистра, первая группа выходов второго блока памяти подключена к группе адресных входов

мультиплексора, а первый разряд первой группы выходов второго блока памяти - к первому в ходу условия блока задания режима, вторая группа выходов второго блока памяти соединена с группой информацион0 ных входов сумматора, третья группа выходов второго блока памяти подключена к первой группе информационных входов первого коммутатора, группа выходов которого соединена с группой адресных входов

5 третьего блока памяти, группа выходов которого соединена с группой информационных входов второго счетчика, группа разрядных выходов которого подключена к группе адресных входов второго блока па0 мяти и группе информационных-входов третьего блока памяти, первый разряд группы выходов которого соединен с инверсным информационным входом второго коммутатора, первым прямым входом второго эле5 мента И, выход четвертого блока памяти соединен с. вторым входом условия блока задания режима, первая группа выходов четвертого блока памяти- с группой информационных входов третьего счетчика, выход

0 переполнения которого соединен с первыми входами третьего и четвертого элементов И, с инверсным управляющим входом третьего коммутатора, с инверсными входами первого и пятого элементов И, вторая

5 группа выходов четвертого блока памяти соединена с группой информационных входов четвертого счетчика, группа разрядных выходов которого соединена с группой адресных входов пятого блока памяти, группа

0 выходов которого и первая группа выходов первого регистра соединены с информационными входами второго регистра, группа выходов которого соединена с группой информационных входов второго блока памя5 ти, второй выход блока задания режима - с вторым прямым входом первого элемента И и со счетным входом пятого счетчика, выход переполнения которого соединен с управляющим входом второго коммутатора( с

0 первыми входами шестого, седьмого и восьмого элементов И, третий выход блока задания режима соединен с первым прямым входом пятого элемента И, с прямым информационным входом второго коммутатора, с

5 вторым входом шестого элемента И, с вторым прямым входом второго элемента И, четвертый выход блока задания режима соединен с вторыми входами третьего и седьмого элементов И, с прямым управляющим входом третьего коммутатора и первым прямым входом девятого элемента И, пятый выход блока задания режима соединен с вторым входом четвертого элемента И, вы- ход которого соединен со счетным входом третьего счетчика, первый выход блока.заания режима также соединен с вторым прямым входом пятого элемента И, с вторым входом восьмого элемента И, с третьими входами третьего, четвертого, шестого и седьмого элементов И, инверсным информационным входом второго коммутатора, с инверсным входом второго элемента И и с управляющим входом первого коммутатора, с инверсным входом девятого элемента И, вторая группа выходов первого регистра соединена с группой адресных входов четвертого блока памяти и с группой информационных входов третьего коммутатора, выход которого соединен с синхровходами третьего и четвертого счетчиков и третьим входом восьмого элемента И, группа разрядных выходов первого счетчика соединена с второй группой информационных входов первого коммутатора, группа выходов блока задания условий подключена к группе информационных входов мультиплексора,

выход которого соединен с третьим прямым входом второго элемента И, вторым прямым входом девятого элемента И, выход которого соединен с синхровходом сумматора, выход второго коммутатора соединен со

счетным входом второго счетчика, выход первого элемента И - со счетным входом первого счетчика, выход седьмого элемента И - с входом записи второго блока памяти, выход шестого элемента И - с

синхровходом второго триггера, выход пятого элемента И - с синхровходом первого регистра, выход восьмого элемента I/I - с входом записи третьего блока памяти, выход второго элемента И - со счетным входом второго счетчика, выход третьего элемента И - со счетным входом четвертого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля тестопригодных программ | 1990 |

|

SU1751767A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| Устройство для коррекции программ | 1990 |

|

SU1751768A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

Изобретение относится к вычислительной технике и может быть использовано для обеспечения полной автоматизации процесса проектирования вычислительных систем (ВС), получения более адекватных оценок производительности ВС разной архитектуры, а также в качестве функционального узла системы автоматизированного проектирования ВС. Цель изобретения - расширение области применения и повышение достоверности. Устройство содержит первый блок памяти (исходной программы), второй блок памяти (интерпретированной программы), третий блок памяти (виртуальных адресов), четвертый блок памяти (базовых адресов), пятый блок памяти (формул-условий), блок задания режима, первый регистр (команд), второй регистр (условий), сумматор,четвертый счетчик (адресов систем формул-условий), пятый счетчик (блокировки), первый счетчик (адресов исходной программы), второй счетчик (адресов интерпретированной программы), третий Счетчик (числа формул), блок индикации, блок задания условий, мультиплексор, первый, второй и третий коммутаторы, первый - девятый элементы И. Новыми элементами в устройстве являются второй, третий, четвертый, пятый блоки памяти, первый и второй регистры, второй, третий, четвертый, пятый счетчики, мультиплексор, второй и третий коммутаторы, второй - девятый элементы И. 5 ил. (Л С

&г.1

блок задания успоВий

5П1

Ф

КОП 0

КОП 1

,

КОП К А-.

/7 Я+1

NOP

16

С - Я,

.f-ft.n

N7

На мил л Фиг,3

ВП2

5ПЗ

Риг.4

/ Режим

2 Режим

Фиг.5

| Устройство для контроля времени выполнения программ | 1979 |

|

SU928360A1 |

| Авторское свидетельство СССР № 1634018, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1990-02-20—Подача