(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преоб разователей. Известен преобразователь двоично кода в двоично-десятичный код граду сов и минут, содержащий блок элемен тов И; первая группа входов которог сйединена с выходными информационным шинами, вторая группа входов соединена с выходами распределителя импульсов, вход которого соединен с выходом элемента И, первый вход эле .мёнта И, соединен с шинйй подачи та товых импульсов ГЛ. , Наиболее .близким по технической сущности к предлагаемому является преобразователь двоичного кода в двоично-десятичный код, содержащий группу элементов И, первые входы которых соединены с информационным Входами преобразователя, распределитель импульсов , шифратбр, накопительный сумматор, выходы которого являются информационными ВЫХОДс1МИ преобразователя, а входы соединены выходами шифратора, входы которого соединены с выходами элементов И группы, вторые входы которых соединены с соответствующими выходами распределителя импульсов, установоч ный вход распределителя импульсов является входом начальной установки, преобразователя С2}. Недостаток известных устройств отсутствие возможности преобразования двоичного кода в двоично-десятичный код градусов и глинут. Цель изобретения - расширение функциональных возможностей, заклю-. чающееся в обеспечении возможности преобразования двоичного кода как в двоично-десятичный, так и в двоичнодбсятично-шестидесятиричйый код. Поставленная цель достигаетсятем, что в преобразователь двоичного кода в двоично-десятичный код, содержащий группу элементов И, первые входы которых соединены с информационными входами преобразователя, распределитель импульсов, шифратор, накапливающий сумматор, выходы которого . являются информационными выходами преобразователя; а входы соединены соответственно с выходами шифратора, входыкоторого соединены соответственно с.выходами элементов И группы, вторые входы которых соединены с соответствующими входами распределителя импульсов, установочный вход распределителя импульсов является входом начальной установки преобразователя, введен элемейт И, а накапливающий сумматор содержит последовательно соединенные комбинационный двоично-десятичный сумматор и комбинационный двоично-шестиричный сумматор, и группу последовательно соединенных комбинационных двоично-десятичных сумматоров, коммутатор и регистр, Информационные входы которого соединены с выходами комбинационных двоично-десятичных сумматоров и выходом комбинационного двоично-шестиричного сумматора, тактовый вход регистра соединен с выходом элемента И и тактовым входом распределителя импульсов, вход сброса регистра соединен- с входом начальной установки преобразователя, а выходы регистра соединены с входами комбинационных двоично-десятичных сумматоров и входом комбинационного двоично-шестиричного сумматора, выходы переполнения первого комбинационного двоично-десятичного сумматора и двоичношестиричного сумматора соединены с информационными входами коммутатора,

.управляющий вход которого соединен с управляющими, входами шифратора и преобразователя, а выход коммутатора соединен с входом переполнения второго комбинационного двоично-десятичного сумматора, последний выход распределителя импульсов соединен с

первым входом элемента И, второй вход которого является тактовым входом преобразователя.

На чертеже представлена блок-схема предлагаемого преобразователя,

Преобразователь содержит информационный вход 1, управляющий вход 2, тактовый вход 3, вход 4 начальной установки , группу элементов И 5, шифратор 6, элемент И 7,комбинационные двоично-десятичные сумматоры 8-1 комбинационный двоично-шестиричный сумматор 12, распределитель 13 импульсов, коммутатор 14, регистр 15, разряды которого разбиты на пять тетрад, информационные выходы 16, накапливающий сумматор 17.

Распределитель 13 импульсов имеет количество выходов на единицу.

-больше количества разрядов входного двоичного кода и может быть построен на базе сдвигового регистра или двоичного счетчика и дешифратора. Все

. выходы распределителя 13 импульсов, за исключением последнего,соединены с соответствующими входами группы элементов И 5. Шифратор 6 служит для формирования двоично-десятичных кодов весов разрядов преобразуемого кода...

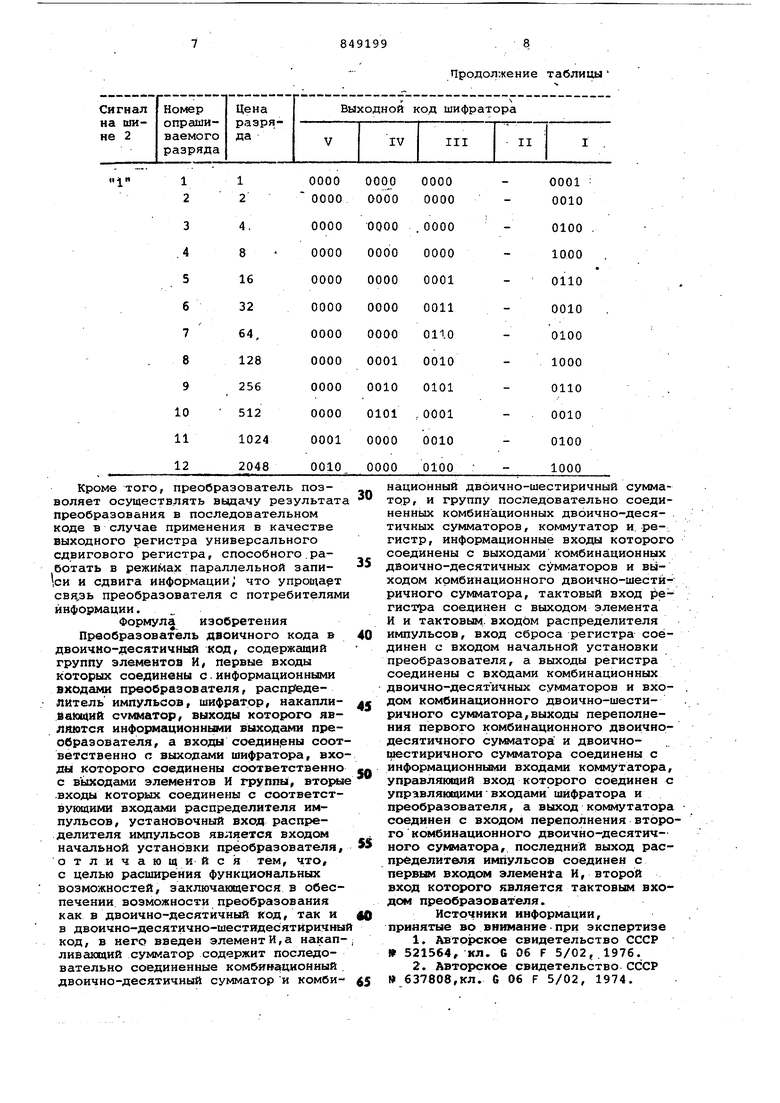

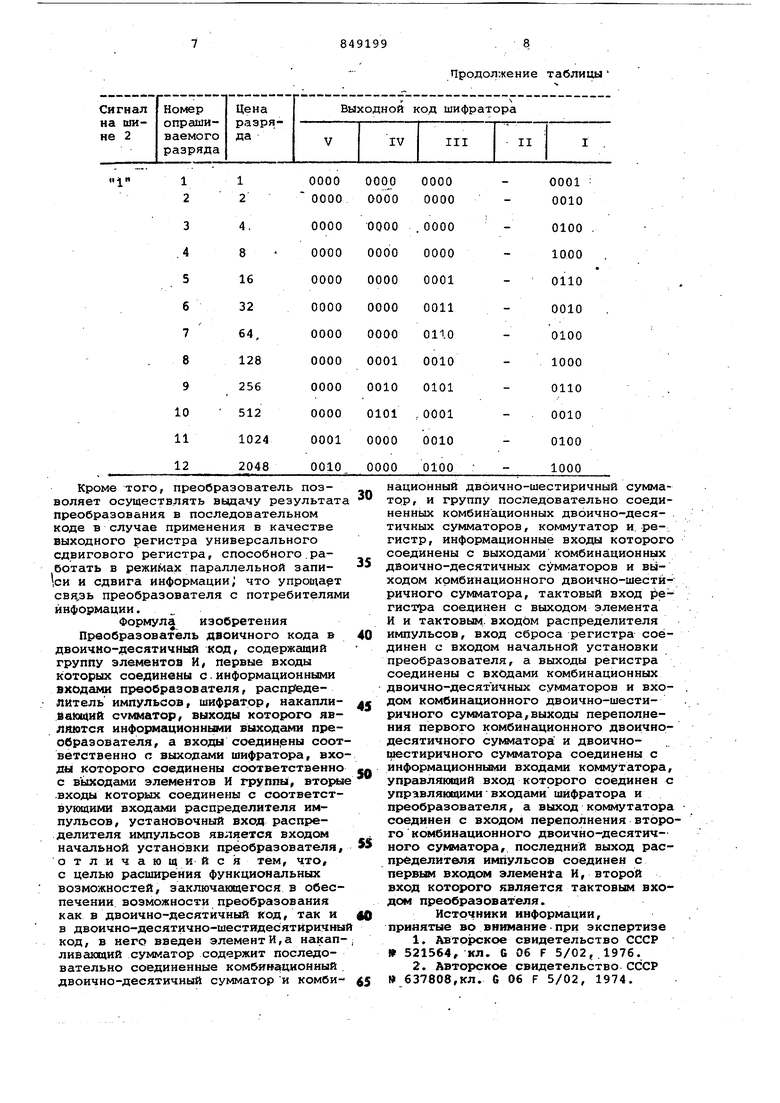

В таблице представлена зависимость выходных кодов шифратора, на выходах I -V от номера опрахииваемого.

разряда входного 12-разрядного двоичного кода при работе в режиме преобрайования двоичного кода в двоичнодесятичный код градусов и минут (на выходе 2 шифратора б:при этом поддерживается сигнал И) и при-работе в режиме преобразования двоичного кода в двоично-десятичный код (на входе 2 поддерживается сигнал 1).

Двоично-десятичные сумматоры 8-11, а также двоично-шестиричный сумматор 12 служит для суммирования выходных кодов шифратора 6 с содержимым тетрад регистра 15 на каждом такте преобразования. В случае преобразования двоичного кода в двоично-десятичный код градусов и минут сумматоры 8,12,9,10 и 11 производят суммирование двоично-десятичных кодо единиц минут, десятков минут, единиц десятков и сотен градусов соответственно. В случае преобразования двоичного кода в двоично-десятичный код числа сумматоры 8-11 производят суммирование- двоично-десятичных кодов .единиц, десятков, сотен и тысяч соответственно, а двоично-шестиричный сумматор 12 в работе преобразователя не участвует.

Двоично-десятичные сумматоры 8-11 являются комбинационными устройствами, выходной код которых выражается зависимостью

с - SAB. если SAB « 1001

Una + ОНО если S,

С76 1001,

ов

- выходной двоичной десятичгденый код,

Sjjg - двоичная сумма входных кодов сумматора.

Выходной код двоично-шестиричного сумматора 12, производящего суммирование десятков минут, выражается зависимостью.

101

, если Sjjg

ов

101

-f 010, SOB

если ов

Коммутатор 14 имеет два информационных входа и один управляющий вход При О на управляющем входе на. выход коммутатора проходит сигнал с выхода переноса двоично-шестиричного сумматора 12 и при 1 на управляющем входе - сигнал с выхода переноса двоично-десятичного сумматора 8, т.е. двоично-шестиричный сумматор 12 исключается из цепи суммирования.

Рассмотрим работу .преобразователя на примере преобразования 12-разрядного двоичного кода. /

На тактовый вход 3 поступает непрерывная последовательность, тактсэвых импульсов, одна1ко они не проходят через элемент И 7 до момента поступления импульса начальной установки на входную шину 4, который производит установку выходов распределителя 13 импульсов, связанных с элементом И 7 и с входом опроса первого разряда группы элементов 5 И, в состояние 1, а всех остальных выходов - в состояние О.. Одновременно производится установка в состояние О разрядов регистра 15. При появлении 1 на выходе распр делителя 13 импульсов, связанном с входом элемента И 7, последний начинает пропускать на свой выход тактовые импульсы. Каждый из импульсов производит запись в регистр 15 кода образовавшегося в результате суммирования кода с выходов шифратора 6 с кодом, хранящимся в регистре 15, и производит сдвиг 1 на следующий выход распределителя 13. Таким образом производится последовательный опрос.состояния всех разрядов входного- двоичного кода и суммирование их двоично-десятичных эквивалентов. После прохождения 12-го тактового импульса выход распределителя 13 импульсов , связанный со входом элемента И 7, сбрасывается в состояние и тем самым запрещается прохождение тактовых импульсов через элемент И 7. На этом цикл преобразования заканчивается. Двоично-десятичный код, полученный в результате преобразования, снимается с выходов регистра 15. Время преобразования кода преобразователем Можно выразить как t п - Т . где п - количество разрядов входного кода; Т - период следования тактовьк импульсов. Погрешность преобразования двоичного кода в двоично-десятичный у рассматриваемого преобразователя равна нулю, а погрешность преобразования двоичного кода в двоично-десятичный код градусов и минут колеблется от о56 до +112, т.е. Меньше величины дискрета входного кода( Предлагаемый преобразователь позщоляет значительно сократить количество оборудования в случае необходимости осуществления преобразова- ния как двоичных кодов угла в двоично-десятичные коды градусов и минут, так и двоичных кодов в двоично-десятичные коды , так как указанные преобразования выполняются одним устройстврм. Преимуществом предлагаемого преобразователя кода является также возможность применения в нем интегральных микросхем высокой степени интеграции - четырехразрядных двоичных сумматоров, четырехразрядных и восьмиразрядных универсальных регистров, то время как в известных устройствах микросхемы высокой степени интеграции не могут быть применены в связи со спецификой их построения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1167737A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов, минут, секунд | 1978 |

|

SU780000A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

3 4

5 6 7 8 9

10 11 12 Кроме того, преобразователь позволяет осуществлять вьадачу результат преобразования в последовательном коде в случае применения в качестве выходного регистра универсального сдвигового регистра, способного.работать в режимах параллельной запи1си и сдвига информации; что ynpouiagT свя,зь преобразователя с потребителям информации. Формула изобретения Преобразователь двоичного кода в двоично-десятичный код, содержащий группу элементов И, первые входы которых соединены с.информационными входа ш преобразователя, расп1 еделитель импульсов, шифратор, накаплиааю1Дий сумматор, выходы которого являются информационными выходами преобразователя, а входы соединены соот ветственно с выходами шифратора, вхо ды которого соединены соответственно с выходами элементов И группы, вторы .входы которых соединены с соответствующими входами распределителя импульсов, установочный вход распределителя импульсов является начальной установки преобразователя, отличающийся тем, что, с целью расшире ния функционгшьных возможностей, заключающегося в обеспечении возможности преобразования как в двоично-десятичный код, так и в двоично-десятично-шестйдесятйричны код, в него введен элемент И,а накапливающий сумматор содержит последовательно соединенные комбинационный двоично-десятичный сумматор и комбинационный двоично-шестиричный сумматоРг и группу последовательно соединенных комбинационных двоично-десятичных сумматоров, коммутатор и. регистр, информационные входы которого соединены с выходами комбинационных двоично-десятичных сумматоров и вь1ходом комбинационного двоично-шестиричного сумматора, тактовый вход регистра соединен с выходом элемента И и тактовым, входом распределителя импульсов, вход сброса регистра соединен с входом начальной установки преобразователя, а выходы регистра соединены с входами комбинационных двоично-десятичных сумматоров и входом комбинационного двоично-шестиричного сумматора,выходы переполнения первого комбинационного двоичнодесятичного сумматора и двоичношестиричного сумматора соединены с информационными входами коммутатора, управляющий вход которого соединен с управляющими входами шифратора и преобразователя, а выход коммутатора соединен с входом переполнения второго комбинационного двоично-десятичного сумматора, последний выход распр ёделитвля импульсов соединен с первым входом элемента И, второй вход которого является тактовым входом преобразователя. Источники информации, принятые во внимание - при экспертизе 1.ABToipCKOe свидетельство СССР 521564, кл. G 06 F 5/02,,1976. 2.Авторское свидетельство СССР 637808,кл. б 06 F 5/02, 1974.

Авторы

Даты

1981-07-23—Публикация

1979-11-16—Подача