Изобретение относится к устройствам автоматического управления и может быть использовано в системах программного управления.....,

Известен линейный интерполятор (Ратмиров В.А. Основы программного управления станками. - М., Машиностроение, 1978, стр. 121), построенный по методу оценочной функции, в котором блок расчета оценочной функции определяет величину отклонения от заданной траектории, после чего в зависимости от знака оценочной функции производится изменение одного или обоих выходных сигналов на фиксированную величину (шаг). Постоянство шага обуславливает независимость скорости компенсации отклонения от величины отклонения, что приводит к низкой динамической точности устройства.

Наиболее близким к предлагаемому яв- . ляется линейный интерполятор {Ратмиров В.А. Основы программного управления

станками.-М.,.Машиностроение. 1978, стр. 117), содержащий два блока перемножения (БП) и два интегратора, первый задающий вход интерполятора соединен с первым входом первого БП, выход которого подключен к входу первого интегратора, второй задающий вход интерполятора соединен с первым входом второго БП, выход которого подключен к входу второго интегратора, третий задающий вход интерполятора соединен с вторыми входами обоих БП, выход первого интегратора является первым информационным выходом интерполятора, а выход второго интерполятора - вторым информационным выходом интерполятора.

Недостатком указанного интерполятора является накопление ошибки интегрирования, вызванное ограниченной точностью используемых интеграторов и технологическим разбросом параметров элементов, что приводит к снижению точности задания траектории.

сл

с

««я

XI

со

кэ 4

СП

Целью изобретения является повышение точности задания траектории.

Для этого в линейный интерполятор, содержащий два блока перемножения и два интегратора, первый задающий вход интерполятора подключен к первому входу первого блока перемножения, второй задающий вход интерполятора подключен к первому входу второго блока перемножения, третий задающий вход интерполятора подключен к вторым входам первого и второго блоков перемножения, выход первого интегратора является первым информационным выходом линейного интерполятора, а выход второго интегратора является вторым информационным выходом, дополнительно введены четыре блока перемножения, сумматор, два блока сравнения и инвертирующий масштабный усилитель, выход первого блока перемножения соединен с суммирующим входом первого элемента сравнения, выход которого подключен к входу первого интегратора, первый вход третьего блока перемножения подключен к выходу первого интегратора, а его выход - к инвертирующему входу второго элемента сравнения, выход второго блока перемножения соединен с первым входом сумматора, выход которого соединен с входом второго интегратора, выход четвертого блока перемножения подключен к суммирующему входу второго элемента сравнения, выход которого через, инвертирующий масштабный усилитель соединен с первыми входа ми пятого и шестого блоков перемножения, выход пятого блока перемножения подключен к инвертирующему входу первого элемента сравнения, а выход шестого блока перемножения подключен к второму входу сумматора, первый вход четвертого блока перемножения соединен с выходом второго интегратора, первый задающий вход интерполятора соединен с вторыми входами четвертого и шестого блоков перемножения, а второй задающий вход интерполятора соединен с вторыми входами третьего и пятого блоков перемножения.

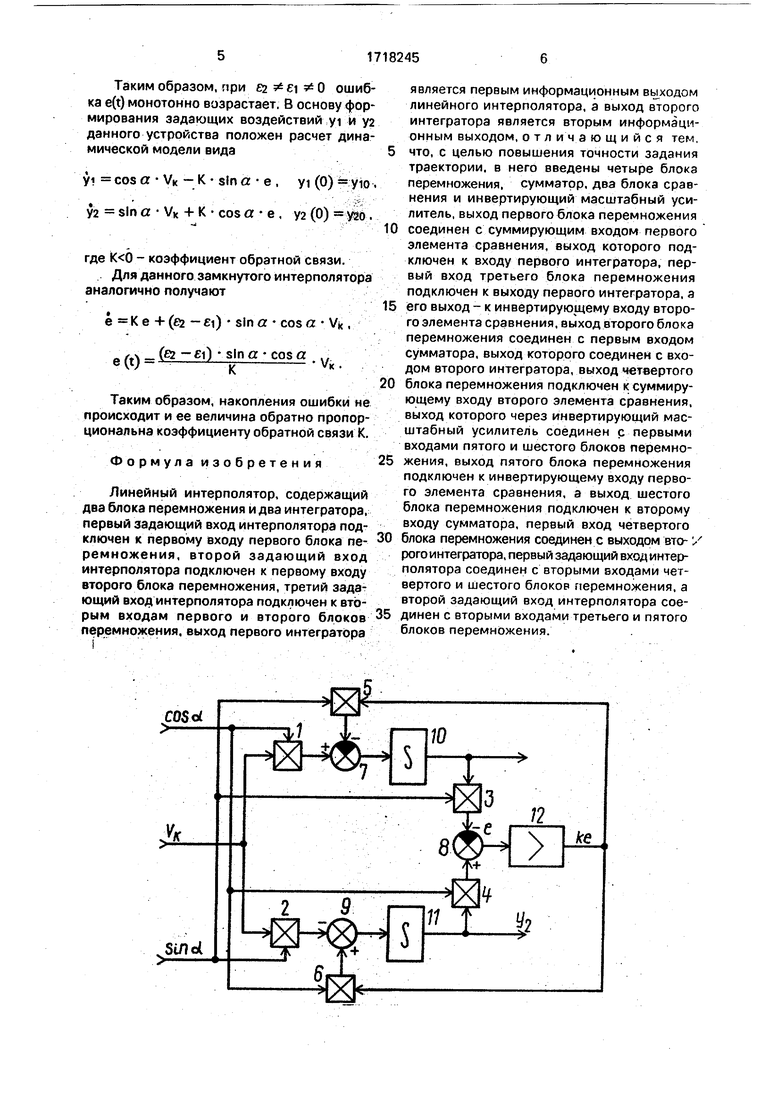

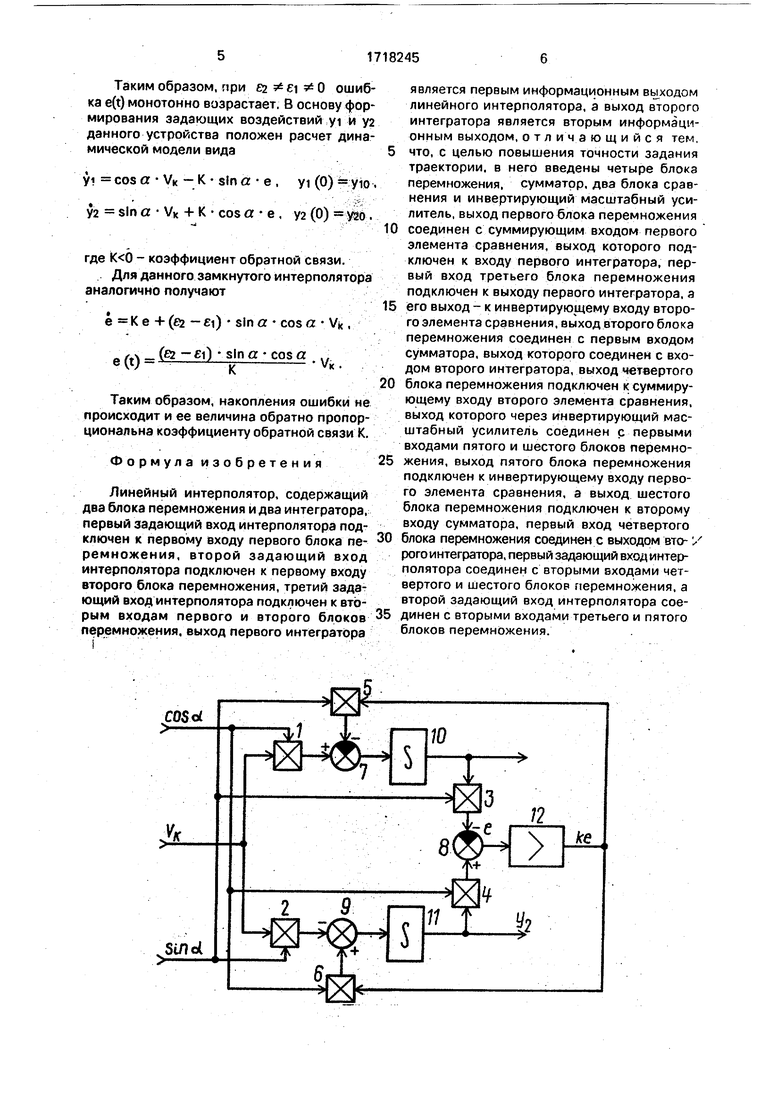

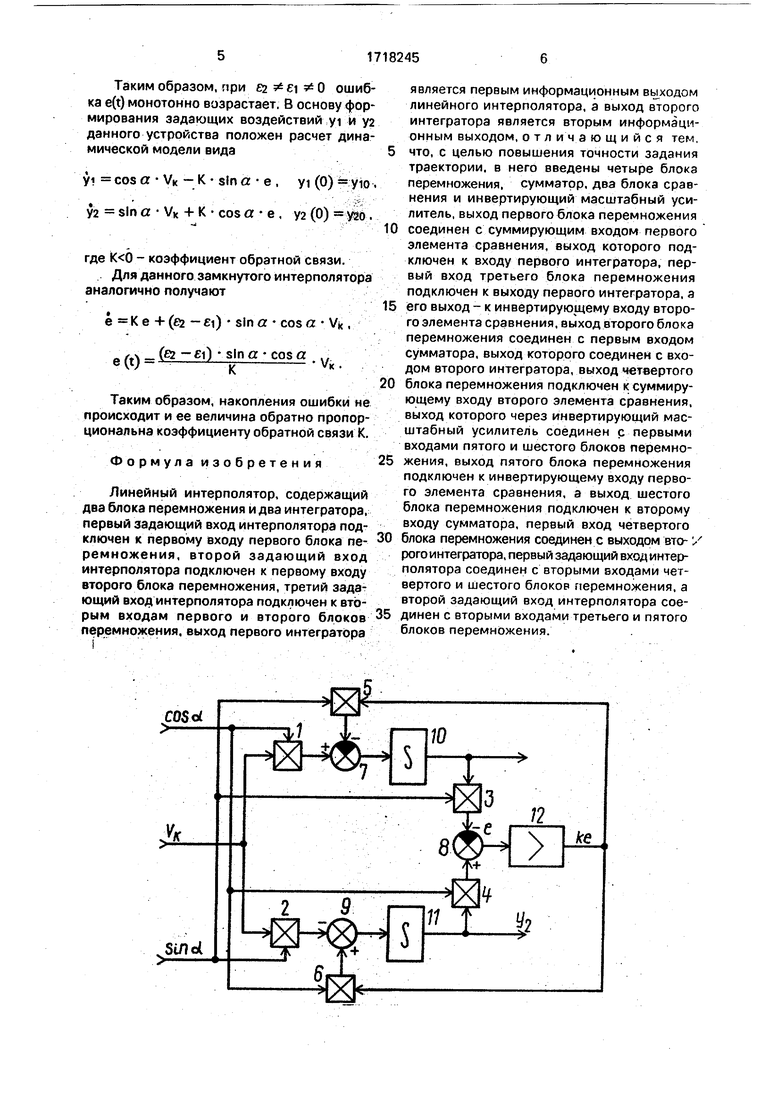

На чертеже изображен предлагаемый интерполятор.

Интерполятор содержит первый, второй, ..., шестой блоки перемножения {БП) 1-6, первый и второй элементы сравнения (ЭС) 7 и 8, сумматор 9, первый и второй интеграторы ТО и 11 и инвертирующий масштабный усилитель 12.

Первый задающий вход интерполятора соединен с первыми входами БП 1, 4 и б, второй задающий вход интерполятора - с первыми входами БП 2 3 и б, а третий задающий вход интерполятора - с вторыми входами БП 1 и 2. Выход первого БП 1 связан с суммирующим входом первого ЭС 7, инвертирующий вход которого подключен к выходу БП5. Выход БП 2 соединен с первым

входом сумматора 9, второй вход которого подключен к выходу БП 6. Выход ЭС 7 соединен с входом первого интегратора 10, подключенного выходом к второму входу БП 3. Выход сумматора 9 соединен с входом

второго интегратора 11, подключенного выходом к второму входу БП 4. Выход БП 3 соединен с инвертирующим входом ЭС 8, суммирующий вход которого связан с выходом БП 4. Выход ЭС 8 через инвертирующий

масштабный усилитель 12 соединен с вторыми входами БП 5 и 6. Выход интегратора 10 является первым информационным выходом линейного интерполятора, а выход интегратора 11 - вторым информационным

выходом линейного интерполятора. При этом на Первый и второй задающие входы интерполятора подаются сигналы cos а и sin а в соответствии с уравнением реализуемой траектории.

- sin а yi+COS а у2 0 ,

где yi и у2 - выходные сигналы интерполятора,

а на третий задающий вход интерполятора подается сигнал контурной скорости Vk.

Уравнение разомкнутого интерполятора (прототипа) с учетом ошибок практической реализации записывают в виде

yi (1 + d) cos a VK,

У2 (1 + Ј2) sin а VK.

где Ј1, Ј2 - малые постоянные.

Источниками подобных ошибок любого реального непрерывного интегратора являются ограниченность коэффициента усиления операционного усилителя, на котором реализован интегратор, дрейф нуля на его входе, наличие сигнальных помех. Основной источник подобных ошибок цифрового интегратора - ограниченная точность реги-- стров, связанная с ограничением разрядной сетки ЭВМ.

Тогда динамика отклонения описывается уравнением

е (Ј2 - Ј1) sin a cos a VK, е (t) (Ј2 - Ј1) sin a cos a V t.

Таким образом, при Ј2 е # 0 ошибка e(t) монотонно возрастает. В основу формирования задающих воздействий yi и у2 данного устройства положен расчет динамической модели вида5

yi coscr VK -К- sin а е . У1(0)%ую, У2 sin а VK + К cos а е , уз (0) yio.

10

где - коэффициент обратной связи.

Для данного замкнутого интерполятора аналогично получают

е .К е -f (ez - Јi) sin a cos a VK ,

Р/тч-(€2-Ј0 -sing-cos a .., е (i) - -. VK .

Таким образом, накопления ошибки не происходит и ее величина обратно пропорциональна коэффициенту обратной связи К.

Формул а изобретения

Линейный интерполятор, содержащий два блока перемножения и два интегратора, первый задающий вход интерполятора подключен к первому входу первого блока пе- ремножения, второй задающий вход интерполятора подключен к первому входу второго блока перемножения, третий задающий вход интерполятора подключен к вторым входам первого и второго блоковперемножения, выход первого интегратора i . . : -

5

10

15

20

25

0 5 :

является первым информационным выходом линейного интерполятора, а выход второго интегратора является вторым информационным выходом, о т л и ч а ю щ и и с я тем, что, с целью повышения точности задания траектории, в него введены четыре блока перемножения, сумматор, два блока сравнения и инвертирующий масштабный усилитель, выход первого блока перемножения соединен с суммирующим входом первого элемента сравнения, выход которого подключен к входу первого интегратора, первый вход третьего блока перемножения подключен к выходу первого интегратора, а его выход - к инвертирующему входу второго элемента сравнения, выход второго блока перемножения соединен с первым входом сумматора, выход которого соединен с входом второго интегратора, выход четвертого блока перемножения подключен к суммирующему входу второго элемента сравнения, выход которого через инвертирующий масштабный усилитель соединен с первыми входами пятого и шестого блоков перемножения, выход пятого блока перемножения подключен к инвертирующему входу первого элемента сравнения, а выход шестого блока перемножения подключен к второму входу сумматора, первый вход четвертого блока перемножения соединен с выходом вто- / рого интегратора, первый задающий вход интер- полятора соединен с вторыми входами четвертого и шестого блоков перемножения, а второй задающий вход интерполятора соединен с вторыми входами третьего и пятого блоков перемножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Круговой интерполятор | 1989 |

|

SU1700567A1 |

| Устройство для измерения мощности многофазной сети | 1984 |

|

SU1239617A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ БОКОВЫМ ДВИЖЕНИЕМ САМОЛЕТА ПРИ ЗАХОДЕ НА ПОСАДКУ | 2017 |

|

RU2662576C1 |

| Устройство для моделирования удара тела о неподвижную преграду | 1985 |

|

SU1381341A1 |

| Способ калибровки синфазно-квадратурного преобразователя | 1989 |

|

SU1677682A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2568315C1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Интерполятор для измерительных преобразователей перемещения | 1978 |

|

SU748445A1 |

| Устройство для задания программы в полярных координатах | 1986 |

|

SU1396125A1 |

| Цифровой измеритель мощности переменного тока | 1988 |

|

SU1511702A1 |

Изобретение относится к устройствам автоматического управления и может быть использовано в системах программного управления движением. Целью изобретения является повышение точности задания траектории. Поставленная цель достигается использованием значения оценочной функции для пропорциональной коррекции скоростей изменения выходных сигналов интерполятора. 1 ил.

С0$о

| Ратмиров В.А | |||

| Основы программного управления станками | |||

| М.: Машиностроение, 1978, с | |||

| Ребристый каток | 1922 |

|

SU121A1 |

| . | |||

| Там же.с | |||

| Аппарат для испытания прессованных хлебопекарных дрожжей | 1921 |

|

SU117A1 |

Авторы

Даты

1992-03-07—Публикация

1989-08-07—Подача