Известны устройства умножения, содержащие регистры множимого и множителя, схемы сдвига и схему анализа на нуль содержимого регистра множителя.

Предлагаемое устройство отличается от известных тем, что оно содержит суммирующее устройство, нулевые выходы приемного регистра которого соединены со входом соответствующего дифференцирующего элемента. Выход этого элемента соединен со входами схем «И», вторые входы которых связаны со схемой управления. При этом выход одной схемы «И» связан со входом схемы «ИЛИ», выход которой соединен со счетным входом триггера старшего разряда приемного регистра. Выход другой схемы «И» связан со входом схемы «ИЛИ», выход которой соединен со счетным входом триггера старшего разряда сумматора.

Это позволяет повысить быстродействие предлагаемой схемы.

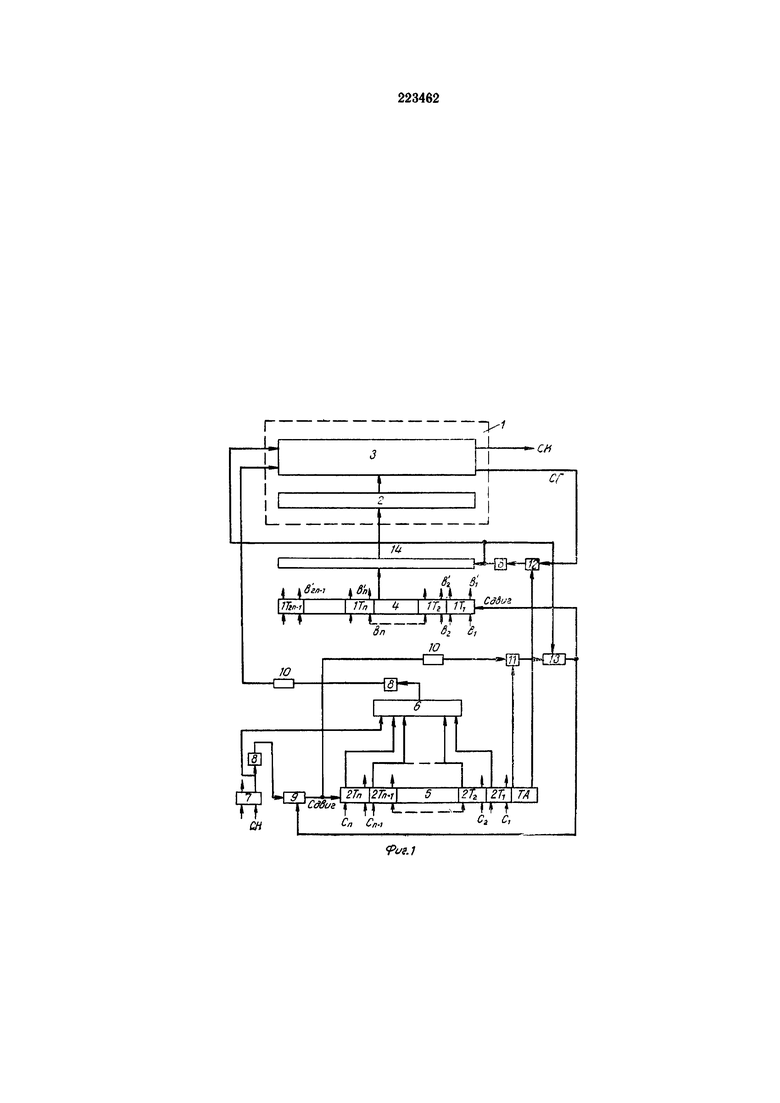

На фиг. 1 приведена принципиальная схема предлагаемого устройства умножения; на фиг. 2 - схема суммирующего устройства.

Принципиальная схема содержит суммирующее устройство 1, состоящее из приемного 2 и суммирующего 3 регистров, регистры множимого 4 и множителя 5, многовходовую схему «И» 6 для анализа на нуль содержимого регистра множителя, триггер 7 для приема сигнала начала работы, единичный выход которого через дифференцирующий элемент 8 и схему «ИЛИ» 9 управляет пуском всего устройства, линии задержки 10, схемы «И» 11 и 12, схему «ИЛИ» 13 и вентильную сборку 14.

Схема суммирующего устройства состоит из приемного регистра на триггерах 15, суммирующего регистра на триггерах 16, схемы сквозного переноса, включающей в себя элементы «И» 17 и «ИЛИ» 18, схемы управления на триггерах,19, 20 и 21 и элементах «И» 22, 23 и «ИЛИ» 24. При этом счетные входы триггеров 15 приемного регистра соединены с выходами схем «ИЛИ» 25, входы которых связаны с выходами триггеров 16 суммирующего регистра через схемы «И» 26, а также с нулевыми выходами триггеров 15 приемного регистра через дифференцирующие элементы 27 и схемы «И» 28. Единичные выходы триггеров 15 связаны со счетными входами триггеров 16 суммирующего регистра через схемы «И» 29 и схемы «ИЛИ» 30. На выходе устройства включены вентильные сборки 31 и 32.

В исходном положении все триггеры находятся в нулевом состоянии. До начала работы устройства необходимо подать множимое на входы регистра множимого 4, множитель - на входы регистра множителя 5 и сигнал начала работы СН - на вход записи «Единицы» триггера 7. При переходе триггера 7 в состояние I на один из входов многовходовой схемы «И» 6 подается высокий потенциал и снимается блокировка. При этом на выходе дифференцирующего элемента 8 образуется сигнал, поступающий на схему сдвига содержимого регистра множителя 5 на один разряд вправо и одновременно на вход линии задержки 10. В результате сдвига содержимое крайнего правого разряда регистра множителя 5 поступает в триггер ТА и в зависимости от состояния этого триггера «0» или «I» поступает на входы схем «И» 11 или 12 в случае «0» на выходе триггера ТА через элемент «ИЛИ» 13 на схему сдвига содержимого регистров множимого 4 и множителя 5. В случае «I» на выходе триггера ТА высокий уровень через схему «И» 12 и дифференцирующий элемент 8 подается на вентильную сборку 14 и передает содержимое регистра множимого 4 на приемный регистр 2 суммирующего устройства 1 при наличии на втором входе схемы «И» 12 высокого уровня сигнала готовности СГ суммирующего устройства принять очередное слагаемое, а также через элемент «ИЛИ» 13 поступает на схему сдвига регистра множимого 4 и через элемент «ИЛИ» 9 - на схему сдвига регистра множителя 5 и на вход линии задержки 10.

В исходном состоянии на выходе элемента «ИЛИ» 24 схемы управления суммирующим устройством поддерживается высокий уровень, так как триггеры 19 и 20 находятся в «0». При поступлении очередного слагаемого на приемный регистр 2 на счетный вход триггера 19 поступает сигнал. В результате на триггерах 19 и 20, образующих счетчик управления, будет записана комбинация «0-1» при поступлении первого слагаемого, «1-0 - при поступлении второго слагаемого и «1-1» при поступлении третьего. Высокий потенциал с нулевого выхода триггера 19 откроет вентильную сборку, образованную элементами «И» 28 и конъюнкция двух слагаемых, поступивших в приемный регистр 2, образованная на выходах дифференцирующих элементов 27, запомнится в суммирующем регистре 3 на триггерах 16 со сдвигом на один разряд влево, а в приемном регистре 2 на триггерах 15 запомнится сумма по «модулю два» поступивших слагаемых. Так как сигнал СГ имеет высокий уровень, на приемный регистр 2 поступает третье слагаемое и образует новую сумму по «модулю два», которая запомнится в приемном регистре, а на дифференцирующих элементах 27 образуется конъюнкция, которая со сдвигом на один разряд влево поступает на вентильную сборку элементов «И» 32, на вторые входы которых подан высокий потенциал с выхода схемы «И» 23. При этом на выходе дифференцирующего элемента 27, подключенного к выходу схемы «И» 23, образуется импульсный сигнал, поступающий на вход вентильной сборки, образованной элементами «И» 31, и на вход схемы «И» 22.

Так в суммирующем устройстве реализуются первые два шага операции «эквивалент сложения». Третий шаг реализуется группой элементов «ИЛИ» 25, на входы которых поступают конъюнкции с выходов вентильных сборок 31 и 32. Сигнал с выхода схемы «И» 22 устанавливает в «0» сумматор и триггер 19, одновременно дизъюнкция, образованная элементами «ИЛИ» 25, поступает в приемный регистр, где суммируется по «модулю два» с содержимым регистра, а на нулевых выходах триггеров 15 через дифференцирующие элементы 27 образуется конъюнкция, которая через вентильную сборку элементов «И» 28, открытую по второму входу высоким уровнем с триггера 19, записывается в сумматор со сдвигом влево на один разряд. Так реализуется первый шаг очередной операции «эквивалент сложения». При наличии к слагаемых устройство повторяет циклы (к-2) раз. При переходе триггера 21 в состояние I прекращается поступление последовательности слагаемых, импульс с единичного выхода триггера 21 через дифференцирующий элемент 27 поступает на вентильную сборку схемы 29 и на входы линий задержки. Затем содержимое приемного регистра передается в сумматор и суммируется с его содержимым, при этом включается схема сквозного переноса. Появление высокого сигнала СК на выходе линии задержки фиксирует конец работы сумматора.

Работа устройства заканчивается после того, как очередной сдвиг содержимого регистра множителя 5 приводит к появлению высокого уровня на выходе многовходовой схемы «И» 6, фиксирующей наличие нулей во всех разрядах регистра 5. При этом на выходе дифференцирующего элемента 8 образуется сигнал, поступающий через линию задержки 10 на вход суммирующего устройства, что является сигналом заключительного суммирования. Конец работы устройства умножения фиксирует высокий уровень сигнала конца работы СК на выходе суммирующего устройства. При этом окончательный результат - произведение расположено в суммирующем регистре 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

Устройство умножения, состоящее из регистров множимого и множителя, схем сдвига и схемы анализа на нуль содержимого регистра множителя, отличающееся тем, что, с целью повышения быстродействия, оно содержит суммирующее устройство, нулевые входы приемного регистра которого соединены со входом соответствующего дифференцирующего элемента, выход этого элемента соединен со входами схем «И», вторые входы которых связаны со схемой управления, при этом выход одной схемы «И» связан со входом схемы «ИЛИ», выход которой соединен со счетным входом триггера старшего разряда приемного регистра, выход другой схемы «И» связан со входом схемы «ИЛИ», выход которой соединен со счетным входом триггера старшего разряда сумматора, при этом единичные выходы триггеров приемного регистра связаны со входом соответствующей схемы «И», второй вход которой соединен со схемой управления, а выход - со входом схемы «ИЛИ», выход которой связан со счетным входом триггера данного разряда сумматора, нулевые выходы триггеров сумматора соединены со входом соответствующего дифференцирующего элемента, выход которого связан со схемой «И», второй вход которой соединен со схемой управления, а выход - со входом схемы «ИЛИ», второй вход которой связан со входом схем «И» цепи сквозного переноса, принадлежащего тому же разряду сумматора, а единичные выходы триггеров сумматора соединены со входами двух соответствующих схем «И», причем, второй вход одной схемы «И» связан со схемой управления, а выход - со входом элемента «ИЛИ», выход которого соединен со счетным входом триггера, принадлежащего тому же разряду приемного регистра, а второй элемент «И» схемы сквозного переноса соответствует данному разряду сумматора.

Авторы

Даты

1968-11-19—Публикация

1966-11-17—Подача