;vj

jlO

ioi iro

ю

i

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных цифровых вычислительных машин.

Известно устройство для возведения в квадрат, содержащее группу элементов И, накапливающий сумматор, разрядные входы которого соединены соответственно с выходами элементов И группы, сдви- говый регистр, выход i-ro разряда которого (i 1, N 2, где N - разрядность числа, возводимого в квадрат) соединен с первым входом i-ro элемента И группы, прямой выход (N-l)-ro разряда регистра сдвига соединен с первым входом N-ro элемента И группы, инверсный выход (N- 1)-го разряда регистра сдвига соединен с первым входом (N-1)-ro элемента И группы, вторые входы элементов И группы объединены и соединены с выходом N-ro разряда регистра сдвига, вход сдвига регистра соединен с входом записи накапливающего сумматора и тактовым входом устройства, информационный вход которого соединен с информационным входом регистра сдвига.

Недостатком данного устройства является то, что число, возводимое в квадрат, поступает на вход устройства младшими разрядами.

Наиболее близким по технической сущности и достигаемому эффекту к изобретению является устройство для возведения в квадрат, содержащее регистр аргумента, регистр результата, комбинационный счетчик, комбинационный сумматор, элемент И.

Сигналы сдвига в регистр аргумента поступают с входа устройства. С другого входа поступает число, возводимое в квадрат старшими разрядами вперед. При поступлении сигнала сдвига с входа в регистре суммы производится сдвиг на 2 разряда влево. Управление записью суммы в регистр осуществляется элементом И по сигналу, поступающему с входа устройства.

Выходы N-1 старших разрядов регистра аргумента соединены с первой группой входов комбинационного сумматора. Выход младшего разряда регистра аргумента 1 соединен с входом младшего разряда регистра результата. На вход второго разряда регистра результата постоянно подается нулевой сигнал, к входам остальных 2N-2 разрядов подключены выходы сумматора и комбинационного счетчика, а выходы 2N-2 разрядов соединены с входами сумматора и комбинационного счетчика. Выход переноса из сумматора соединен со счетным входом счетчика.

Недостатком данного технического решения является низкое быстродействие.

Цель изобретения - увеличение быстродействия, а также упрощение регистра результата.

Поставленная цель достигается тем, что в устройство для возведения в квадрат,

0 содержащее регистр аргумента, регистр суммы, комбинационный счетчик, входы тактовой частоты регистра аргумента и регистра результата объединены и являются тактовым входом устройства, выходы ком5 бинационного сумматора с 1-го по (М-2)-й соединены с информационными входами регистра результата со 2-го по (М-1)-й соответственно, первые N-1 выходов регистра результата являются выходами

0 устройства с 3-го по (N+ 1)-й разряд, выходы и входы разрядов с 1-го по (М-1)-й комбинационного счетчика соединены с входами и выходами, начиная с N-ro разряда регистра результата, дополнительно

5 введены N элементов И, причем первые входы с 2-го по N-й элементов И объединены и подключены к прямому выходу 1-го разряда регистра аргумента, инверсный выход которого соединен с первым вхо0 дом первого элемента И, выход которого соединен с первым информационным входом регистра результата, прямые выходы разрядов регистра аргумента с 3-го по N-й соединены с вторыми входами соответ5 ствующих элементов И, прямой выход 2-го разряда регистра аргумента одновременно соединен с вторыми входами 1-го и 2-го элементов И и. является выходом первого разряда устройства, выходы элементов И с 4-го

0 по N-й соединены с первыми входами с 2-го по (М-2)-й разрядов комбинационного сумматора, выходы 2-го и 3-го элементов И соединены с 1-м и 2-м входами 1-го разряда комбинационного сумматора, выходы реги5 стра суммы с 1-го по (N-1) - с вторыми входами разрядов с 2-го по (N-2)-ft комбинационного сумматора, выход переноса которого соединен с информационным входом (2N-1) разряда регистра результата, вы0 ход которого соединен со счетным входом комбинационного счетчика, выходы которого являются выходами устройства с (N+2)-ro по 2N-u разряды и выход устройства, соответствующий второму разряду, подсоеди5 нен к общей шине устройства.

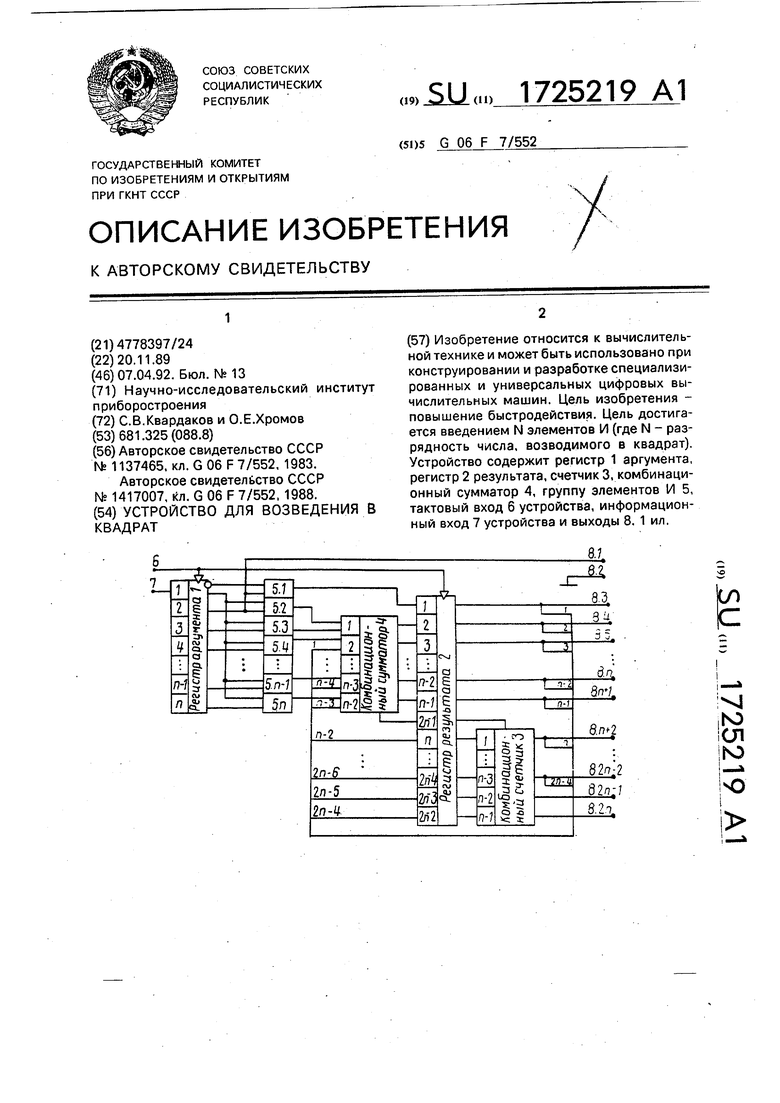

На чертеже изображена функциональная схема устройства.

Устройство для возведения в квадрат содержит регистр 1 аргумента, регистр 2 результата, комбинационный счетчик 3,

комбинационный сумматор 4, группу элементов И 5, тактовый вход 6, информационный вход 7, выходы 8.

Первые входы с второго по N-й элемента И 5 объединены и подключены к прямому выходу первого разряда регистра 1 аргумента, инверсный выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с первым информационным входом регистра 2 результата. Прямые выходы разрядов регистра 1 аргумента с 3-го по N-й соединены с вторыми входами соответствующих элементов И 5, прямой выход 2-го разряда регистра 1 аргумента одновременно соединен с вторыми входами 1-го и 2-го элементов И 5 и является выходом 1-го разряда устройства, выходы элементов И с 4-го по N-й соединены с первыми входами с 2-го по (N-2)-u разрядов комбинационного сумматора, выходы 2-го и 3-го элементов И соединены с 1-м и 2-м входами 1-го разряда комбинационного сумматора. Выходы регистра 2 результата с 1-го по ()-n разрядов соединены с вторыми входами разрядов с 2-го по (N-2)-u комбинационного сумматора 4, выход переноса сумматора 4 соединен с информационным входом (2N-1)-ro разряда регистра 2 результата, выход которого соединен со счетным входом комбинационного счетчика 3. Выходы комбинационного сумматора с 1-го по (N-2)-n соединены с информационными входами регистра 2 результата с 2-го по (М-1)-й соответственно. Первые N-1 выходов регистра 2 результата являются выходами устройства с 3-го по (Ы+1)-й разряд, выходы и входы разрядов с 1-го по (N-1)-u разряд комбинационного счетчика соединены с входами и выходами, начиная с N-ro разряда регистра 2 результата. Выходы комбинационного счетчика 3 также являются выходами устройства с (N+2)-ro по ( разряд. Выход устройства, соответствующий 2-му разряду, подсоединен к общей шине устройства. Тактовые входы регистра 1 аргумента и регистра 2 результата объединены.

Устройство работает следующим образом.

Для отыскания квадрата числа необходимо выполнить N циклов. В исходном состоянии сдвиговый регистр 2 и накапливающий сумматор 4 сброшены в О.

Первый цикл. На вход 7 устройства подается старший разряд Х1 числа, возводимого в квадрат, и на тактовый вход 6 подается сигнал С1. Разряд Х1 записывается в 1-й разряд сдвигового регистра 1. С выходов регистра 1 аргумента записанное

число поступает на входы элементов И 5. С первого элемента И 5 сигнал поступает на первый вход регистра 2 результата. С остальных выходов схем И 5 сигнал поступает

на входы комбинационного сумматора, складывается с числом, записанным в регистре 2 результата с 3-го по (М-1)-й разряд, и поступает на входы с 2-го по (Ы-1)-й регистра результата.

Второй цикл. На вход 7 подается второй разряд Х2 числа и на тактовый вход 6 сигнал С1. Полученный результат суммирования с выходов сумматора 4 и комбинационного счетчика 3, а также сигнал с выхода первого

элемента И 5 переписывается в регистр 2 результата. Разряд Х1 переписывается во 2-й разряд регистра 1 аргумента, Х2 записывается в первый разряд сдвигового регистра 1. Записанное число с выходов сдвигового

регистра 1 аргумента поступает на входы схем И 5. С 2-го по N-й выходы элементов И 5 сигнал поступает на входы сумматора, где складывается с числом, записанным в регистре 2 результата с 3-го по (N-1)-u разряд, и

поступает на входы со 2-го по (М-1)-й регистра 2 результата. С выхода 1 элемента И 5 сигнал поступает на первый информационный вход регистра 2 результата. С выхода 2N-1 регистра 2 результата на счетный вход

комбинационного счетчика 3 поступает сигнал переноса, который суммируется с содержимым регистра результата с N-ro по (2N-3)-u разряды и со сдвигом на два разряда влево поступает на входы с (N+2)-n по

(2Ы-2)-й регистра 2 результата.

Аналогичным образом выполняются и оставшиеся N-2 цикла. После завершения последнего (N-2)-ro цикла в регистре 2 результата будут записаны с 3-го по (N-H)-n

младшие разряды результата, а в комбинационном сумматоре - с (N+ 2)-го по 2N-n старшие разряды результата. Первый младший разряд берется с 2-го выхода регистра аргумента, а второй разряд всегда равен

Лог.О.

Технико-экономические преимущества. Время вычисления квадрата п-разрядного числа известным устройством равно

50 Т1 пхТц1,

(D

где Т1 - время вычисления известным устройством;

Тц1 - длительность одного цикла рабо- ты известного устройства.

Согласно описанию изобретения один цикл работы известного устройства равен двум тактам, поэтому

Т1 2 х п хТт1,

(2)

где Тт1 - длительность одного такта работы известного устройства.

За один такт в известном устройстве должен распространиться сигнал переноса от младшего разряда комбинационного сумматора 4 до старшего разряда комбинационного счетчика 3, а затем результат сложения должен быть записан в регистр. Поэтому Т1 можно вычислить по формуле

Тт1 (п-1)хТр + Тз,

гдеТр - время распространения переноса в одном разряде;

Тз - время записи в регистр.

Общая формула для Т1 принимает вид

Т1 4хпх (п-1)хТр + 2хпхТз.

В предлагаемом устройстве время вычисления квадрата n-разрядного числа равно

Т2 пхТц2,

где Т2 - время вычисления предлагаемым устройством;

Тц2 -длительность цикла предлагаемого устройства.

Поскольку у предлагаемого устройства один цикл состоит из одного такта, то

Т2 - пхТт2,

где Тт2 - длительность одного такта работы предлагаемого устройства.

В предлагаемом устройстве распространение сигнала переноса в комбинационном сумматоре 4 и комбинационном счетчике 3 происходит одновременно, поэтому длительность такта Тт2 равна

Тт2 (п-1)хТрхТз.(7)

Общая формула для Т2 имеет вид Тт2 пх(п-1)хТр + пхТз.(8)

Сравнение формул (4) и (8) показывает, что Т2 меньше Т1 по крайней мере в два раза. При увеличении п это отношение при

ближается к 4. Таким образом, быстродействие предлагаемого устройства в 2-4 раза больше известного.

5Ф о р м у л а и з о б р е т е н и я

Устройство для возведения в квадрат, содержащее регистр аргумента, информационный вход которого является информационным входом устройства, а тактовый

10 вход объединен с тактовым входом регистра результата и подключен к тактовому входу устройства, комбинационный сумматор, выходы которого с первого по (п-2)-й соединены с информационными входами разрядов

15 регистра результата с второго по (п-1)-й соответственно, разрядные выходы с первого по (п-1)-й которого являются разрядными выходами устройства с третьего по (п+1)-й соответственно, выходы и входы разрядов с

20 первого по (п-1)-й счетчиков соединены соответственно с входами и выходами разрядов с п-го по (2п-2)-й регистра результата, отличающееся тем, что, с целью повышения быстродействия, в него введены

25 N элементов И, причем первые входы с второго по N-й элементов И объединены и подключены к прямому выходу первого разряда регистра аргумента, инверсный выход которого соединен с первым входом первого

30 элемента И, выход которого соединен с информационным входом первого разряда регистра результата, прямой выход второго разряда регистра аргумента соединен с вторыми входами первого и второго элементов

35 И и является первым разрядным выходом устройства, прямые выходы разрядов регистра аргумента с третьего по N-й соединены с вторыми входами одноименных элементов И, выходы второго и третьего элементов И

40 соединены с первым и вторым входами первого разряда комбинационного сумматора, первые входы разрядов с второго по (М-2)-й которого подключены к выходам элементов И с четвертого по N-й, а вторые входы - к

45 выходам разрядов с первого по (N-1)-u регистра результата, вход и выход (2п-1)-го разряда которого соединен соответственно с выходом переноса комбинационного сум- маторэ и счетным входом счетчика, выходы

50 которого являются разрядными выходами с (N+2)-ro по 2М-й устройства, выход второго разряда устройства подключен к общей шине устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Процессор аппроксимационной обработки информации | 1988 |

|

SU1501089A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1137465A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для вычисления функции вида F( @ )= @ | 1987 |

|

SU1418709A1 |

| Устройство для вычисления логарифма | 1979 |

|

SU783798A1 |

| Вычислительное устройство | 1984 |

|

SU1196856A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления гиперболических функций у = @ и у = с @ | 1990 |

|

SU1735845A1 |

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных цифровых вычислительных машин. Цель изобретения - повышение быстродействия. Цель достигается введением N элементов И (где N - разрядность числа, возводимого в квадрат). Устройство содержит регистр 1 аргумента, регистр 2 результата, счетчик 3, комбинационный сумматор 4, группу элементов И 5, тактовый вход 6 устройства, информационный вход 7 устройства и выходы 8. 1 ил.

| Устройство для возведения в квадрат | 1983 |

|

SU1137465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в квадрат | 1986 |

|

SU1417007A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-07—Публикация

1989-11-20—Подача