10

15

Изобретение относится к вычисли- гельной технике и может быть исполь- зЬвано в системах управления гибкими- и автомати зированными производствами, г технологическими процессами, в специализированных вычислительных устрой- с ТВ ах.

Цель изобретения - повышение быстродействия.

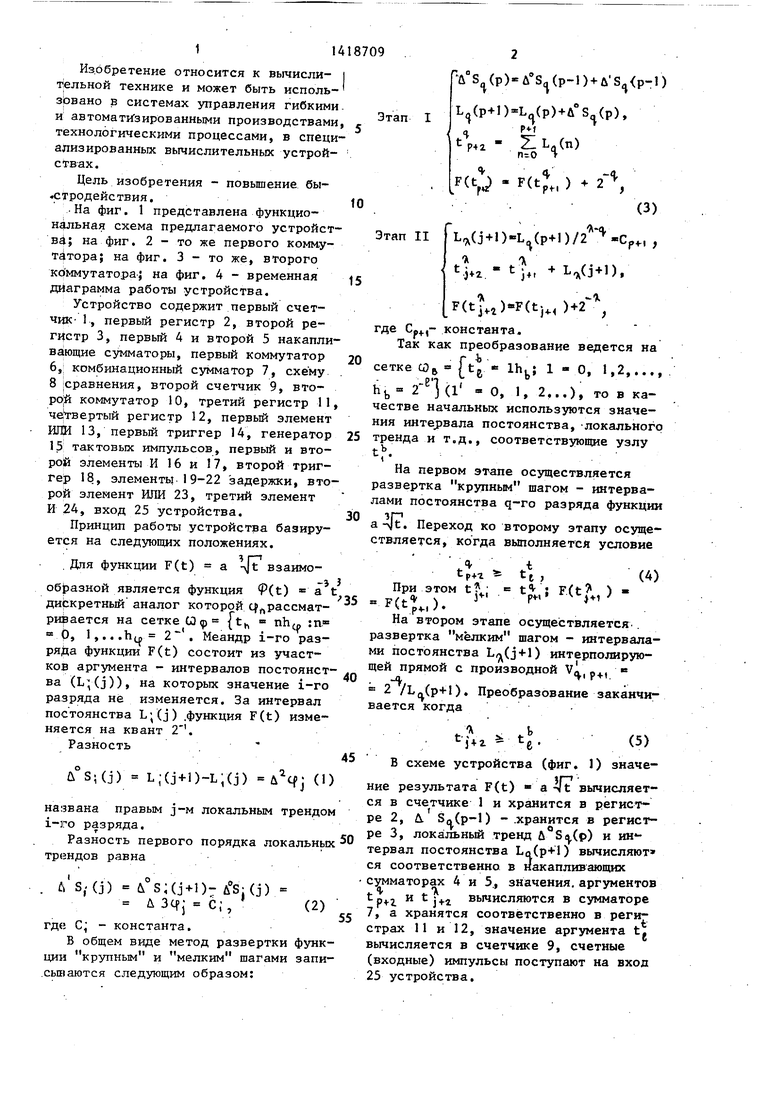

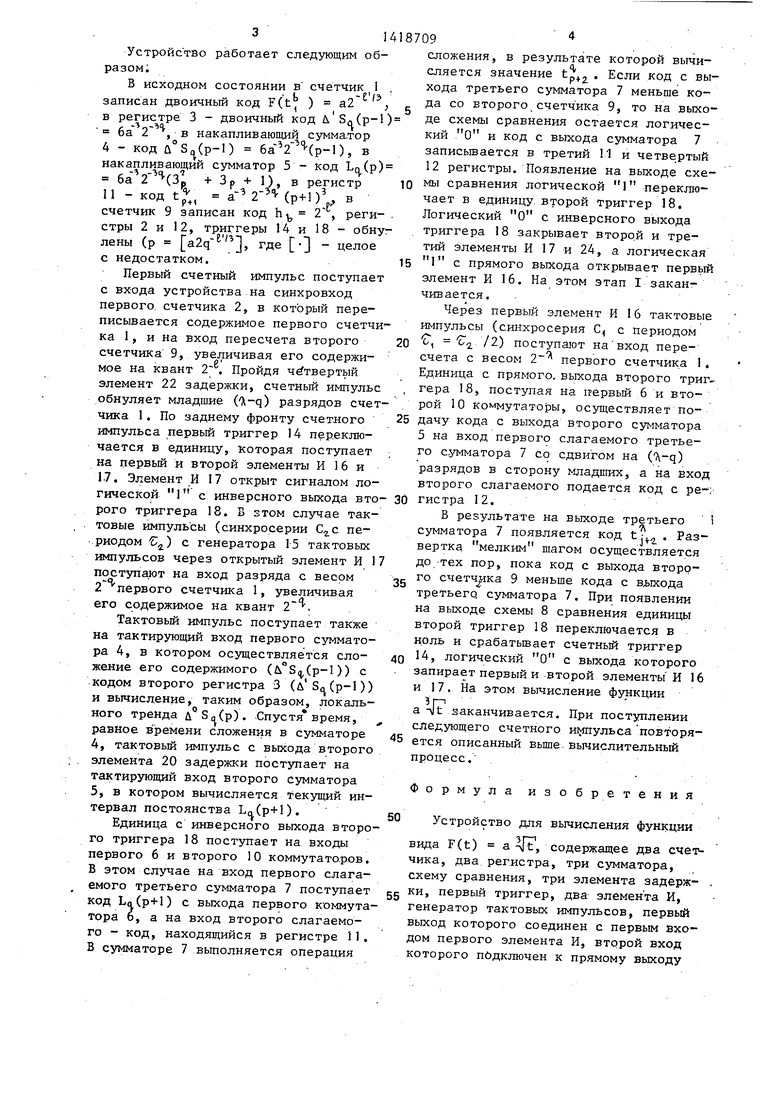

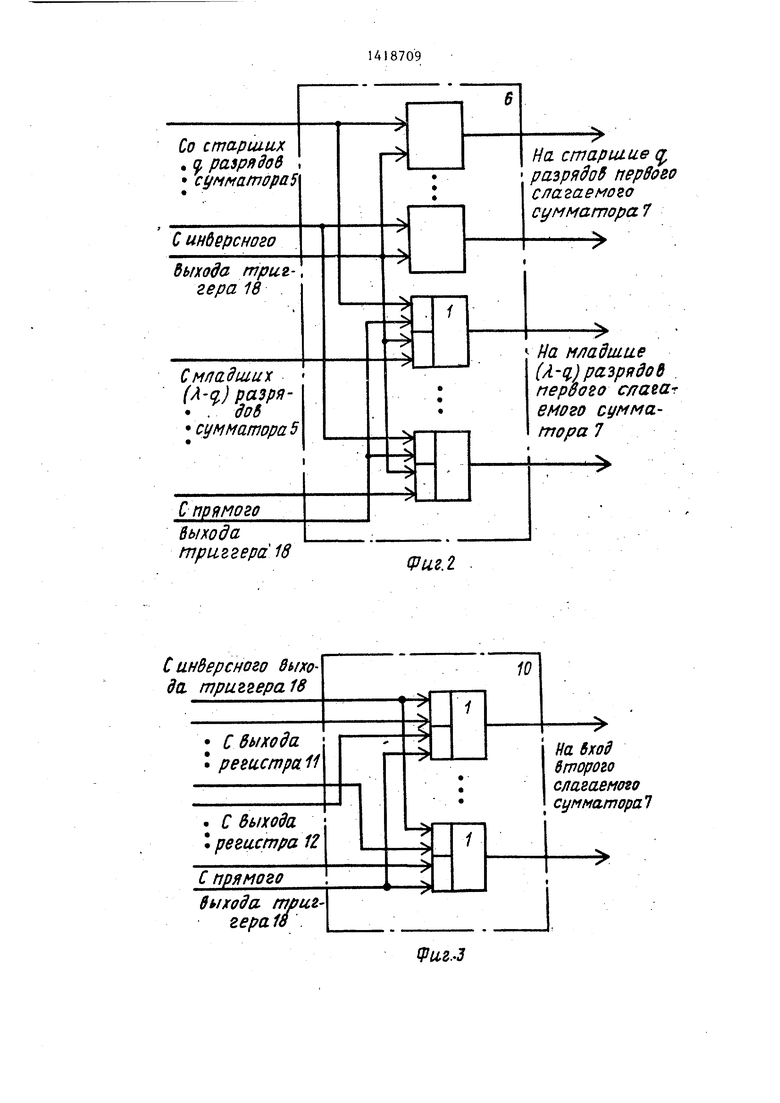

На фиг. 1 представлена функциональная схема предлагаемого устройст- Bi| на фиг. 2 - то же первого комму- тйтора; на фиг. 3 - то же, второго кр ммутатора; на фиг. 4 - временная диаграмма работы устройства.

Устройство содержит первый счетчик- 1, первый регистр 2, второй регистр 3, первый 4 и второй 5 накапливающие сумматоры, первый коммутатор 6, комбинационный сумматор 7, схему . 8 сравнения, второй счетчик 9, вто- ро|й коммутатор 10, третий регистр 11, четвертый регистр 12, первый элемент ИЛИ 13, первый триггер 14, генератор 15 тактовых импульсов, первый и второй элементы И 16 и 17, второй триггер 18, элементы 19-22 задержки, второй элемент ИЛИ 23, третий элемент И 24, вход 25 устройства.

Принцип работы устройства базируется на следующих положениях.

, Для функции F(t) а -Jt взаимо- образной является функция P(t)

20

25

а t

дискретный аналог которой с| рассмат- рибается на сетке СЭф (t nhq, :n« 0, l,...h(,, . Меандр i-го разряда функции F(t) состоит из участков аргумента - интервалов постоянства (L,(j)), на которых значение i-ro разряда не изменяется. За интервал постоянства L;(j) .функция F(t) изменяется на квант .

Разность .

u°s;(j) L;(J-H)-L;(J) (1)

35

40

45

Этап I

Vs(p)-u S(p-)-t-u S p-r) (p-H)L(p)- -u s(p),

Р+2

P«-f

т: LM

ПгО

ntj,.)

Этап II

2

,М

гЧ

(3)

L(j + I)-L(p+l)/2 -Ср, , t,, +L(j + l),

)г. F(tu,)F(tu, )+2

-г

j

где Ср,- константа.

Так как преобразование ведется на

сетке COft t

Ь

Ih,

1 - О, 1,2,...,

(1 0, 1, 2,..), то в качестве начальных используются значения интервала постоянства, локальног р тренда и т.д., соответствующие узлу

На первом этапе осуществляется развертка крупным шагом - интервалами постоянства q-го разряда функции

. Переход ко второму этапу осуществляется, когда выполняется условие

t J+ tt , (4) « При этом tf,; tp,; F(t, ) На втором этапе осуществляется . развертка мелким шагом - интервалами постоянства Ln(j+l) интерполирующей прямой с производной V, р,

2 /L-(p+l), Преобразование заканчивается когда

tj , t. (5)

В схеме устройства (фиг. 1) значе)Г

на;звана правым j-м локальным трендом i-Fo разряда.

трендов равна

ние результата F(t) «а вычисляется в счетчике 1 и хранится в регистре 2, U. SQ(P-I) - .хранится в регист г - - ре 3, локальный тренд и Sa(p) и ин Разность первого порядка локальньк Э тервал постоянства Ьа(р+1) вычисляют

ся соответственно в накаплив ающих сумматорах 4 и 5., значения, аргументов t и t j .4 вычисляются в сумматоре ее 7, а хранятся соответственно в регистрах 11 к 12, значение аргумента tj вычисляется в счетчике 9, счетные (входные) импульсы поступают на вход 25 устройства.

U s-(J) Л sXj+O- s-(j) л 3cf- с;,

(2)

где С - константа.

В общем виде метод развертки функции крупным и мелким шагами записью аются следующим образом:

Этап I

Vs(p)-u S(p-)-t-u S p-r) (p-H)L(p)- -u s(p),

Р+2

P«-f

т: LM

ПгО

ntj,.)

2

гЧ

(3)

Этап II

,М

L(j + I)-L(p+l)/2 -Ср, , t,, +L(j + l),

)г. F(tu,)F(tu, )+2

-г

j

где Ср,- константа.

Так как преобразование ведется на

сетке COft t

Ь

Ih,

1 - О, 1,2,...,

(1 0, 1, 2,..), то в качестве начальных используются значения интервала постоянства, локальног р тренда и т.д., соответствующие узлу

На первом этапе осуществляется развертка крупным шагом - интервалами постоянства q-го разряда функции

. Переход ко второму этапу осуществляется, когда выполняется условие

t J+ tt , (4) « При этом tf,; tp,; F(t, ) На втором этапе осуществляется . развертка мелким шагом - интервалами постоянства Ln(j+l) интерполирующей прямой с производной V, р,

2 /L-(p+l), Преобразование заканчивается когда

tj , t. (5)

В схеме устройства (фиг. 1) значе)Г

ние результата F(t) «а вычисляется в счетчике 1 и хранится в регистре 2, U. SQ(P-I) - .хранится в регистУстройство работает следующим образом;В

исходном состоянии в записан двоичный код F(t

счетчик 1 ) а2в регистре 3 - двоичный код t 8а(р-1), - о-н- ..

6а 2 ,

4 - код U

в накапливающий сумматор S,(p-l) (р-1), в

накапливающий сумматор 6а 2 (3р + Зр + 1) 11 -код tj;, а- 2- счетчик 9 записан код h

код bq,(p) регистр

- 2-(р+)-., в

)-t

регистры 2 и 12, триггеры 14 и 18 - обнуг лены (р a2q , где - целое с недостатком.

Первый счетный импульс поступает с входа устройства на синхровход первого счетчика 2, в который переписывается содержимое первого счетчика 1, и на вход пересчета второго счетчика 9, увеличивая его содержимое на квант 2 . Пройдя четвертый элемент 22 задержки, счетньй и тульс обнуляет младшие ( X-q) разрядов счетчика 1, По заднему фронту счетного импульса первый триггер 14 переключается в единицу, которая поступает на первый и второй элементы И 16 и 17. Элемент И 17 открыт сигналом логической 1 с инверсного выхода второго триггера 18. В зтом случае тактовые импульсы (синхросерии периодом С) с генератора 15 тактовых импульсов через открытый элемент И 17 поступают на вход разряда с весом

Q

2 первого счетчика 1, увеличивая его содержимое на квант 2.

Тактовый импульс поступает также на тактирующий вход первого сумматора 4, в котором осздцествляется сложение его содержимого (u°S(j,(p-l)) с кодом второго регистра 3 {u S((p-l)) и вычисление, таким образом, локального тренда u SflCp). Спустя время, равное в ремени сложения в сумматоре

4,тактовый импульс с выхода второго элемента 20 задержки поступает на тактирующий вход второго сумматора

5,в котором вычисляется текущий интервал постоянства Ln(p+I).

Единица с инверсного выхода второго триггера 18 поступает на входы первого 6 и второго 10 коммутаторов. В этом случае на вход первого слагаемого третьего сумматора 7 поступает код La(p+l) с выхода первого коммутатора 6, а на вход второго слагаемого - код, находящийся в регистре 11. В сумматоре 7 вьтолняется операция

)

10

г-

-;7

15

20

25

30

В результате которой вычи- значение tj, . Если код с высложения,

JT/i 6 ГС л. 3 iiici- io«A.jriv- nx

хода третьего сумматора / меньше кода со ВТОрого счетчика 9, то на выходе схемы сравнения остается логический О и код с выхода сз матора 7 записывается в третий 11 и четвертый 12 регистры. Появление на выходе схемы сравнения логической 1 переключает в единицу второй триггер 18. Логический О с инверсного выхода триггера 18 закрывает второй и третий элементы И 17 и 24, а логическая 1 с прямого выхода открывает первьгй элемент И 16. На этом этап I заканчивается. .

Через первый элемент И 16 тактовые импульсы (синхросерия С с периодом /2) поступают на вход пере Г - Г

о, - c/i

счета с весом первого счетчика I . Единица с прямого, выхода второго триггера 18, поступая на иервый 6 и второй 10 коммутаторы, осуществляет подачу кода с выхода второго сумматора 5 на вход первого слагаемого третьего сумматора 7 со сдвигом на (A-q) разрядов в сторону младших, а на вход второго слагаемого подается код с гистра 12.

В результате на выходе третьего сумматора 7 появляется код t.-. . Развертка мелким шагом осуществляется

5

0

5

0

до -тех пор, го счетчика

пока код с выхода вторр- 9 меньше кода с В4 1хода третьего, сумматора 7. При появлении на выходе схемы 8 сравнения единицы второй триггер 18 переключается в ноль и срабатьшает счетный триггер 14, логический О с выхода которого запирает первый и второй элементы И 16 и 17, На этом вычисление функции

Зр а -)t заканчивается. При поступлении

следующего счетного импульса повторяется описанный вьше вычислительный процесс.

Формула изобретения

Устройство для вычисления функции

вида F(t) а л|7, содержащее два счетчика, два регистра, три сумматора, схему сравнения, три элемента задерж- g ки, первый триггер, два элемен та И, генератор тактовых импульсов, первьй выход которого соединен с первым входом первого элемента И, второй вход которого подключен к прямому выходу

514

пефвого триггера, выход первого элемента И соединен с входом первого элемента задержки и с входом младшего разряда первого счетчика, разрядные вькоды которого подключены к информационным входам первого регистра, вход и вьпсод второго элемента задержки подключены соответственно к тактирующим входам первого и второго накапливающих сумматоров, разрядные вьЬсоды перового из которых соединены с информационными входами второго накапливающего сумматора, о.т л и - ч а ю щ е е. с я тем, что, с целью повьшення быстродействия, в него введены два коммутатора, третий и четвертый регистры, два элемента ИЛИ, .второй триггер, четвертьй элемент задержки, третий элемент И, а третий сумматор выполнен комбинационным, П1|ичем разрядные выходы второго реги- стгра соединены с информационными вхо- д4ми первого накапливающего суммато- р4з выход второго элемента И подключен к тактирующему входу первого накапливающего сумматора, к входу q-ro разряда первого счетчика и к входу третьего элемента задержки, выход которого соединен с синхровходом третьего регистра и первым входом тре- Т1)его элемента И, информационный вход устройства соединен с сихровхо- дом первого регистра, с первым входом первого элемента ИЛИ, с входом младшего разряда второго счетчика и через четвертый элемент задержки - с входом сброса младших -q разрядов первого счетчика, первый, второй и -.

96

третий входы второго элемента И соединены соответственно с.вторым выходом генератора тактовых импульсов, прямым выходом первого триггера и инверсным выходом второго триггера, подключенного к второму входу третьего элемента Ник первым управляющим входам первого и второго коммутаторов, вторые управляющие входы которых, второй вход первого элемента ИЛИ и третий вход первого элемента И подключены к прямому выходу второго триггера, вход которого соединен с

выходом схемы сравнения, первая и вторая группы входов которой соединены соответственно с разрядными выходами комбинационного сумNaтора и второго счетчика, выходы третьего и

четвертого регистров соединены с пер- вой и второй группами информационных входов второго коммутатора, выход которого и выход первого коммутатора подключены к одноименным входам слагаемых комбинационного сумматора, разрядные выходы которого подключены к информационным входам третьего и четвертого регистров, выход третьего элемента И соединен с первым входом

второго элемента ИЛИ, второй вход

и выход которого подключен соответственно к выходу первого элемента держки и синхровходу четвертого регистра, выход первого элемента ИЛИ сое35-динен с входом первого триггера, раз- рядны выходы второго накапливающего сумматора соединены с информационными входами первого коммутатора.

иг. З

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1987 |

|

SU1481750A1 |

| Функциональный преобразователь | 1988 |

|

SU1501021A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Формирователь кодов радиально-круговой развертки для индикатора кругового обзора | 1983 |

|

SU1185284A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

Изобретение относится к вычислительной технике и может быть использовано в .системах управления гибкими автоматизированными производствами, технологическими процессами в специализированных вычислительных устройствах. Цель изобретения - повьшение быстродействия. Изобретение позволяет в несколько десятков раз повысить ,. скорость извлечения корня третьей степени и реализует умножение резуль- тата на вещественный коэффициент. Повышение скорости преобразования достигается за счет декомпозиции алгоритма развертки на,два этапа. На первом этапе развертка ведется крупным шагом в некотором среднем q-м разряде и приращение функции осуществляется квантами На втором этапе ведемся развертка мелким шагом в младшем fj -м разряде, а приращение- функции реализуется квантами 2. Для достижения поставленной цели в устройство введены два коммутатора 6 и 10, -третий 11 и четвертый 12 регистры, .два элемента ШШ 13 и 23., второй триг- гер 18, четвертый элемент 22 задержки, третий элемент И 24. Дополнительно введенное оборудование позволяет осуществить переход к развертке мелким шагом путем сдвига в первом коммутаторе 6 значения длины интервала постоянства на ( Л-д) разрядов в сторону младших. После вычисления текус iS (/) щего значения функции F(t) а реализуется возврат к развертке ным шагом. 4 ил. круп4 И 00 о (

| Устройство для извлечения квадратного корня | 1980 |

|

SU949654A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения корня третьей степени | 1983 |

|

SU1129609A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-15—Подача