Изобретение относится к вычислительной технике и может быть использовано в .многомашинных вычислительных системах для повышения их надежности.. :: Целью изобретения является повыше ние надежности за счет аппаратного децентрализованного диагностирования в многомашинной вычислительной системе.

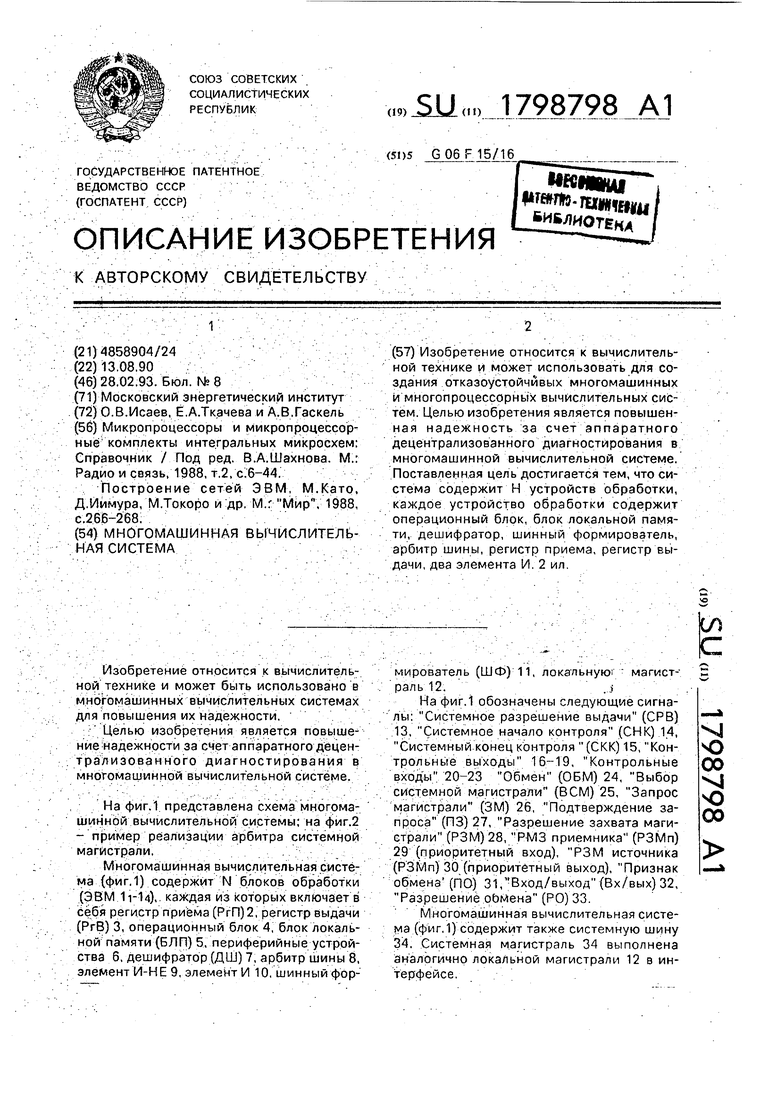

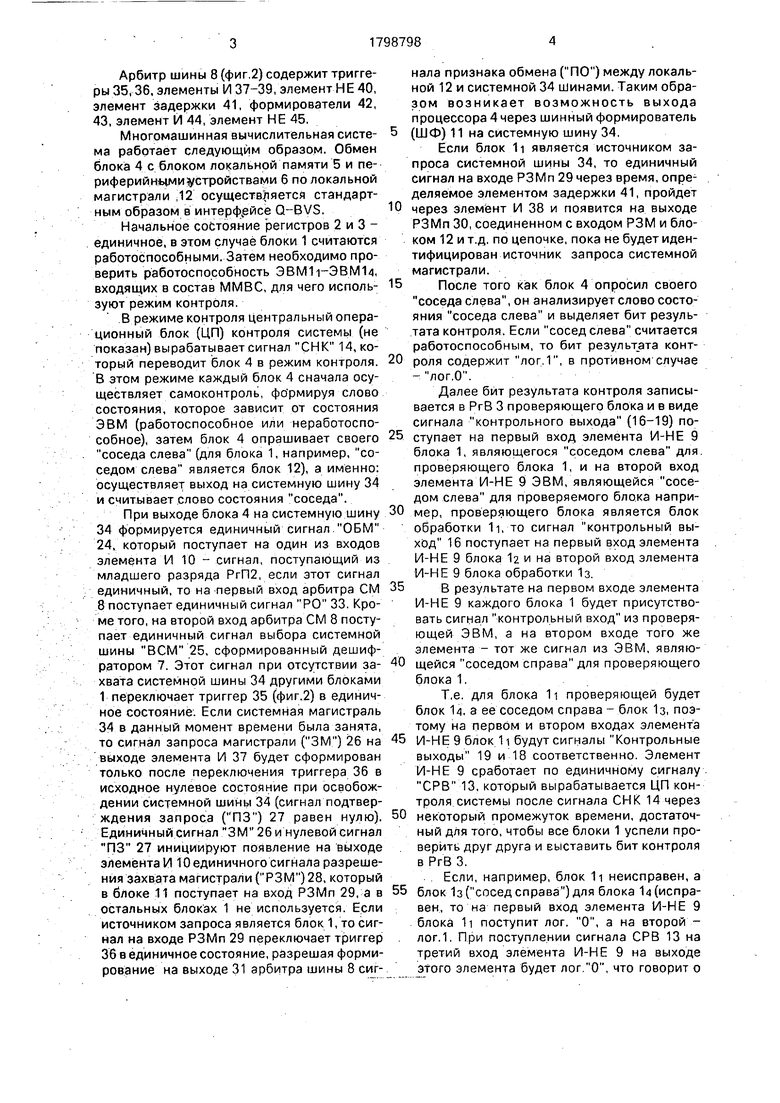

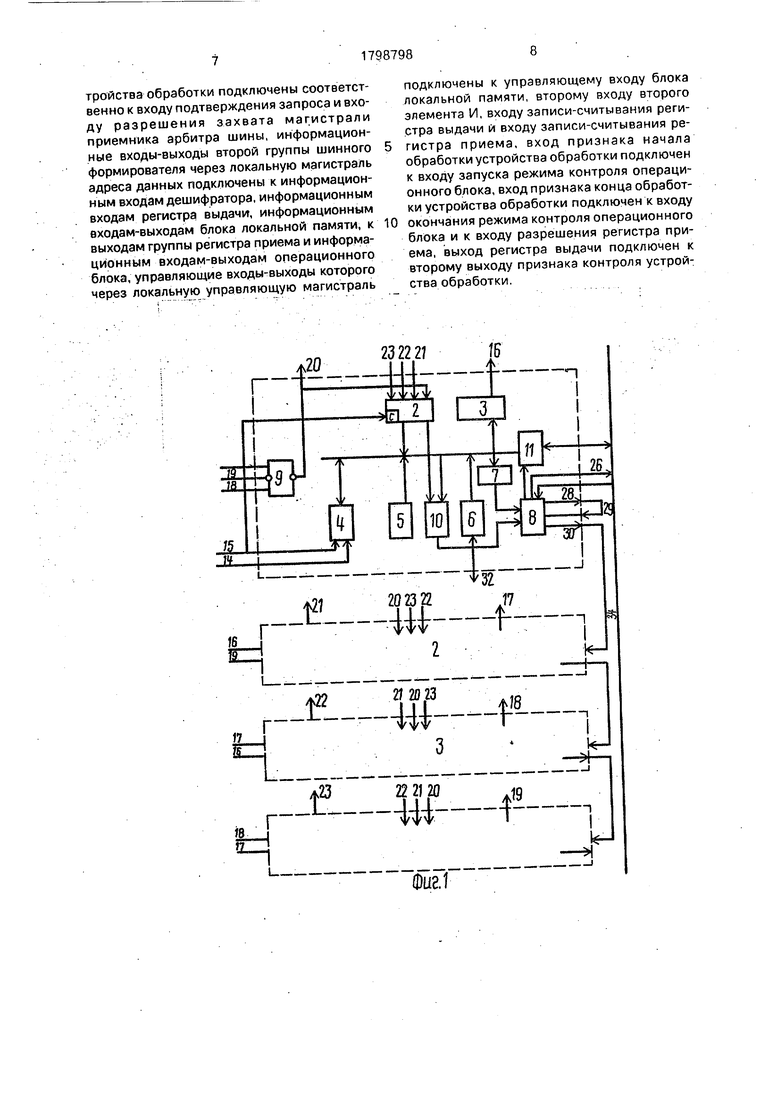

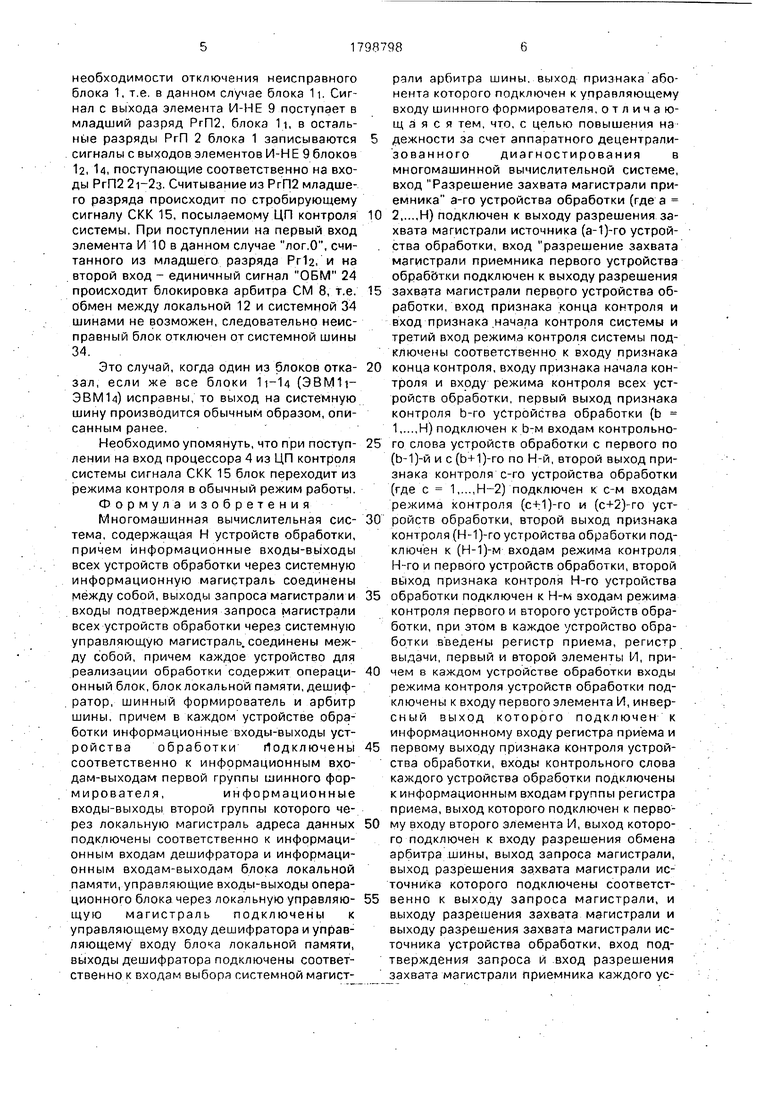

На фиг.1. представлена схема многома- шиннЬй вычислительной системы; на фиг.2 - пример реализации арбитра системной магистрали.....-.. : ,

Многомашинная вычислительная Система (фиг.1) содержит N блоков обработки (ЭВМ 11-14),. каждая из которых включает в Себя регистр приёма (РгП) 2, регистр выдачи (РгВ) 3, операционный блок 4, блок локальной памяти (БЛП) 5, периферийные устройства 6, дешифратор (ДШ) 7, арбитр шины 8, элемент И-НЕ 9, элемент И 10, шинный формирователь (ШФ) 11, локальную : магист- П раль 12. ,)

На фиг.1 обозначены следующие сигналы: Системное разрешение выдачи (СРВ) 13, Системное начало контроля (СНК) 14, Системный конец контроля (СКК) 15, Контрольные выходы 16-19, Контрольные входы 20-23 Обмен (ОБМ) 24, Выбор системной магистрали (ВСМ) 25, Запрос магистрали (ЗМ) 26, Подтверждение запроса (ПЗ) 27, Разрешение захвата магистрали (РЗМ)28,РШ приемника (РЗМп) 29 (приоритетный вход), РЗМ источника (РЗМп) 30 (приоритетный выход), Признак обмена (ПО) 31,Вход/выход (Вх/вых) 32, Разрешение обмена (РО) 33.

Многомашинная вычислительная система (фиг.1) содержит также системную шину 34, Системная магистраль 34 выполнена аналогично локальной магистрали 12 в интерфейсе.

XI

Ю 00 4 Ю 00

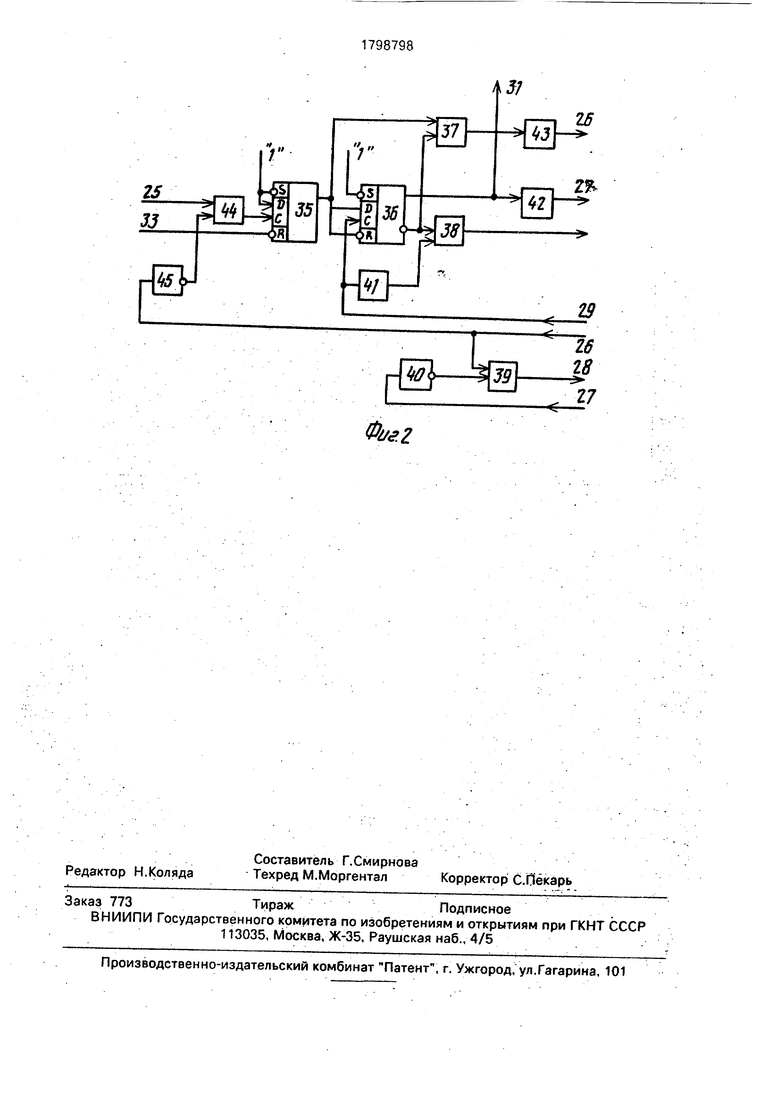

Арбитр шины 8 (фиг.2) содержит триггеры 35,36, элементы И 37-39, элемент НЕ 40, элемент задержки 41, формирователи 42, 43, элемент И 44, элемент НЕ 45,

Многомашинная вычислительная система работает следующим образом. Обмен блока 4 с блоком локальной памяти 5 и периферийными устройствами 6 по локальной магистрали ;12 осуществляется стандартным образом в интерфейсе Q-BVS,

Начальное состояние регистров 2 и 3 - единичное, в этом случае блоки 1 считаются работоспособными. Затем необходимо проверить работоспособность ЭВМ1-1-ЭВМ14, входящих в состав ММВС, для чего используют режим контроля.

.В режиме контроля Центральный операционный блок (ЦП) контроля системы (не показан) вырабатывает сигнал СНК 14, который переводит блок 4 в режим контроля. В этом режиме каждый блок 4 сначала осуществляет самоконтроль, фо рмируя слово состояния, которое зависит от состояния ЭВМ (работоспособное или неработоспособное), затем блок 4 опрашивает своего соседа слева (для блока 1, например, соседом слева является блок 12), а именно: осуществляет выход на системную шину 34 и считывает слово состояния соседа.

При выходе блока 4 на системную шину 34 формируется единичный сигнал.ОБМ 24, который поступает на один из входов элемента И ТО - сигнал, поступающий из младшего разряда РгП2, если этот сигнал единичный, то на первый вход арбитра СМ 8 поступает единичный сигнал РО 33. Кроме того, на второй вход арбитра СМ 8 поступает единичный сигнал выбора системной шины ВСМ 25, сформированный дешифратором 7. Этот сигнал при отсутствии захвата системной шины 34 другими блоками 1 переключает триггер 35 (фиг.2) в единичное состояние. Если системная магистраль 34 в данный момент времени была занята, то сигнал запроса магистрали (ЗМ) 26 на выходе элемента И 37 будет сформирован только после переключения триггера 36 в исходное нулевое состояние при освобождении системной шины 34 (сигнал подтверждения запроса (ПЗ) 27 равен нулю). Единичный сигнал ИЗМ 26 и нулевой сигнал ПЗ 27 инициируют появление на выходе элемента И 10 единичного сигнала разрешения захвата магистрали (РЗМ) 28, который в блоке 11 поступает на вход РЗМп 29, а в остальных блоках 1 не используется. Если источником запроса является блок 1, то сигнал на входе РЗМп 29 переключает триггер 36 в единичное состояние, разрешая формирование на выходе 31 арбитра шины 8 сигнала признака обмена (ПО) между локальной 12 и системной 34 шинами. Таким образом возникает возможность выхода процессора 4 через шинный формирователь

(ШФ) 11 на системную шину 34.

Если блок 1i является источником запроса системной шины 34, то единичный сигнал на входе РЗМп 29 через время, определяемое элементом задержки 41, пройдет

через элемент И 38 и появится на выходе РЗМп 30, соединенном с входом РЗМ и блоком 12 и т.д. по цепочке, пока не будет идентифицирован источник запроса системной магистрали.

5 После того как блок 4 опросил своего соседа слева, он анализирует слово состояния соседа слева и выделяет бит результата контроля. Если сосед слева считается работоспособным, то бит результата конт0 роля содержит лог. 1, в противном случае - лог.О.

Далее бит результата контроля записывается в РгВ 3 проверяющего блока и в виде сигнала контрольного выхода (16-19) по5 ступает на первый вход элемента И-НЕ 9 блока 1, являющегося соседом слева для. проверяющего блока 1, и на второй вход элемента И-НЕ 9 ЭВМ, являющейся соседом слева для проверяемого блока напри0 мер, проверяющего блока является блок обработки 1i, то сигнал контрольный выход 16 поступает на первый вход элемента И-НЕ 9 блока 1г и на второй вход элемента И-НЕ 9 блока обработки 1з.

5в результате на первом входе элемента И-НЕ 9 каждого блока 1 будет присутствовать сигнал контрольный вход из проверяющей ЭВМ, а на втором входе того же элемента - тот же сигнал из ЭВМ, являю0 щейся соседом справа для проверяющего блока 1.

Т.е. для блока 1i проверяющей будет блок 14, а ее соседом справа-блок 1з, поэтому на первом и втором входах элемента

5 И-НЕ 9 блок 1i будут сигналы Контрольные выходы 19 и 18 соответственно. Элемент И-НЕ 9 сработает по единичному сигналу СРВ 13, который вырабатывается ЦП контроля системы после сигнала СНК 14 через

0 некоторый промежуток времени, достаточный для того, чтобы все блоки 1 успели проверить друг друга и выставить бит контроля в РгВ 3. . Если, например, блок 1ч неисправен, а

5 блок 1з(соседсправа) для блока (исправен, то на первый вход элемента Й-НЕ 9 блока 1i поступит лог. О, а на второй - . лог.1. При поступлении сигнала СРВ 13 на третий вход элемента И-НЕ 9 на выходе этого элемента будет лог.О, что говорит о

необходимости отключения неисправного блока 1, т.е. в данном случае блока 1i. Сигнал с выхода элемента И-НЕ 9 поступает в младший разряд РгП2, блока 1i, в остальные разряды РгП 2 блока 1 записываются сигналы с выходов элементов И-НЕ 9 блоков 12, 14, поступающие соответственно на входы РгП2 2-|-2з. Считывание из РгП2 младшего разряда происходит по стробирующему сигналу СКК 15, посылаемому ЦП контроля системы. При поступлении на первый вход элемента И 10 в данном случае лог.О, считанного из младшего разряда Рг1г, и на второй вход - единичный сигнал ОБМ 24 происходит блокировка арбитра СМ 8, т.е. обмен между локальной 12 и системной 34 шинами не возможен, следовательно неисправный блок отключен от системной шины 34.

Это случай, когда один из блоков отказал, если же все блоки 11-14 (Э В Mil- ЭВМ 14) исправны, то выход на системную шину производится обычным образом, описанным ранее.

Необходимо упомянуть, что при поступлении на вход процессора 4 из ЦП контроля системы сигнала СКК 15 блок переходит из режима контроля в обычный режим работы.

Формула изобретения

Многомашинная вычислительная система, содержащая Н устройств обработки, причем информационные входы-выходы всех устройств обработки через системную информационную магистраль соединены между собой, выходы запроса магистрали и входы подтверждения запроса магистрали всех устройств обработки через системную управляющую магистраль, соединены между собой, причем каждое устройство для реализации обработки содержит операционный блок, блок локальной памяти, дешифратор, шинный формирователь и арбитр шины, причем в каждом устройстве обработки информационные входы-выходы устройства обработки Подключены соответственно к информационным входам-выходам первой группы шинного формирователя,информационные входы-выходы второй группы которого через локальную магистраль адреса данных подключены соответственно к информационным входам дешифратора и информационным входам-выходам блока локальной памяти, управляющие входы-выходы операционного блока через локальную управляющую магистраль подключены к управляющему входу дешифратора и управляющему входу блока локальной памяти, выходы дешифратора подключены соответственно к входам выбора системной магистрали арбитра шины, выход признака абонента которого подключен к управляющему входу шинного формирователя, отличающаяся тем, что, с целью повышения на 5 дежности за счет аппаратного децентрализованного диагностирования в многомашинной вычислительной системе, вход Разрешение захвата магистрали приемника а-го устройства обработки (где а

0 2,...,Н) подключен к выходу разрешения захвата магистрали источника (а-1)-го устрой- . ства обработки, вход разрешение захвата магистрали приемника первого устройства обработки подключен к выходу разрешения

5 захвата магистрали первого устройства обработки, вход признака конца контроля и вход признака .начала контроля системы и третий вход режима контроля системы подключены соответственно к входу признака

0 конца контроля, входу признака начала контроля и входу режима контроля всех устройств обработки, первый выход признака контроля b-го устройства обработки (Ь 1,...,Н) подключен к b-м входам контрольно5 го слова устройств обработки с первого по (Ь-1)-й и с (Ь+1)-го по Н-й, второй выход признака контроля с-го устройства обработки (где с 1,...,Н-2) подключен к с-м входам режима контроля (с+1)-го и (с+2)-го уст0 ройств обработки, второй выход признака контроля (Н-1)-го устройства обработки подключен к (Н-1)-м входам режима контроля Н-го и первого устройств обработки, второй выход признака контроля Н-го устройства

5 обработки подключен к Н-м зходам режима контроля первого и второго устройств обработки, при этом в каждое устройство обработки введены регистр приема, регистр выдачи, первый и второй элементы И, при0 чем в каждом устройстве обработки входы режима контроля устройств обработки подключены к входу первого элемента И, инвер- сный выход которого подключен к информационному входу регистра приема и

5 первому выходу признака контроля устройства обработки, входы контрольного слова каждого устройства обработки подключены к информационным входам группы регистра приема, выход которого подключен к перво0 му входу второго элемента И, выход которого подключен к входу разрешения обмена арбитра шины, выход запроса магистрали, выход разрешения захвата магистрали источника которого подключены соответст5 венно к выходу запроса магистрали, и выходу разрешения захвата магистрали и выходу разрешения захвата магистрали источника устройства обработки, вход подтверждения запроса и вход разрешения захвата магистрали приемника каждого устройства обработки подключены соответственно к входу подтверждения запроса и входу разрешения захвата магистрали приемника арбитра шины, информационные входы-выходы второй группы шинного формирователя через локальную магистраль адреса данных подключены к информационным входам дешифратора, информационным входам регистра выдачи, информационным входам-выходам блока локальной памяти, к выходам группы регистра приема и информационным входам-выходам операционного блока, управляющие входы-выходы которого через локальную управляющую магистраль

0

подключены к управляющему входу блока локальной памяти, второму входу второго элемента И, входу записи-считывания регистра выдачи И входу записи-считывания регистра приема, вход признака начала обработки устройства обработки подключен к входу запуска режима контроля операционного блока, вход признака конца обработки устройства обработки подключен к входу окончания режима контроля операционного блока и к входу разрешения регистра приема, выход регистра выдачи подключен к второму выходу признака контроля устройства обработки.

Фигг

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Вычислительная система | 1989 |

|

SU1633417A1 |

| Устройство сопряжения многопроцессорной системы | 1987 |

|

SU1575195A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1988 |

|

SU1571603A1 |

| Устройство для обмена данными между процессорами | 1988 |

|

SU1566361A1 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| УСТРОЙСТВО МЕЖМАШИННОГО ОБМЕНА | 1989 |

|

SU1635782A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

Изобретение относится к вычислительной технике и может использовать для создания отказоустойчивых многомашинных и многопроцессорных вычислительных систем. Целью изобретения является повышенная надежность за счет аппаратного децентрализованного диагностирования в многомашинной вычислительной системе. Поставленная цель достигается тем, что система содержит Н устройств обработки, каждое устройство обработки содержит операционный блок, блок локальной памяти, дешифратор, шинный формирователь, арбитр шины, регистр приема, регистр выдачи, два элемента И. 2 ил.

| Кипятильник для воды | 1921 |

|

SU5A1 |

| В.А.Шахнова | |||

| М.: Радио и связь, 1988, т.2, | |||

| Построение сетей ЭВМ, М.Като, Д.Иимура, М.Токоро и :др | |||

| М.г Мир, 1988, с.266-268; | |||

Авторы

Даты

1993-02-28—Публикация

1990-08-13—Подача