(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Устройство для ввода информации | 1983 |

|

SU1113793A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для отображения информации | 1990 |

|

SU1785035A1 |

Изобретение относится к устройствам управления доступом к общему каналу связи и может быть использовано в системах сбора и обработки информации. Цель - повышение оперативности - достигается за счет введения в абонентские блоки обнаружителя информации, выполненного на первом и втором элементах ИЛИ и регистре сдвига, а также анализатора наполнения блока памяти, реализованного на первом, втором и третьем триггерах и первом, втором и третьем элементах И. Управление доступом абонентскими блоками 5 к каналу связи через блок элементов ИЛИ осуществляется распределителем импульсов. 1 ил.

Изобретение относится к передаче дискретной информации и может быть использовано при организации систем связи и вычислительных систем с общим каналом связи, а также в системах телеметрии, телеуправления и телесигнализации.

Целью изобретения является повышение оперативности передачи информации.

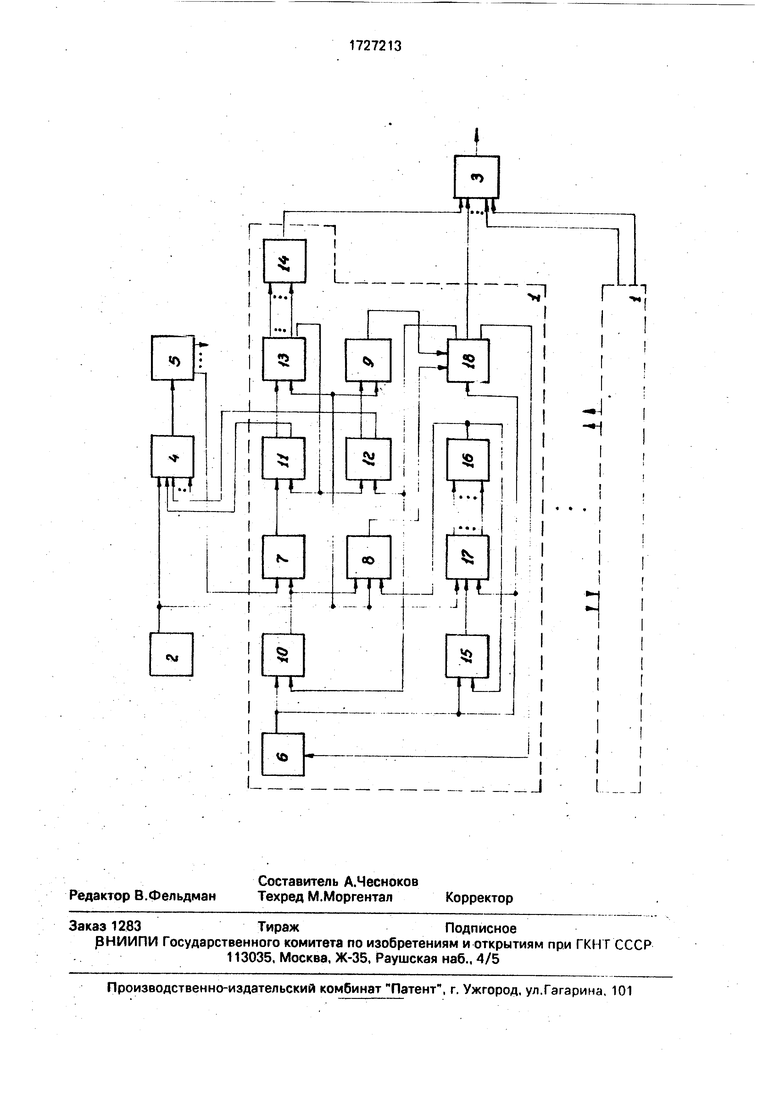

На чертеже представлена структурная электрическая схема устройства.

Устройство управления доступом к общему каналу связи содержит абонентские блоки 1, генератор 2 импульсов, блок 3 элементов ИЛИ, блок 4 элементов И и распределитель 5 импульсов, при этом каждый абонентский блок 1 содержит источник 6 информации, первый 7, второй 8 и третий 9 элементы И, первый 10, второй 11 и третий 12 триггеры, счетчик 13, мультиплексор 14, первый 15 и второй 16 элементы ИЛИ,-регистр 17 сдвига и блок 18 памяти.

Устройство управления доступом к общему каналу связи работает следующим образом.

Генератор 2 импульсов вырабатывает тактовые импульсы, которые через первый вход блока 4 элементов И поступают на вход распределителя 5 импульсов и запускают его. От первого тактового импульса появляется первый импульс на первом выходе распределителя 5 импульсов, а от второго тактового импульса появляется второй импульс на втором выходе распределителя 5 импульсов и т.д. до N, где N - число абонентских блоков 1. Импульсы поочередно появляются на выходах распределителя 5 импульсов и, поступая на первый вход каждого абонентского канала 1, опрашивают тем самым состояния источников 6 информации.

Допустим, что на выходе источника 6 информации первого абонентского блока 1

со

имеется дискретная информация, тогда она, поступая на первый вход первого триггера 10, переводит его в единичное состояние. Первый бит в начале передачи любой информационной последовательности имеет уровень логической единицы. Одновременно с этим информационные импульсы поступают на первый вход регистра 17 сдвига и, через первый вход первого элемента ИЛ И 15 на второй вход регистра 17 сдвига, обеспечивая уровнем логической единицы режим последовательного ввода информации со сдвигом вправо. Сдвигающий регистр 17 загружается данными посредством тактовых импульсов, поступающих на его тактовый вход с выхода генератора 2 импульсов. Второй элемент И Л И 16 осуществляет логическое сложение информационных импульсов, появляющихся на выходах регистра 17 сдвига. Благодаря этому обеспечивается постоянство сигнала уровня логической единицы в течение времени поступления информационных импульсов, на выходе второго элемента ИЛИ 16, которая одновременно подается на третий вход второго элемента И 8, и через второй вход первого элемента ИЛИ 15 на второй вход регистра

17сдвига. На основании вышесказанного создаются условия для прохождения тактовых импульсов, генерируемых генератором 2 импульсов, через второй вход второго элемента И 8, на тактовый вход блока 18 памяти, а также для неизменности сигнала уровня логической единицы на выходе первого элемента ИЛИ 15, который, поступая на второй вход регистра 17 сдвига, обеспечивает режим последовательного ввода информации со сдвигом вправо. Тактовые импульсы, поступая с выхода второго элемента И 8 на тактовый вход блока 18 памяти, записывают поступающие с выхода источника 6 информации информационные импульсы. В случае полного заполнения блока

18памяти с его выхода переполнения на вход источника б информации подается сигнал, приостанавливающий передачу информационных импульсов.

Запись информационных последовательностей в блок 18 памяти может производиться неоднократно. Приход определенного количества нулевых битов после поступления последнего единичного импульса является признаком окончания передачи источником 6 информации дискретной последовательности. После поступ- ления заданного количества нулевых битов на всех выходах регистра 17 сдвига будут уровни логического нуля, которые после сложения их во втором элементе ИЛИ 16, также обеспечивают уровень логического

нуля на его выходе. Этот сигнал, поступив на третий вход второго элемента И 8, запрещает прохождение тактовых импульсов на тактовый вход блока 18 памяти, а также проходит из второй вход первого элемента ИЛИ 15, на первом входе которого имеется уровень логического нуля из-за отсутствия информации на выходе источника 6 информации. Уровень логического нуля с

выхода первого элемента ИЛИ 15 проходит на второй вход регистра 17 сдвига, переводя его тем самым в режим хранения.

При поступлении сигнала с выхода распределителя 5 импульсов на первый вход

первого абонентского блока 1 этот импульс появляется на выходе первого элемента И 7 и переключает второй триггер 11 в единичное состояние. При этом уровень логического нуля, поступающий с его второго выхода

на один из входов блока 4 элементов И, запрещает прохождение тактовых запускающих импуле-.сов на вход распределителя 5 импульсов. Уровень логической единицы, появившийся на входе сброса счетчика 13,

активным уровнем которого является уровень логического нуля, разрешает подсчет тактовых импульсов, поступающих на его тактовый вход с выхода генератора 2 импульсов. Счетчик 17 под их действием перебирает свои состояния, тем самым осуществляя изменение кода, поступающего на адресные входы мультиплексора 14. Происходит последовательная коммутация

входов данных мультиплексора 14 к его выходу. На входах данных мультиплексора 14 выставлен код данного абонентского блока 1. Этот код поступает на один из входов, блока 3 элементов ИЛИ и без задержки,передается в канал связи, После перебора счетчиком 13 всех своих состояний на его выходе переполнения появляется единичный импульс, который одновременно поступает на первый вход второго триггера 11,

переключая его в нулевое состояние, и яа второй вход третьего триггера 12, перебрасывая его в единичное состояние. Со второго выхода третьего триггера 12 уровень логического нуля поступает на один из входов блока 4 элементов И, не разрешая тем самым прохождение тактовых импульсов на вход распределителя 5 импульсов на время чтения информации из блока 18 памяти. Уровень логической единицы с первого выхода третьего триггера 12 поступает на пер- вый вход третьего элемента И 9, обеспечивая прохождение тактовых импульсов, поступающих на его второй вход, на второй вход блока 18 памяти. Цифровая информация считывается из блока 18 памяти и, поступая на один из входов блока 3 элементов ИЛИ, проходит в канал связи.

В блоке 18 памяти дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими автономные адресные входы, поэтому можно вместе с чтением данных из него, производить запись дискретной информации, поступающей с выхода источника 6 информации.

После чтения последнего, записанного в блок 18 памяти, бита блок 18 памяти выдает импульс сброса, который поступает одновременно на второй вход первого триггера 10 и на первый вход третьего триггера 12, перебрасывая их в нулевое состояние и подготавливая к передаче информации, поступающей с выхода источника 6 информации. После появления уровня логической единицы на втором выходе третьего триггера 12 начинается прохождение тактовых импульсов через первый вход блока 4 элементов И на вход распределителя 5 импульсов, который вновь начинает производить опрос состояний источников 6 информации.

Формула изобретения

Устройство управления доступом к общему каналу связи содержащее абонентские блоки, генератор импульсов, блок элементов ИЛИ и последовательно соединенные блок элементов И и распределитель импульсов, выходы которого подключены к первым входам соответствующих абонентских блоков, каждый из которых содержит источник информации и первый элемент И, первый вход которого является входом абонентского блока, отличающееся тем, что, с целью повышения оперативности, в каждый абонентский блок введены первый, второй и третий триггеры, второй и третий элементы И, счетчик, мультиплексор, первый и второй элементы ИЛИ, регистр сдвига и блок памяти, выход переполнения которого подключен к управляющему входу источника информации, выход которого подключен к объединенным первым входом блока памяти, регистра сдвига, первого элемента 5 ИЛИ и первого триггера, выход которого подключен ко второму входу первого оле- мента И и к первому входу второго элемента И; выход которого подключен к тактовому входу блока памяти, первый выход которого

0 подключен ко второму входу первого триггера и к первому входу третьего триггера, второй вход которого объединен с первым входом второго триггера и подключен к выходу переполнения счетчика, вход сброса

5 которого соединен с первым выходом второго триггера, второй вход которого соединен с выходом первого элемента И, первый выход третьего триггера подключен к пер вому входу третьего элемента И, выход ко0 торого соединен со вторым входом блока памяти, выход которого является первым выходом абонентского блока, вторым выходом которого является выход мультиплексора, входы которого подключены к выходам

5 счетчика, тактовый вход которого объединен с тактовым входом.регистра сдвига, вторыми входами второго и третьего элементов И и является тактовым входом абонентского блока, третьим и четвертым

0 выходами которого являются вторые выходы второго и третьего триггеров, выход первого алемента И соединен со вторым входом регистра сдвига, выходы которого подключены ко входам второго элемента ИЛИ, вы5 ход которого подключен ко второму входу

первого элемента ИЛИ и к третьему входу

второго элемента И, причем выход генерлтора импульсов подключен к тактовым вхо- дам абонентских блоков и первому входу

0 блока элементов И, к другим входам которого подключены вторые и третьи выходы або- нентских блоков, первые и вторые выходы которых подключены ко входам блока элементов ИЛИ.

г з

q

| Устройство управления доступом к общему каналу связи | 1988 |

|

SU1598215A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-04-15—Публикация

1990-03-05—Подача