Ич(1Прс1 {МП UTIKK: ит( И ;- - ЫЧИ(;:И TOjibFmii T-c jiiiUKC и можс Т Пыт;-: исгкхчьrUlflHHn при ПОСТПО(:М1ИИ MHl Г |1МЛ111ИЯ; ЫХ

вгичислительных гсст см на блпе микгл - ЭВМ г. общей шнион.,

Цель изобрстеьт ля - расширение функциональных возможиостс ; за счет обсслпчення режима перек.л1оления I:IHH

Ил .1 предстлплеиа блок-схема ycTpoiiCTHa п фрагменте двухмап:иииой нычислительноГ системы с оГиким ле- риферт1} 11 ым устройст юм; на фиг. 2 - распределение адресных входов и информационных выходов лостоя но1 1 па- мяти прог рамм управления; ла фиг„3 - схема блока управления прерыванием; ка фиг.4 - схема блока управления прямым доступом к памяти.

Двухмашинная вычислительная сксте ма о6;)аботки данных содерж1-;т (фиг ,1 и 2) две микроэвм 2, например, типа Эдектроника-60., периферийное устройство 3, например, типа Кон- или и устройство 4 для сопряжения.

ЭВМ 1 связана с устройством А магистралью 5, со/гержащс-й информаш--;он- ные 6 и управлямицк- 7 ЭВМ 2 связана с ycrpoficTBOM А маг страл::,ю 8, содержащей информа1 ионн :1е 9 и управляющие 10 шинь. Устрчм-ютво А связатю с периферийным устройство 3 магистралью 11, содержащей ич-гфор- мационные 12 и управляющие 13 шин,;.

Устройство для сопряжен1-я содержит дешифраторы 14 и 15 ад :-есоп, постоянную память 16 программ упраг,-- ления, регистры 17 и 18 )авляю1цих сигналов и состояния, прнемспере; ат- чики 19 и 20, блок 21 уг1ра1 ле};ия лр; рыванием, блок 22 у 1раллення ) доступом к памяти, регистр 23 ii, ных, счетчики 2- ;. и 2Ь адреоов, счетчик 26 слов, регистр 27 режимов, шл- ход 28 разряда флага готовности :;Р гистра 23 данных5 группы 29 и 3( выходов дешифраторов :4 и 1 5 са, первьй 31 и второй 32 ;ь::хо;1ы блока 21, с первогч: по дес5- гый 33-42 j orHT-recKoro ycлos iя блока 2 i , с первого по четвертый входы 4)-4(5 логического условия б.лока 22, с г:орвого по пятый выходы 47--50 .12. группу 51 вь ходов 22,, с riei::-Bo- го по се,дьмой .-гиформаг ионш -е выхо; ;ь 52-58 постоянной 1 ;амяти 16, с г;ер- вого по сед1)Мой адресные входь: 59 - 66 постояТ Но п,)мяти 16, с первой

0

0

5

0

5

0

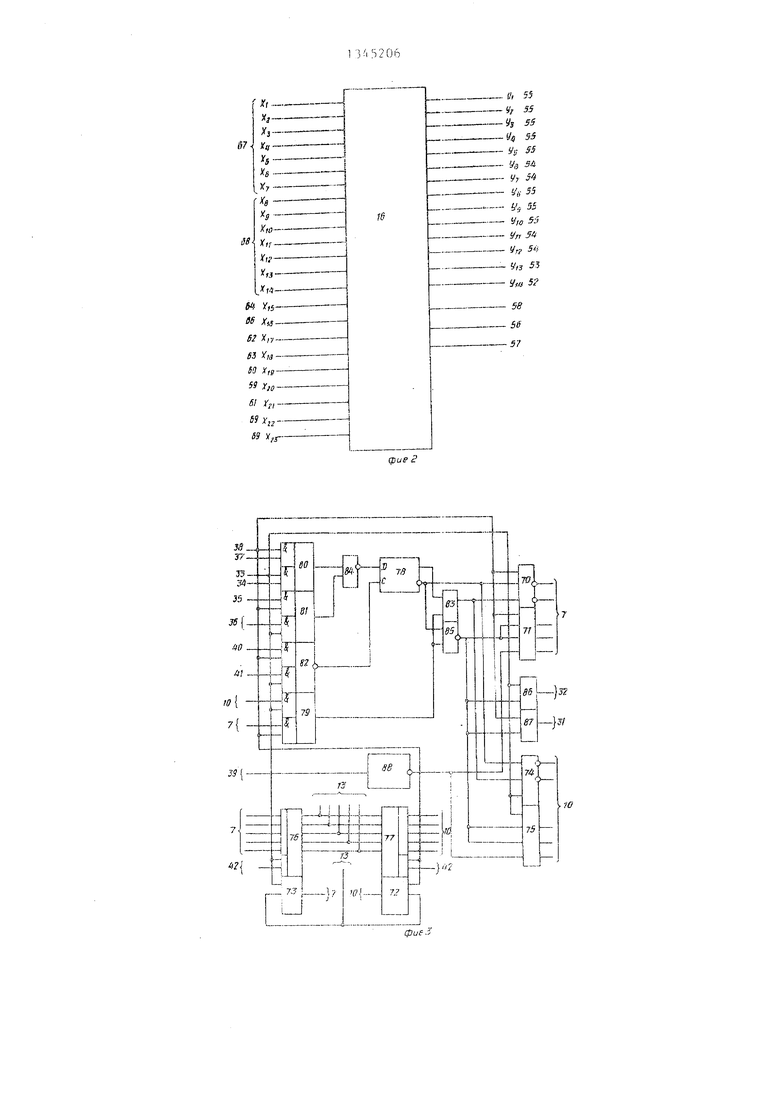

ре :-;,нс пуппь; /,/-,.) ;;;iр С нмх ихо- noi: оя н и ( , а.мчти I i , )ЛО - 21 vnpa Fijic л я прерыи, нием с од ержи (.4) перед; чики 70-715 П1и емс1 тере/итт чики 76 н 77, тригг ер 78, эл. И-НЛИ 79-81, : лемент l- i-HJIH-l-n- , 82, Т1 емент И 83, члементы И-ИЕ 84 и 85, о.лемгиты HJFH 86 и 87, одновибратор 88,

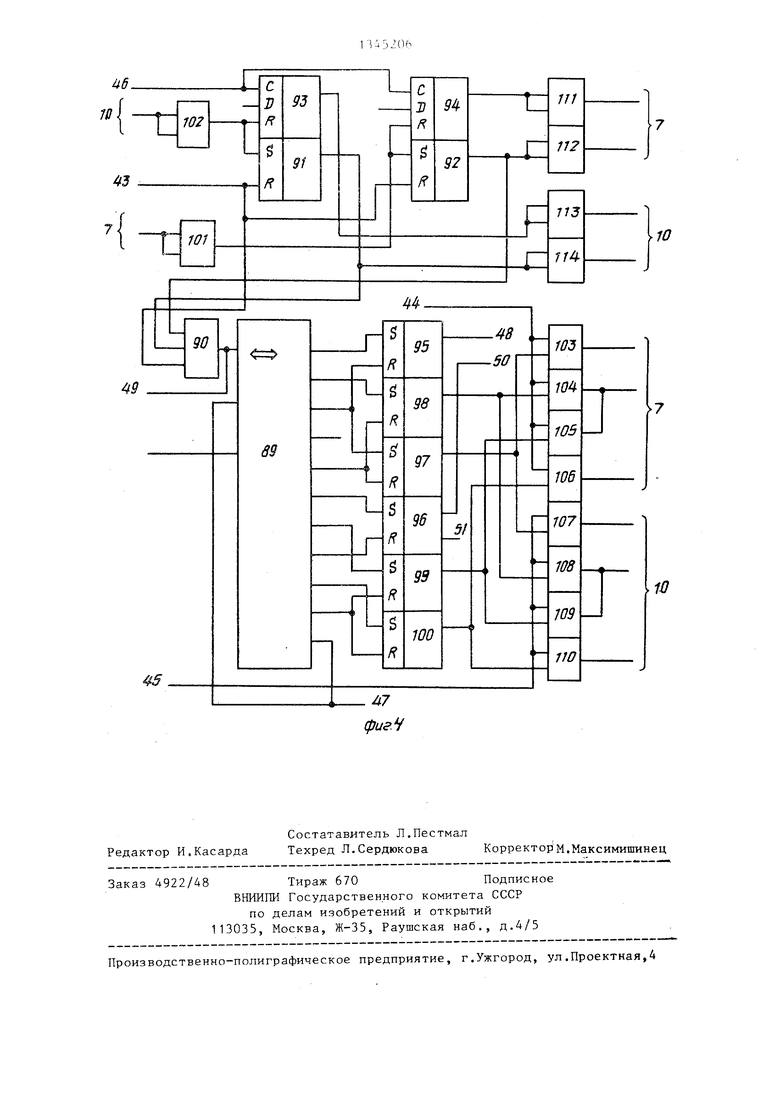

плок 22 у 11рат леи я досту- iioM к памяти сг- держит (фиг-, 5) регистр 89, элемент И 90 триггеры 9-100, ри( 101 и i02, передатчики 103-1 14„

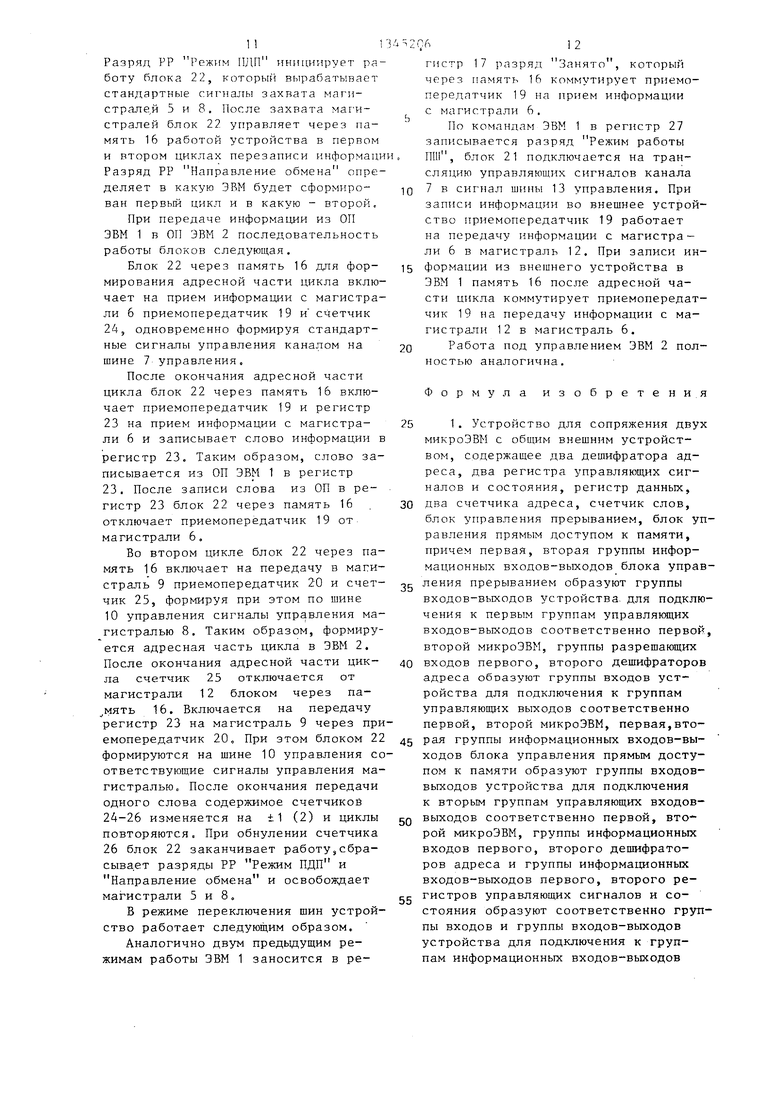

Назначение вхо;;отв и выходов постоянно памяти 16 следую 1,ее .

/1ля , адресных входов 67 - 1п,ение к регистру 23 (1) - , счетчику 24 (1) - сигнал чику 25 (|) - сигнал Xj,

26 (1) - си- нал Х, реги- (1) - сигнал Xj-, сигнал Ввод от ЭВМ 1 - л., сигнал Вывод or ЭВМ 1 - X, ,

/1.ЛЯ 1 рупг Ы адресных входов 68 - ото к рег истру 23 (2) - сиг п ал Xg, счетч ику 24 (2) - сигнал Хд, счс гчику 25 (2) -- сигнал X , cqe 4H -:y 26 (2) - сигнал X . , регистру 27 (2) - ,и X,,, сигнал Ввод от ЭВМ 2 - X ,,, , сиз нал Вывод ЭВМ 2 - ,,,

Эти .-.1 РГ5ВНЫ единице после того, чпк соо Г етствующая микроЭВМ п.став:: ; канале: адрес соответ- ствую1,гго iei-; CT a устройства, )В / глиифрируется н запоминается ,в дешифр;л оре 1 или 15.

По л ход;1м 64 и 66 из регистра 17 и р,ег 1с;тра 18 з память ; 6 постуX .., За: ТО обр,

с .п нал : Х , сче с чет 1И г с т р у 2 7

1

г ают сигна.;. гято 2 - Х,,.

По 62 и 63 из регистра 27 I-. гамя-ь 16 оступают сигналь:: Режим - X,,,,, Паг равление обмена (НО) -- X .„ , причем разряд направле- ;:ия обм(:на е.г :иницер ес.ли ус- ic ;новлен режим для ведущей ; Т5М.

По isxoriaM 60 59 61 5 69 из блока 22 I; Г1амят) if) 1 :оступан;т следую11

iq 1Адрес РД

X.,,, СЧ X,,.

Bbixo;i, с игнйЛ памят : 16 обР газуют с ЛеДУН)11П:(: 1-1.ХОДЫ,

Упр, иление записью регистра 23

Y,

н

если ecTi)

31

ращенир. со стороны одной из ЭВМ, занявшей устройство, к регистру 23 в цикле Вывод или в режиме прямого доступа к памяти (ПДП), если выработан сигнал ЗП РД,

Управление записью счетчика 24 - Yj; Yj 1 в случае, если есть обращение со стороны одной из ЭВМ, занявшей ycTpoAcTBOjK счетчику 24 в цикле Вывод о

Управление записью счетчика 25 - Y осуществляется аналогично. Управление записью счетчика 26 - Y осуществляется аналогично. Управление записью регистра 27 Y осуществляется аналогично.

Управление приемопередатчиком 19 на прием - Y 1 в случае, если ЭВМ 1 заняла устройство, режим обмена программный и нет обращения к регистру 23 со стороны ЭВМ 2, или в режиме ПДП, если установлен разряд Направление обмена и выработан сигнал X,,, Адрес

или в режиме

переключения щин (ПШ), если нет сигнала Ввод от ЭВМ 1, или в режиме ПДП, если ЭВМ 2 заняла устройство, разряд Направление обмена не установлен и выработан сигнал X Адрес 1,

Управление приемопередатчиком 20 на прием - Y, 1 в случае, если ЭВМ 2 заняла устройство, режим обмена программный и нет обращения к регистру 23 со стороны ЭВМ 1 , или в режиме ПДП, если установлен разряд Направление обмена и выработан сигнал Адрес 1, или в режиме ПШ, если нет сигнала Ввод от ЭВМ 2, или в режиме ПДП, если ЭВМ 1 заняла устройство, разряд Направление обмена не установлен и выработан сигнал Xjo Адрес 1.

Управление регистром 23 на считывание - Yg; Yg 1, если ЭВМ 2 заняла устройство, есть обращение -к регистру 23 от ЭВМ 1 в цикле Ввод или если ЭВМ 1 заняла устройство и есть обращение к регистру 23 от ЭВМ 2 в цикле Ввод, или, если выработан сигнал Х Считывание РД.

Управление счетчиком 24 на считывание - Yg; Yg 1, если ЭВМ 1 заняла устройство, разряд Направление обмена установлен и йьфаботан сигнал Xj(, Адрес 1, или разряд Направление обмена не установлен и выработан сигнал Xj Адрес 2 или

10

52064

если ЭВМ 2 заняла устройство, разряд Направление обмена установлен и вьгработан сигнал Х, Адреса 2, или разряд Направление обмена не

5 установлен и выработан сигнал Х,, Адрес 1.

Управление счетчиком 25 на считывание - Y,o , Y ,0 1, если ЭВМ 1 заняла устройство, разряд Направление обмена не установлен, вьфабо- тан сигнал X о Адрес Г или, если разряд Направление обмена установлен и выработан сигнал X, Адрес 2 или, если ЭВМ 2 заняла устройство, разряд Направление обмена установлен и выработан сигнал , Адрес 1, или разряд Направление обмена не установлен и выработан

2р сигнал Xj, Адрес 2.

Управление приемопередатчиком 19 на передачу - Y, , Y 1, если ЭВМ 2 заняла устройство и в режиме программного обмена есть обращение к

2g регистру 23 от ЭВМ 1 в цикле Ввод, или в режиме ПДП, если установлен разряд Направление обмена и вьфа- ботан сигнал X ,, Адрес 2, или, если ЭВМ 1 заняла устройство в режиме ПШ и идет канальный цикл Ввод, или в режиме ПДП, если разряд Направление обмена не установлен и выработан сигнал Адрес 2,

Управление приемопередатчиком 20 на передачу - 1, если

ЭВМ 1 заняла устройство и в режиме программного обмена есть обращение к регистру 23 от ЭВМ 2 в цикле Ввод, или в режиме ПДП установлен разряд Направление обмена и выработан сигнал Xj, Адрес 2, или, если ЭВМ 2 заняла устройство в режиме ПШ и идет канальный цикл Ввод, или в режиме ПДП, если разряд Направление обмена не установлен и

вьгработан сигнал Х Адрес 2,

Управление передатчиками 103-106 в блоке 22 - Y,,; , если ЭВМ 1- заняла устройство, установлен ре- сд жим ПДП, не выработан сигнал Адрес 2 и установлен или не установлен разряд Направление обмена, или, если ЭВМ 2 заняла устройство, установлен режим ПДП, не выработан сигнал Адрес 2 и установлен или не установлен разряд Направление обмена.

Управление передатчиками 107-100 в блоке 22 - Х н если ЭВМ 2 заняла устройство, установлен

40

БП )

режим ГЩП, но яырлботаи :и:-иа,-| Л;;- рее 1 и устаноп.тк. и или ж угтаиг Ц- лен разряд Напр,) обмена, или, если ЭВМ занял; ycTpoi-kvi-fio

нл.;; Ллрсг1 и у; Г ажш it- i или

у 1ц;1Р ир Лчрч; Haiipa пл(М и( мс на ,

ВХ Хчиыоv Г ыходны( ( игнллы

t, тановлен режим ПЛИ, не пыработан сиг- ны слсл.укмиими С(М)тн, М11пи1,чми:

,.Х,-Х,, VXg X ,,, X,, V

Y,.Х.Х,. VX, Х - Х,, ;,

Y,,, VХ,- X,,. X,,, ;

Y 7 15 f - м м 1 ;

YJ Xj-X -X,-VX,,, Х. X . ;

Y, X.,, X,.,,.X,g X, V

Х.. ,„ V X,, X,,-X,,V X,,. Х,.

YV Хг.,о Х, V х,- x:,.x,,,v х„-х YB х,-х,.х., V х,-х,,. X,, V х,з

Yg Х,, Х,, X,, V Х. X..,. Х, V Х,. Х,. X.v .21 -rt -te

Y

Y

Y, X,. X,,. X,,.X,, V X, ...

Y X

7 -r..o X, V x,- x:,.x.v x,,-x, . x.v x,-x,,. x, ;

V X.. -X,,. X,

MO x,,.x,j.x, V X,, .x.,,..x,vx..x,, x,v x,. x,. X,, ;

я r- ., - f-,.-X V n Se . ./ X.

X.. Х„Л X,,,- X.,VX,,.X.X,, ;

V X, . X,,-X,,.X,,;

18

Y,, X,,. . X. V X,,.X,. X,,X,vX,5- X,,.X,,V ..- .

Сигналы гаи (X,-,), BB1 i X () , )VB2 (X ) транслируются через ПГ1У 16 бс : изменений,

Блок 21 управления прерьшаниемч работает следующим образом,

Если установлен разряд ТПР в регистре 17 (18) ведущей машины и ус-- тановлен разряд Р11Р в регистре 17 (18) ведомой маигины, то триггер 78 устанавливается в нулевое состояние по заднему фроЕ1ту канальнс г з сигнала Ввод магистр;али 7 или 1C в зависимости от того, какая микро-ЭВМ ведущая. Канальный сигнал ТИ вырабатывается в ведомую машину за счет блокировки передат И лОВ ведущей маширгы снт налом Занято с регистра 17 (18) ведущей . Сиг-нал Нредостав.чевие прерывания ; из капала ведомоГ метилы поступает

нл.;; Ллрсг1 и у; Г ажш it- i или иг

у 1ц;1Р ир Лчрч; Haiipa пл(М и( оО- мс на ,

ВХ Хчиыоv Г ыходны( ( игнллы спязаны слсл.укмиими С(М)тн, М11пи1,чми:

v .21 -rt -t

V X.. -X,,. X,

0

5

через элемент И-ИЛИ 79 на вход элемента И-t-iF 85, вызывая вырабатывание сигналов Синхронизация пассивного устройства, выдачу адреса вектора F, канал ведо1 1ой микроЭВМ и сброс разряда ТПР в регистре 17 (13) ведущей ЭВМ. Триггер 78 устанавливается Е единичное состояние, снимая сигнал ТПР в канал ведомой ЭВМ и вырабатывая сигнал Предоставление прерывания 1 по совпадению с сигналом Предоставление прерывания 1, и запрещает распространение этого сигна.чя. другим устройствам. Ведомая микро ;)ВМ снимает сигнал Предоставление прерывания 1, Устройство снимает ;;:г-::гналь Синхронизация пассив - яого устройства адрес - вектора и Предг с:тавление прерывания Ф .По задне у фронту сигнала с выхода счет71345206

одновибрато р 88 вырабал Прерывание по таймею ЭВМ.

переключения тин разряд 21 открывает передачу сигналов из магистрали агистраль периферийных ПУ) через приемопередат77 в зависимости от точ

е

5

10

в х п за ге за но ре сд и чи чт ча до ты

го, какая микроЭВМ заняла устройство. Передатчики 73 или 72 транслируют сигнал Синхронизация пассивного устройства из магистрали ПУ в магистраль ведущей микроЭВМ.

Блок 22 работает следующим образом.

После записи в регистр 27 разряда Рехким ПД 5 выход которого соединен со стробирующими входами триггеров 93 и 94, их выходы устанавливаются в 1 и в магистралях

7и 10 микроэвм 1 и 2 соответственно вырабатываются сигналы требования прямого доступа (КТДЦ1 иКТПД2)

8ответ на эти сигналы ЭВМ 1 и 2 на шинах предоставления прямого доступа (ПЦЦ1 и ППД2) выставляют соответствующие сигналы, которые через приемники 101 и 102 устанавливают триггеры 91 и 92 и сбрасывают триггеры 93 и 94. Таким образом, происходит захват управления магистралями 5 и 8 блоком 22. Совпадение трех единиц на элементе И 61, двух сигналов ПВ и сигнала Не равен О со счетчика 26 слов разрешает работу регистра 89 сдвига.

По переднему фронту сигнала, поступающего с элемента И 61, в первы разряд регистра 89 записывается 1 (в остальные разряды О),которая устанавливает в 1 триггер 95, вход которого открывает на передачу один из приемопередатчиков 19 или 20 в зависимости от разрядов Направление обмена и Занято. Далее в соответствии с тактовой частотой производится сдвиг 82 с 1 по 11

1 в регистре

с 1 по 11 разряд и установка и сброс триггеров 95-100.

После записи 1 во 2-й разряд в 1-й разряд из 11-го разряда записывается О и устанавливается триггер 98, на котором вырабатывается СИА дпя ЭВМ - источника информации. Выход триггера 98 соединен с передатчиками 104 и 108. На передачу подключается только один из них.

что определяется сигналами Y и Y

н

ет в 111 (t

0

5

0

Sainicb 1 в 3-й разряд сбрасыва- 0 триггер 95 и устанавливает в 1 триггер 97 сигнала Ввод, выход которого соединен с вх одами двух передатчиков 103 и 107. Установка 1 в 4-м разряде формирует сигнал записи в регистр 23. После записи 1 в 5-й разряд сбрасываются триггеры 98 и 97 и заканчивается цикл записи слова в регистр 23. Аналогично происходит перезапись слова из регистра 23 в память ЭВМ-приемника сдвигом 1 из 6-го разряда по 10-й и установкой триггеров 96-100. Отличие от первого цикла состоит в том, что теперь в адресном цикле подключается на передачу счетчик 25 и выходом с 8-го разряда управляется считывание регистра 23.

Регистр 27 режимов служит для задания одного из возможных режимов работы устройства и направления

5 обмена данными для режима прямого доступа к памяти и содержит разряды: обмен в режиме ПДП; режим ПШ; направление обмена.

Приемопередатчики 19 и 20 имеют

0 три состояния на входах-выходах и

служат для подключения регистров устройства к общим шинам микроЭВМ. Регистр 23 данных используется в режиме программного обмена, а также об5 мена ПДП между двумя микроЭВМ для промежуточной фиксации данных.

Счетчик 26 слов при программном обмене выполняет функции контроля времени обмена, в режиме ПДП исполь0 зуется для занесения длины передаваемого массива. Память 16 служит для предотвращения конфликтных ситуаций в работе устройства при одно- в.ременном обращении к нему со сторо5 ны сразу двух микроЭВМ, разрешая запись в регистры и счетчики. 23-27 только со стороны машины, занявшей устройство, и осуществляет коммутацию направления передачи информа0 ции приемопередатчиками 19 и 20 в зависимости от режимов работы устройства и обращений к блоку адресуемых регистров, а также управляет, считыванием информации из блока ад5 ресуемых регистров.

Счетчики 24 и 25 адресов используются для занесения начальных адресов обмена в режиме ПДП. Счетчик 24 формирует адрес в память машины,захватившей устройство, я с -1отч1-;к /. в память второй микроЗВМ. Бочможно автоматическое наращир.лиие или умейшение на 1 (2) адрссор памяти зтими

счетчиками.

Блок 22 служит для формировакия: сигналов управления каналами микро- ЭВМ в режиме прямот о дрступа к памяти для передачи информации из памя- ти одной микроэвм в память второй без участия процессора. Блок 21 управления прерыванием служит для формирования сигналов прерывания программы в первую или вторую машины, что определяется тем, какая машина захватила устройство.

Устройство может работать в следующих режимах: программнс го обмена обмена по каналу 1ЩП; IIHI,

В каждом из возможных режимов о;; боты только о;;на микроЭВМ может захватить устройство сопряжения, записав в свой регистр 17 (18) разрчд Занято, который автомат1-п ески бло кирует установку аналогичного разряда в другом регистре 18 (17).

В режиме программного обме}1а устройство работает следующим образом«

По командам программы ЭВМ 1 в ре гистр 17 записываются разрядь: Устройство занято, . Разряд Занято блокирует записг, аналогичного разряда в регистр 18, Таким образом ЭВМ 2 не может его записать програм мным путем. Одновременно через памя 16 этим разрядом пр иемопередатчика 19 включается на Прием информация с информационной шины 6 и коммутигуу ется блок 21 на магистраль К), пс.г.и чего в ЭВМ 2, если установлен разряд РПР в регистре 18, вырабатывается сигнал ТПР.

ЭВМ 1 записывает через приемопер датчик 19 в регистр 23 данные для передачи в ЭВМ 2. При этом jjerM- стра данных подиимаетс;я в Г и поступает в регистры 17 и 18, В чике 26 ЭВМ 1 я;и1исл ;рзает вр ;:мя, о-- водимое на обмен, и в регис : р 2/ - разряд Режим обмена программный ., который переводит счетчик 26 я режим работы счетчика времени,

ЭВМ 2 по программе обработки пре рывания опрашииает ФГ РД, которь1й считывается через регистр 18 п формирует команду иб); шения к регистру 23. Сигнал обрашсмгия J15M 2 к регистмаг1;стр;;. 1и

rnci pnj b ), i);uio;ips-M( перояодя регист : 23 i режим считыиания инфор N).

После счкть влния рсм ястрл 23 ЭВМ 2 устройство ,()з ф. пп.аетс я в исходное гостояш е, Понт;фкг;ггс я операции по :-:аписи регистр.:; 23 H:J ЭВМ 1 и счи- Tbinai-nisi ei o з ЭВМ 2, Лля контро.ггя }1реме)и 1бме {п я тгом режиме испо. зуется счетчик 26. По окончании вре- NieiiH, отведеинот с на обмег,, счетчик 2Ь 5),1рс |батывлет прерывание по тай- xf py в ЭВМ 1, Если необходимо увеличит, нремя обмена, з счетчик 26 ЭВМ 1 зяпис ыпаетг я новый код } ременно- г(1 интервала .

В режиме lljlll н:-1формапия передаетс под управлением устройства сопряжени из задпнш й области ОП ЭВМ - источик кп инфсрмгэци -; в за;;.анную область СП ЭВМ - приемника информагши. На- гравлегие пере дачи информации определяется разря. ю.м регистра 27 Направ- .:1е}-:ие обмена , к.оторый и определяет, какая ЭВМ - источ} ик, а какая - прием1{ик ичформпиии, Пе1)едача одного с .повл )орма1::ии состоит из двух LIKK , В первом цикле слово из ОП ЭВМ 1 источника ин(Ьо1)мации записывается в регистр 23,, р,о втором цикле из ре г кугра , 3 происхогП Гг затп-гсь Сотова в ОП ЭВМ 2 приемника И формации. На- ча.л)ные адреса массивов в ОП ЭВМ 1 и ОП ЭВМ 2 могут быть разными. Эти адреса ;и;ис1:.тпются в счетчики 24 н 2S соответстиенно,

ПоследователiiHocTb операций для задания устройству режима ГЩП сле- .гг:. ч1щая .

ЭВМ - чпдат гик формирует коман- .ау зглш ::и в тегистр 17 разряда За- , -:oTopbii-: б.иокируе : з;зпис; ана- ло Л1чно (1 Is регистр 18 и ол 4:) HHf через память 16 и при- e:-;:Miepe, 1,;;.тчик подклк чае гся на il ine i имфо1)мадип ;: ь агистрали 6, Слоду;(;щ--1 и кг)мян;:,ам1 ЭВМ 1 через при f ionepe, :а 1 чи : Ч записывает в счет- чили 2ч п 2S :;ачя.г; адреса ОП для Э-РЛ- : 1 - лсточнлка и ЭВМ 2 - приемника, i счетчик 26 з л гд СЬ вается дли- ч;1 пере;:;iBaeNuvo массива. Затем в ;){Ч истр 27 згтисынаются разряды ( жим r;Ul и Пачр;) вление обмена.

Разряд PP Режим ПЛП инициирует работу блока 22, который вырабатывает стандартные сигналы захвата маги- страле.й 5 и 8. После захвата маг и- стралей блок 22 управляет через память 16 работой устройства в первом и втором циклах перезаписи информаци Разряд РР Направление обмена оцре- деляет в какую ЭВМ будет сформцро- ван первый цикл и в какую - второй.

При передаче информации из ОП ЭВМ 1 в ОП ЭВМ 2 последовательность работы блоков следующая.

Блок 22 через память 16 для фор- мирования адресной части цикла включает на прием информации с магистрали 6 приемопередатчик 19 и счетчик 24, одновременно формируя стандартные сигналы управления каналом на шине 7 управления.

После окончания адресной части цикла блок 22 через память 16 включает приемопередатчик 19 и регистр 23 на прием информации с магистра- ли 6 и записывает слово информации в

регистр 23. Таким образом, слово записывается из ОП ЭВМ 1 в регистр 23. После записи слова из ОП в регистр 23 блок 22 через память 16 . отключает приемопередатчик 19 от магистрали 6.

Во втором цикле блок 22 через память 16 включает на передачу в магистраль 9 приемопередатчик 20 и счет- чик 25, формируя при этом по шине 10 управления сигналы управления магистралью 8. Таким образом, формируется адресная часть цикла в ЭВМ 2. После окончания адресной части цик- ла счетчик 25 отключается от магистрали 12 блоком через па- мять 16. Включается на передачу регистр 23 на магистраль 9 через приемопередатчик 20о При этом блоком 22 формируются на шине 10 управления соответствующие сигналы управления магистралью. После окончания передачи одного слова содержимое счетчикой 24-26 изменяется на ±1 (2) и циклы повторяются. При обнулении счетчика 26 блок 22 заканчивает работу сбрасывает разряды РР Режим ПДП и Направление обмена и освобождает магистрали 5 и 8.

В режиме переключения шин устройство работает следующим образом.

Аналогично двум предьщущим режимам работы ЭВМ 1 заносится в ре

Qft1 2

гистр 17 разряд Занято, который через память 16 коммутирует приемопередатчик 19 на прием информации с магистрали 6.

По командам ЭВМ 1 в регистр 27 записывается разряд Режим работы ПП1, блок 21 подключается на трансляцию управляющих сигналов канала 7 в сигнал шины 13 управления. При записи информации во внешнее устройство приемопередатчик 19 работает на передачу информации с магистрали 6 в магистраль 12, При записи информации из внешнего устройства в ЭВМ 1 память 16 после адресной части цикла коммутирует приемопередатчик 19 на передачу информации с магистрали 12 в магистраль 6.

Работа под управлением ЭВМ 2 полностью аналогична.

Формула изобретени.я

1, Устройство для сопряжения двух микроэвм с общим внешним устройством, содержащее два дешифратора адреса, два регистра управляющих сигналов и состояния, регистр данных, два счетчика адреса, счетчик слов, блок управления прерыванием, блок управления прямым доступом к памяти, причем первая, вторая группы информационных входов-выходов блока управления прерыванием образуют группы входов-выходов устройства для подключения к первым группам управлякщих входов-выходов соответственно первой, второй микроэвм, группы разрешающих входов первого, второго дешифраторов адреса образуют группы входов устройства для подключения к группам управляющих выходов соответственно первой, второй микроэвм, первая,вторая группы информационных входов-выходов блока управления прямым доступом к памяти образуют группы входов- выходов устройства для подключения к вторым группам управляющих входов- выходов соответственно первой, вто рой микроэвм, группы информационных входов первого, второго дешифраторов адреса и группы информационных входов-выходов первого, второго регистров управляющих сигналов и состояния образуют соответственно группы входов и группы входов-выходов устройства для подключения к группам информационных входов-выходов

соответственно ПерВОИ, втор;;; МИК);- ЭВМ, при этом выход|)1 псргки С, пч-ор - го дешифраторов адрбн :а ;;оедии иы с входами задисн счит|1та чл соответственно первого и вторС ГО регк.стров управляющих сигналов и состояния, входы установки которых сое/хинешл соответственно с перным и вторым выходами блока управления npi ipbufa- нием, первый, HTopof ij тр(тий и ier- вертый, пятьш, тестой входы логического условия которого соединены с первым, вторым, третьим nHiJjcipNia- циoнны ш выходами соответственно вого и второго регистров управляющих сигналов и состояния, ин1|),-- онные входы которых соединен, с информационным выходом региспа данных, счетные входы первого, зторо- го счет-гиков адреса и счетчика с,ло1в соединены с первым ныхол,ом блока равлен ия прямым доступом к памяти, выход счетчика слов соединен с: вым входом логического условия ка управления прямь м доступом к ;:;з- мяти и седьмым входом логиче :: .(1 условия блока управления пре-,л, ем, о т л и ч а ю ui е е с я т ем, что, с делью расигирения функдион-п.кь- ных возможностей за счет обсспечо- ния режима переключения шин, в нег :- введены постоянная дамятт, программ управления, два приемопе11е; ;ггчика, регистр режимов, причем третья группа информационр{ых входов-Г Ь|Ходон блока управления прерыванием образует группу входов-выходов устройгт- ства для подключения к группе управляющих входов-выходов ofin;:M o Периферийного устройства, легшь группы информадионных пхо7до;- -г,ых.:1дов лервого;, второго приемо ередатчико1-5, г руппы информадиоши.к входов и Tii .ixo- дов регистра )х,. первого., второго счетчиков адреса, груггпь мационных входов сче1 чика сдов jie-- |:гистра режимов образуют г-руппу вхо- дов-вьгходов устройства j,ля подключения к группе инфор;- апионных вхо- дов-вьпсодов об дех о иерисрерийного уст зойства,, вторые груп(ы инфо-рмадион- пых входов-выходов первого, ;п оро- го приемопередатчик(гв образуют пы входов-выхо,дов устройства гшя подключения к г-руппам :информапионн,1х зходов-выходов соотвртс твенчо первой второй микроэвм, при этом пуппы выходов первого и втстрого дешифратоl)ii;j ajii i :а f I fT.nnt iii i n;vr U Tr твенис

( и BTi p-. .МИ a j p е (

РХСДОП г .10тои1 гп; памяти ро1 рамм управ. 1ен:- я, neimb -:, вторсп, третий адреснь е нхо,д|.: «v -npjof соедпшеШ) с (тответг тлегпк с: щ-орым, третьим четвертым выхо;. б.1:ока управления :рямьлм ,ЧС::С У U iM к , группа вь - ;о;:ов которо о соединена с третьей rpxnnoil п.;1, пходов постоянной 1 амяти гро1 рамм уг ра ления, первый, n rC jMUi ; ; ф;1рмяписч1нь;с: в()ходь: кото- jjoi; coe;..i- не lib с оо1 ветственно с ш о- , тро1 ьим г ходами лот ического ус- :1(1.ия 6j:riKa упра в.пения прямым доступом к пам.ктр-;, че1 вер . вход догиче- скоу С) ус довия которого соединен с пе-звым 1-:ь:ход(1М режимов, р.Т( 1ро-й у T peTiif Bbrxcjni которого сое- jiHi СЧ1Ы с врнно с четдвертым и пятым адресным - входами постоянной : :амяти ро рамм управления, шестой, ге.;:.ьмо a. ippc: иые входы которой со- едгпеп : ;.; первым - информап - онными п ходам 1 с ooTise тствс пш первого и аторсм о рег 1стрсв управдяюи их сигна- Л(П и сост(, информап - оп- П,;; ; В1 ХС Д пос гс яШ О памяти программ уп;-ав.пс пя cn(;i nii:H с управдяюшими 1ход;1М 1 и siTopoi o пр емопе- ре ;а гч1п с;, четвертый информашюнный ттос т ояп1-с й 1амяти программ уп- р:1: де п1я гоед,пнен с входами записи- ) ре Д С1 ра да нных, регист- ра режимспв, первого, второго счетчи- ког адреса, счетчике слов, 1ятый, i :ecToii, се.дьмст; иьчформадионнряе выхо- ;д ПОСТС1Я амятк дрограмм управ- . coe:niHe i.i соответственно с нсгпмь м. .девять М5 дес:ятым входами ло tnrnecKoro ycjuiBiiH б.г ока удравления прс рь ва ;ием.

-; ,-1 н; Ц с- е с я тем, что блок управления 1прер1-1иан :ем содержит гег, uiecTb перед., два приемо- 1 е5 ед.ат1 ика 5 одл ов.ибратор , два элемента H- fiE, лва э.ремента ИЛИ, элемент И три - .пеме гга И-ИЛИ, элемент И-ИЛИ- НЕ,, .)Ормап -;онвые выходы i ei niorO; третьего тередат- -ij-ir OB, ;нфо ;м;пп;п ные входь первого np -;eMont реда Г -П ка., первый вход пер- элс;ме - та И-И.МИ образуют ервую г-руп у информапион п,1х входов-выходов С- ЛО ча управления 7рсрыванием, инфор- MarnioHHbie {плхидуя че 1 нертогс., пятого j :i:efToro перед;г: чикс;р, -;нфор --1апио 1ные

Bxcijuii второгп приемопар .-датчика , второй РХ(1Д перп(1го элемента И-И.ПИ образуют вторую группу ипформаплонных входов-выходов блока управления прерыванием, информационные выходы первого, второго приемопередатчиков, информационные входы третьего, шестого передатчиков образуют третью группу информадаонных входов-выходов блока управления прерыванием, выходы первого, второго элементов ИЛИ являются первым, вторым выходами блока управления пре1)ыванием соответственно, первые разрешающие входы первого, второго приемопередатчиков образуют группу разрешающих входов блока управления прерыванием, первый вход второго элемента И-ИЛИ соединен с первым входом третьего элемента И-ИЛИ, с первым входом элемента И-ИЛИ-НЕ, с третьим входом пе-рвого элемента И-ИЛИ, с вторым разрешающим входом первого приемопередатчи-. ка, с управляющими входами третье- ,го, четвертого, пятого передатчиков, с первым входом первого элемента ИЛИ и является первым входом логического условия блока управления прерыванием, второй вход второго эле мента И-ИЛИ, второй, третий входы третьего элемента И-ИЛИ, третий вход второго элемента И-ИЛИ являются соответственно вторым, третьим, четвертым, пятым входами логического условия блока управления прерыванием, четвертый вход второго элемента И-ИЛИ соединен с четвертым входом третьего элемента И-ИЛИ, с вторым входом элемента И-ИЛИ-НЕ, с четвертым входом первого элемента И-ИЛИ, с вторым разрещающим входом второго приемопередатчика, с разрешающим входом первого, второго, шестого передатчиков, с первым входом второго элемента ИЛИ и является щестым входом логического условия блока управления . прерыванием, вход одновиб- ратора, третий и четвертый входы

элемента И-ИЛИ-НЕ, первые разрешающие входы первого, второго приемопередатчиков являются соответственно седьмым, восьмым, девятым и десятым входами логического условия блока уп-

райления прерыванием, при этом в бло-gg выходы первого, второго, третьего,

четвертого, девятого, десятого пет редатчиков и информационный вход первого приемника образуют первую групцу информационных входов-выходо

ке управления прерыванием выходы второго, третьего элементов И-ИЛИ соединены с первым и вторым входами первого элемента И-НЕ, выход которого

соединен с информационным входом триггера,единичный выход которого соединен с первым входом элемента И, выход которого соединен с первым информационным входом первого передатчика и с первым информационным входом четвертого передатчика, второй информационный вход которого, соединен с вторым информационным входом первого передатчика, с нулевьм выходом триггера, с первым входом второго элемента И-НЕ, выход которого соединен с первым, вторым инфор- мационны входами второго передатчика, с вторыми входами первого, второго элементов ИЛИ, с первым, вторым информационными входами пятого передатчика, третий информационный вход которого соединен с выходом одновибратора и с третьим информационным входом второго передатчика, выход первого элемента И-ИЛИ соединен с вторыми входами элемента И и второго элемента И-НЕ, вьтод элемента И-ИПИ-НЕ соединен с синхровходом триггера.

3. Устройство по П.1, о т л и зоg

35 t

0

0

чающееся тем, что блок управления прямым доступом к памяти содержит регистр сдвига, десять триггеров, элемент И, два приемника, двенадцать передатчиков, причем пер- вьм вход элемента И соединен с нулевыми входами первого, второго триггеров и является первым входом логического условия блока управления прямым доступом к памяти, разрешающий вход первого передатчика соединен с разрешающими входами второго, третьего, четвертого передатчиков и является вторым входом логического условия блока управления прямым доступом к памяти, разрещающий вход пятого передатчика соединен с разре- тающими входами шестого,седьмого, восьмого передатчиков и является третьим входом логического условия блока управления прямым доступом к памяти, синхровход третьего триггера соединен с синхровходом четвертого триггера и является четвертым вхо- дом логического условия блока управления прерыванием, информационные

выходы первого, второго, третьего,

четвертого, девятого, десятого пет редатчиков и информационный вход первого приемника образуют первую групцу информационных входов-выходов

блока управления прямым догтуис м к памяти, информапд ониые зьгхо,чы пятс - го, шестого, седьмого, восьмого, одиннадцатого, двенадкатог о передатчиков и информационный вход второго приемника образуют вторую rpyiiny информационных входов-выход,ов Одска управления прямым доступом к тмяти первый вькод регистра сдвига спеди- нен со своим информационные входом и является первЕ)1м выходом блока управления прямым доступом к памятг:, выход шестого триггера является БТСГ рым выходом блока управления прямым доступом к памяти, вькод элемеггга И соединен с входом разрешения сдвига регистра сдвига и является третьим выходом блока управления прямьм доступом к памяти, единичный выход шестого триггера является четвертым выходом блока управления прямым доступом к памяти, второй выход регистра сдвига и нулевой выход шестого триггера образуют группу выходов блока управления прямым доступом к памяти, при этом в блоке управления прямым доступом к памяти информационый выход первого приемнике, соедике с нулевым входом четвертого тригтер и с единичным входом второго тркг-- гера, вькод которого соединен с информационным входом десятого передатчика и с вторым входом злемекта И, третий вход которог о соединен с информационным входом: двенадцатого передатчика и с выходом первого триггера,единичный вход которого соединен с информационным выходом второго приемника и с нулевым входом третьего триггера, выход которого соединен с информационным входом

5

(VUI гП1 ллиатого .,т -чнкп 5 ныхсд чет- Г.(ФТ О1Ч Т ггср.ч с |Г, :, с инфС р- мапионнь м вх(1Д,(м ;1Г15ят(1Г о поредат- ика, -ретий иыхо;. регистра сдвига гпединея с единичным пятого iinrrepa, нулряой гход кот(ро1 о со- едине} с едияич :ым вхо,;;ом седьмого Tjrnrrep.a и с четг-иг-ртым выходом ре- г (fCTpa сдвиг а, viHTbis i выход, которого соединен с еи и к :нъгм входог восьмого триггера, нулевой вход которого соединен с нулевым входом седьмого трр-rrrepG и с ныходсм регистра сдвига, седьмой выход которого соединен с единичньлм входом шестого триггера, нулевой вход которого соединен с восьмым выходом регистра сдвига,, девятый выход которого соединен с е,диничным нходом де;зятого тригге1)а5 улеБой узход которого соединен с нулевым входом десятого триггера и с десятым выходом регистра сдвига, о,циь:надиатр,1й ВЬЕСОД которого соединен с единичным входом десятого триг гера,, выход которого соединен с информационными входами четвертого и восьмого передатчиков, информационные входы третьего п се,дьмого передатчиков соединены с вьжодом дer: lтorc триггера,., инфор- мйиионг:ые входы второго и шестого передатчиков соединень с выходом восьмого триггера, информационные входы первого к пятого передатчиков сое,ди- нень с выходом седьмого триггера информационнь е входы третьего и четвертого тригг сров подключены к шине е;линичг:ого потенгтиала устройства, тйктовь й вход, регистра сдвига является тгкговым вхдом блока управления прямым доступом к памяти.

Редактор И.Касарда

Состатавитель Л.Пестмал

Техред Л.Сердюкова КорректорМ.Максимишинец

Заказ 4922/48 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многомашинных вычислительных систем на базе микроэвм с общей шиной. Целью изобретения является расширение функциональных возможностей за счет обеспечения режима переключения шин. Устройство содержит блок управления прерыванием, блок управления прямым доступом к памяти, постоянную память программ управления, два дешифратора адреса, два регистра управления и состояния, два приемопередатчика, регистр данных, два счетчика адреса, счетчик слов, регистр режимов. 2 з.п. ф-лы, 5 ил. S (Л с о: 42 О to

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мячев А.А | |||

| Организация управляющих вычислительных комплексов | |||

| М.: Энергия, 1980, с.227. | |||

Авторы

Даты

1987-10-15—Публикация

1985-11-10—Подача