длительности импульсов данных и интервалов между ними. В цикле загрузки данные подаются по входу 22 в блок 9 памяти, импульс сопровождения по входу 24 через элемент ИЛИ 3 запускает распределитель 5 импульсов, сигналы которого обеспечивают управление адресным счетчиком 4 и блоком 9 памяти. В режиме вывода данных, который задается по входу 23 устройства, данные переписываются из блока 9 памяти в регистр 14. Данные содержат коды информации, длительности выходных импульсов и интервалов между выводимыми единицами информации. Коды проверяются по четности блоком 15, который включает счетчик 10

с помощью триггера 7. Счетчик 10 вырабатывает коды, которые сравниваются с соответствующими кодами регистра 14 блоками 17 и 18 сравнения. Блок 17 управляет триггером 20 и через коммутатор 21 обеспечивает выдачу данных из регистра 14 во внешнее устройство. Блок 18 сравнения через мажоритарный элемент 19, выполняющий функцию формирователя импульса, отключает счетчик 10. После вывода всего массива данных дешифратор 6 включает триггер 8, который отключает распределитель 5 импульсов, обнуляет через элемент И 11 счетчик 4, регистр 14, и устройство возвращается в исходное состояние. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для считывания информации с перфоносителя | 1986 |

|

SU1388914A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Многоканальное устройство для сбора и обработки информации | 1988 |

|

SU1524078A1 |

| Адаптивное устройство для приема информации с групп рассредоточенных объектов | 1990 |

|

SU1837346A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления обменом информацией между каналами Ввода-вывода и периферийными устройствами. Цель изобретения - расширение области применения устройства. В устройстве реализованы цикл загрузки и цикл вывода данных с возможностью изменения 16 з Ё Х| м ihO CJ 4 i4)

Изобретение относится к вычислительной технике и может быть использовано для управления обменом информацией между каналами ввода-вывода и периферийными устройствами.

Цель изобретения - расширение области применения за счет обеспечения формирования изменения длительности сигналов выводимой информации и интервалов между ними.

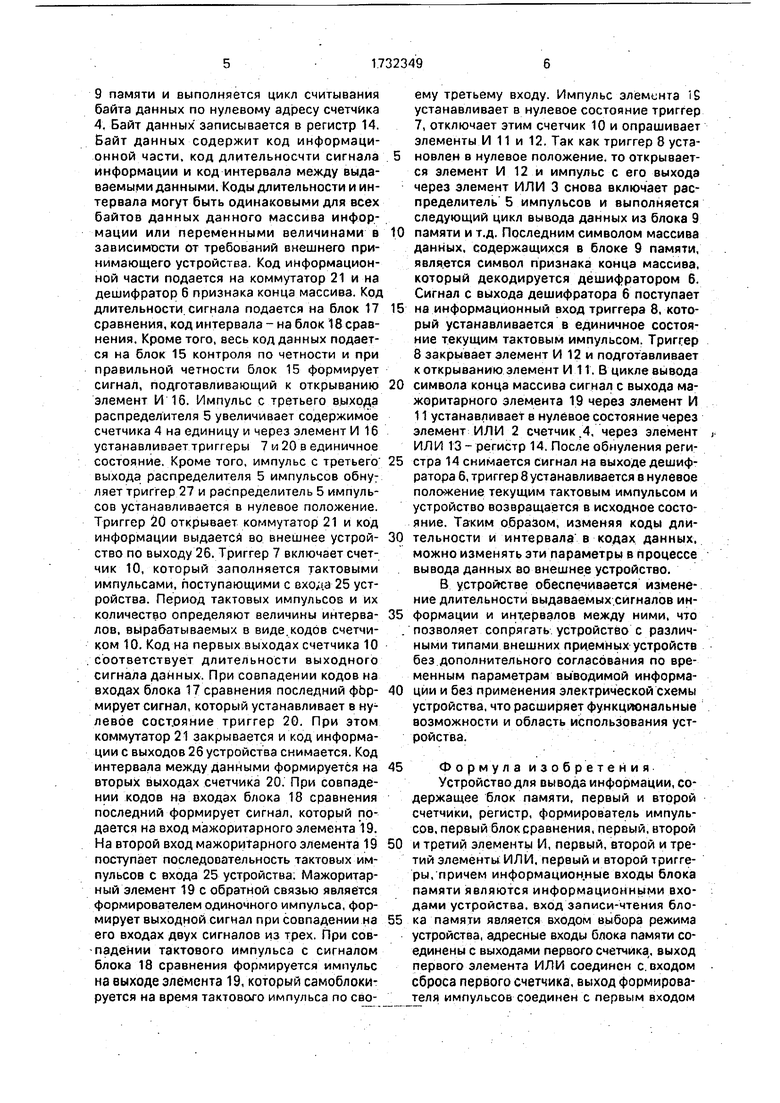

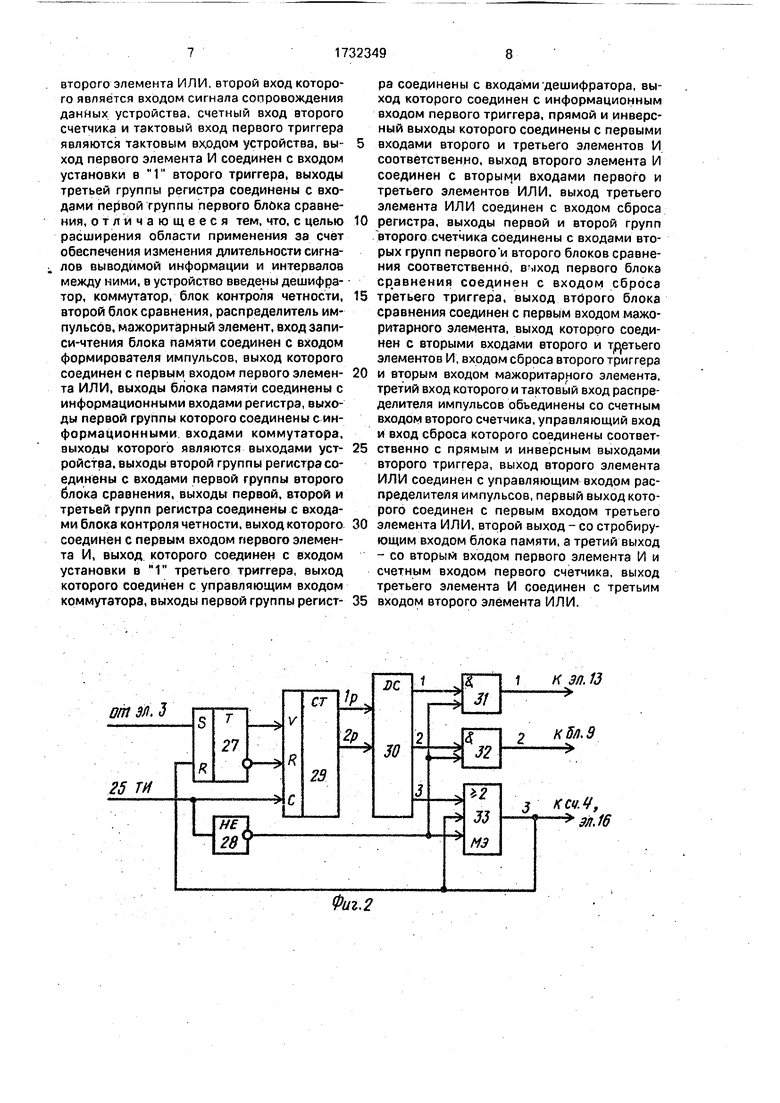

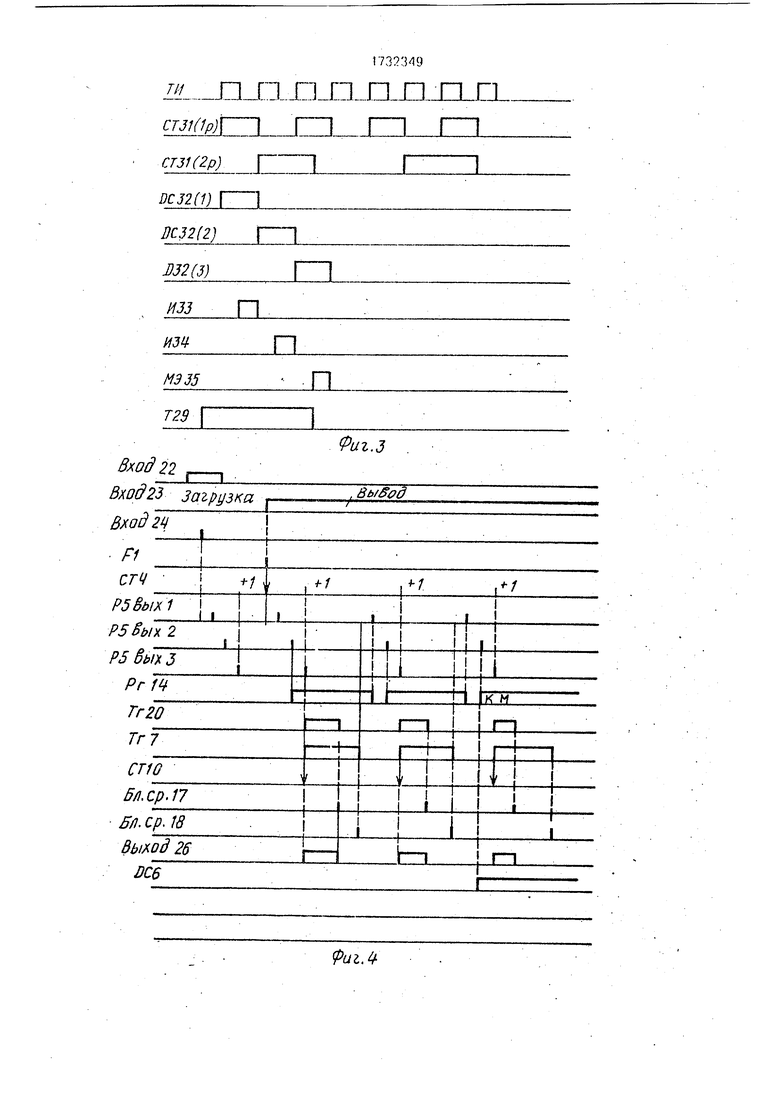

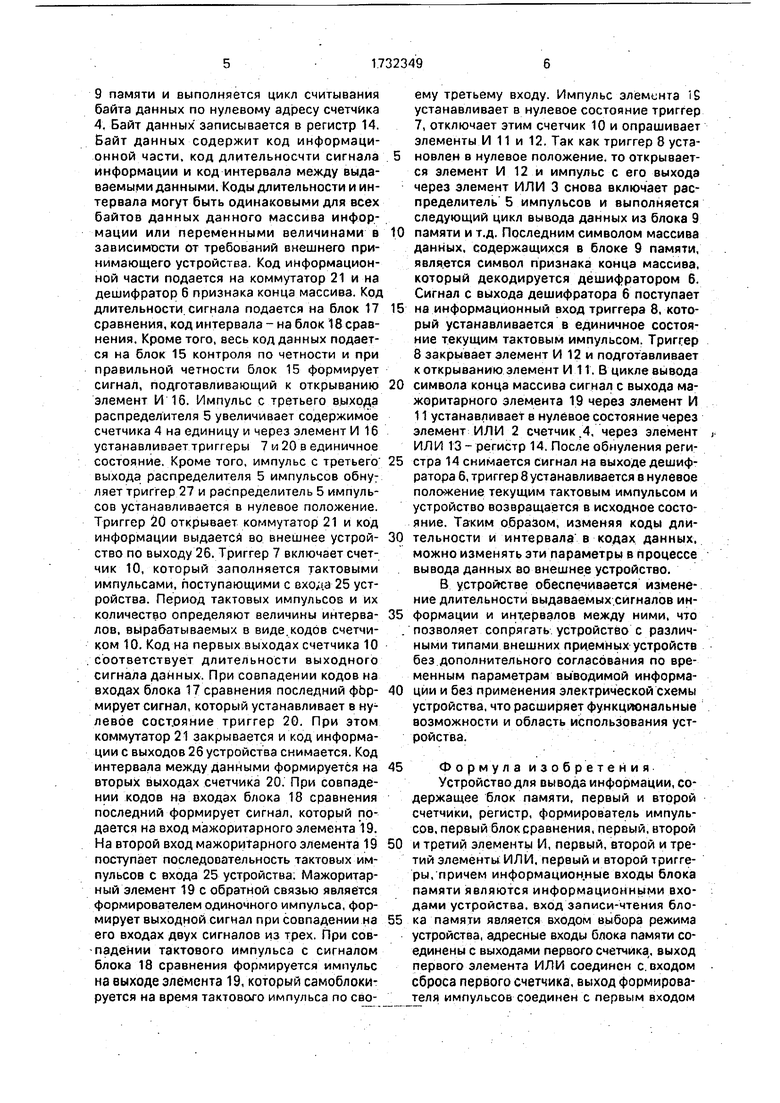

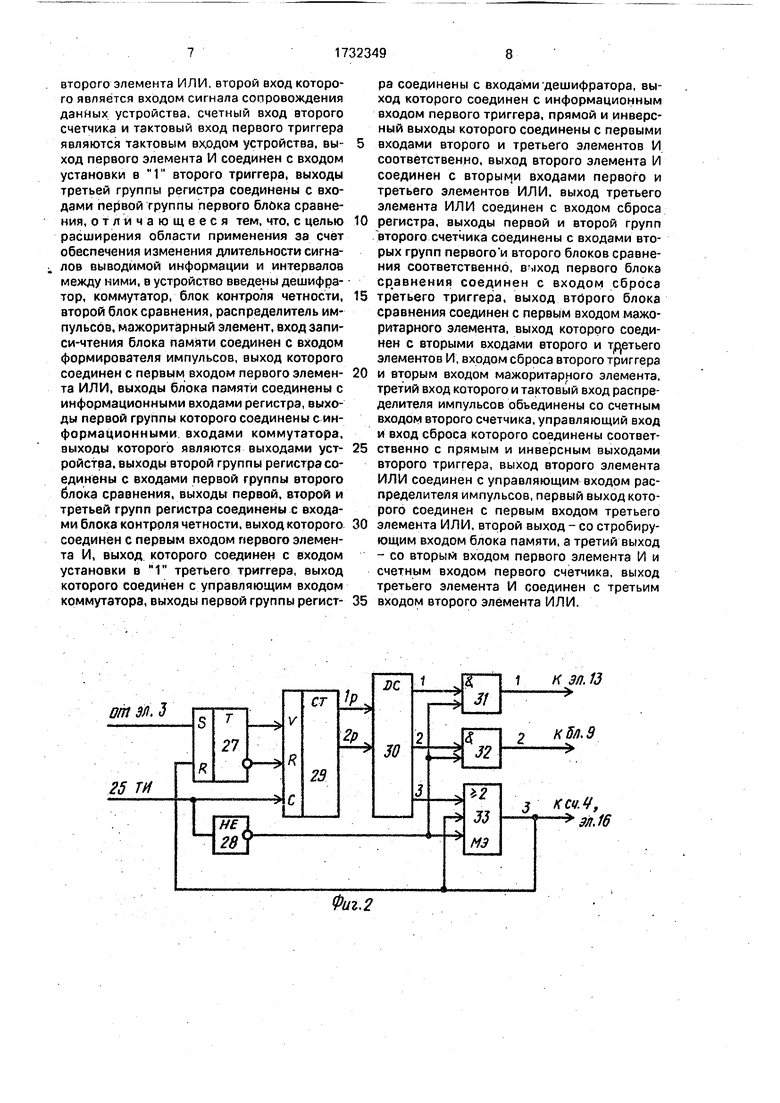

На фиг. 1 приведена блок-схема устройства; на фиг, 2 - схема распределителя импульсов; на фиг. 3 - временная диаграмма работы распределителя импульс г-. на фиг, 4 - временная диаграмма работы устройства.

Устройство содержит формирователь 1 импульсов, первый и второй элементы ИЛИ 2 и 3, первый счетчик 4, распределитель 5 импульсов, дешифратор 6, второй и первый триггеры 7 и 8, блок 9 памяти, второй счетчик 10, второй и третий элементы И 11 и 12, третий элемент ИЛИ 13, регистр 14, блок 15 контроля по четности, первый элемент И 16, первый и второй блоки 17 и 18 сравнения, мажоритарный элемент 19, третий триггер 20, коммутатор 21, информационные входы 22, вход 23 выбора режима, вход 24 импульсов сопровождения данных, вход 25 тактовых импульсов, выходы 26 устройства.

Распределитель 5 импульсов (фиг. 2) содержит триггер 27, элемент НЕ 28, счетчик 29, дешифратор 30, элементы И 31 и 32, мажоритарный элемент 33.

Устройство работает следующим образом.

В исходном положении счетчик 4, триггеры 7, 8 и 20, регистр 14 и триггер 27 распределителя 5 импульсов установлены в нулевое положение (цепи начальной установки не схеме не показаны). В процессе

работы устройства выполняется цикл загрузки и цикл вывода данных. Цикл загрузки задается по входу 23 устройства потенциальным сигналом низкого уровня. Данные

по входу 22 .поступают на информационные входы блокз 9 памяти, импульс сопровождения данных по входу 24 через элемент ИЛИ 3 запускает распределитель 5 импульсов. В последнем срабатывает триггер 27, который разрешает счет тактовых импульсов в счетчике 29. Состояния счетчика 29 декодируются дешифратором 30, сигналы с выходов которого селектируются через элементы И 31, и 32 и мажоритарный элемент 33 инверсным тактовым импульсом. Мажоритарный элемент 33 с обратной связью формирует импульс, который обнуляет триггер 27 и цикл работы распределителя импульсов заканчивается (фиг, 4). За один цикл распределитель импульсов формирует три импульса на своих выходах. Импульс с первого выхода в цикле загрузки не используется. Импульс с второго выхода распределителя импульсов 5 обеспечивает запись данных в

блок 9 памяти по адресам, задаваемым счетчиком 4. Приращение адресов в счетчике 4 обеспечивается импульсом с третьего выхода распределителя 5 импульсов. По окончании цикла загрузки внешнее устройство

задает по входу 23 режим вывода данных потенциальным сигналом высокого уровня. По фронту этого сигнала формирователь 1 формирует импульс, который через элемент ИЛИ 2 устанавливает счетчик 4 в нулевое

состояние и через элемент ИЛИ 3 включает распределитель 5 импульсов. Импульс с первого выхода распределителя 5 импульсов через элемент ИЛИ 13 устанавливает регистр 14 в нулевое состояние. Импульс с

второго выхода распределителя 5 импульсов подается на стробирующий вход блока

9 памяти и выполняется цикл считывания байта данных по нулевому адресу счетчика 4. Байт данных записывается в регистр 14. Байт данных содержит код информационной части, код длительносчти сигнала информации и код интервала между выдаваемыми данными. Коды длительности и интервала могут быть одинаковыми для всех байтов данных данного массива информации или переменными величинами в зависимости от требований внешнего принимающего устройства. Код информационной части подается на коммутатор 21 и на дешифратор 6 признака конца массива. Код длительности сигнала подается на блок 17 сравнения, код интервала - на блок 18 сравнения. Кроме того, весь код данных подается на блок 15 контроля по четности и при правильной четности блок 15 формирует сигнал, подготавливающий к открыванию элемент И 16. Импульс с третьего выхода распределителя 5 увеличивает содержимое счетчика 4 на единицу и через элемент И 16 устанавливает трип еры 7 и 20 в единичное состояние. Кроме того, импульс с третьего выхода распределителя 5 импульсов обнуляет триггер 27 и распределитель 5 импульсов устанавливается в нулевое положение. Триггер 20 открывает коммутатор 21 и код информации выдается во внешнее устрой- ство по выходу 26. Триггер 7 включает счетчик 10, который заполняется тактовыми импульсами, поступающими с 25 устройства. Период тактовых импульсов и их количество определяют величины интерва- лов, вырабатываемых в виде кодов счетчиком 10. Код на первых выходах счетчика 10 соответствует длительности выходного сигнала данных. При совпадении кодов на входах блока 17 сравнения последний фор- мирует сигнал, который устанавливает в нулевое состояние триггер 20. При этом коммутатор 21 закрывается и код информации с выходов 26 устройства снимается. Код интервала между данными формируется на вторых выходах счетчика 20. При совпадении кодов на входах блока 18 сравнения последний формирует сигнал, который подается на вход мажоритарного элемента 19. На второй вход мажоритарного элемента 19 поступает последовательность тактовых импульсов с входа 25 устройства. Мажоритарный элемент 19 с обратной связью является формирователем одиночного импульса, формирует выходной сигнал при совпадении на его входах двух сигналов из трех. При совпадении тактового импульса с сигналом блока 18 сравнения формируется импульс на выходе элемента 19, который самоблокируется на время тактового импульса по своему третьему входу. Импульс элемента IS устанавливает в нулевое состояние триггер 7, отключает этим счетчик 10 и опрашивает элементы И 11 и 12. Так как триггер 8 установлен в нулевое положение, то открывается элемент И 12 и импульс с его выхода через элемент ИЛИ 3 снова включает распределитель 5 импульсов и выполняется следующий цикл вывода данных из блока 9 памяти и т.д. Последним символом массива данных, содержащихся в блоке 9 памяти, является символ признака конца массива, который декодируется дешифратором 6. Сигнал с выхода дешифратора 6 поступает на информационный вход триггера 8, который устанавливается в единичное состояние текущим тактовым импульсом. Триггер 8 закрывает элемент И 12 и подготавливает к открыванию элемент И 11. В цикле вывода символа конца массива сигнал с выхода мажоритарного элемента 19 через элемент И 11 устанавливает в нулевое состояние через элемент ИЛИ 2 счетчик.4. через элемент ИЛИ 13 - регистр 14. После обнуления регистра 14 снимается сигнал на выходе дешифратора 6, триггер 8 устанавливается в нулевое положение текущим тактовым импульсом и устройство возвращается в исходное состояние. Таким образом, изменяя коды длительности и интервала в кодах данных, можно изменять эти параметры в процессе вывода данных во внешнее устройство.

В устройстве обеспечивается изменение длительности выдаваемых сигналов информации и интервалов между ними, что позволяет сопрягать устройство с различными типами внешних приемных устройств без дополнительного согласования по временным параметрам выводимой информации и без применения электрической схемы устройства, что расширяет функциональные возможности и область использования устройства.

Формула изобретения Устройство для вывода информации, содержащее блок памяти, первый и второй счетчики, регистр, формирователь импульсов, первый блок сравнения, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ, первый и второй триггеры, причем информационные входы блока памяти являются информационными входами устройства, вход записи-чтения блока памяти является входом выбора режима устройства, адресные входы блока памяти соединены с выходами первого счетчика, выход первого элемента ИЛИ соединен с входом сброса первого счетчика, выход формирователя импульсов соединен с первым входом

второго элемента ИЛИ, второй вход которого является входом сигнала сопровождения данных устройства, счетный вход второго счетчика и тактовый вход первого триггера являются тактовым вхрдом устройства, выход первого элемента И соединен с входом установки в 1 второго триггера, выходы третьей группы регистра соединены с входами первой группы первого блика сравнения, отличающееся тем, что, с целью расширения области применения за счет обеспечения изменения длительности сигналов выводимой информации и интервалов между ними, в устройство введены дешифратор, коммутатор, блок контроля четности, второй блок сравнения, распределитель импульсов, мажоритарный элемент, вход записи-чтения блока памяти соединен с входом формирователя импульсов, выход которого соединен с первым входом первого элемента ИЛИ, выходы блока памяти соединены с информационными входами регистра, выходы первой группы которого соединены с информационными входами коммутатора, выходы которого являются выходами устройства, выходы второй группы регистра соединены с входами первой группы второго блока сравнения, выходы первой, второй и третьей групп регистра соединены с входами блока контроля четности, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом установки в 1 третьего триггера, выход которого соединен с управляющим входом коммутатора, выходы первой группы регистФиг. 2

ра соединены с входами-дешифратора, выход которого соединен с информационным входом первого триггера, прямой и инверсный выходы которого соединены с первыми

входами второго и третьего элементов И соответственно, выход второго элемента И соединен с вторыми входами первого и третьего элементов ИЛИ. выход третьего элемента ИЛИ соединен с входом сброса

регистра, выходы первой и второй групп второго счетчика соединены с входами вторых групп первого и второго блоков сравнения соответственно, вмход первого блока сравнения соединен с входом сброса

третьего триггера, выход второго блока сравнения соединен с первым входом мажоритарного элемента, выход которого соединен с вторыми входами второго и третьего элементов И, входом сброса второго триггера

и вторым входом мажоритарного элемента, третий вход которого и тактовый вход распределителя импульсов объединены со счетным входом второго счетчика, управляющий вход и вход сброса которого соединены соответственно с прямым и инверсным выходами второго триггера, выход второго элемента ИЛИ соединен с управляющим входом распределителя импульсов, первый выход которого соединен с первым входом третьего

элемента ИЛИ, второй выход - со стробиру- ющим входом блока памяти, а третий выход - со вторым входом первого элемента И и счетным входом первого счетчика, выход третьего элемента И соединен с третьим

входом второго элемента ИЛИ.

HL ГЛ„Г1Г П. MIILJCIL

СТ31(2р)

.1

icjgf/j I 1

DC32(2)

J)32(3)

1

m

ИЗЗ

П

ИЗЦn

МЭ35

n

/Z.J

Вход 22

Вход23 Загрузка Вход 24

Р1

I

1

, 8ь/Ј0о

| Устройство для вывода информации | 1982 |

|

SU1043618A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 4656548, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-07—Публикация

1989-07-11—Подача