XI

CJ

|Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении диагностируемых систем. Цель изобретения - сокращение аппаратурных затрат устройства. При подаче сигнала запуска на вход 13 устройства на регистр 2 через коммутатор 1 переписывается контролируемое число с информационного входа 21 устройства, а на регистр 3 - модуль контроля со входа 22 устройства. Блоки сравнения группы 4 сравнивают содержимое регистра 2 (выход 14) с содержимым регистра 3 (выход 15), умноженным на 2, где 1 j k (k - число блоков в группе 4). В блоках вычита

ЧЭ

ьия группы 6 происходит вычисление разноси и между содержимым регистра 2 и содержимым регистра 3, умноженным на 2J. Выходы 18 блоков 6 вычитания поступают на входы мультиплексора 7, который управляется выходом 17 дешифратора 12, пропускающим на выход 19 мультиплексора 7 наименьшую разность между содержимым регистров 2 и 3. Эта наименьшая разность через коммутатор 1 записывается снова в регистр.

Изобретение относится к вычислительной технике и может быть использовано при поиi роении диагностируемых систем.

Цепь изобретения - сокращение аппаратурных затрат устройства.

На фиг. 1 приведена функциональная схема устройства; на фиг, 2. 3 - примеры реализации мультиплексоре) и дешифратора.

Устройство (фиг. 1) содержит коммута- 1, регистры 2 и 3, группу блоков 4 сравнения, блок 5 сравнения, группу блоков б вычитания, мультиплексор 7, группу элементов И 8, элемент НЕ 9, элемент И 10, генератор 11 тактовых импульсов, дешиф- ратор 12, вход 13 запуска устройства, выходы 14, 15 первого и второго регистров 2 и 3 соответственно, выходы 16 блоков 4 сравнения группы, выход 17 дешифратора 12, выходы 18 блоков б вычитания группы, выход (9 мультиплексора 7, информационный выход 20 устройства, информационный вход 21 устройства, вход 22 задания модуля контроля устройства, элемент ИЛИ 23,

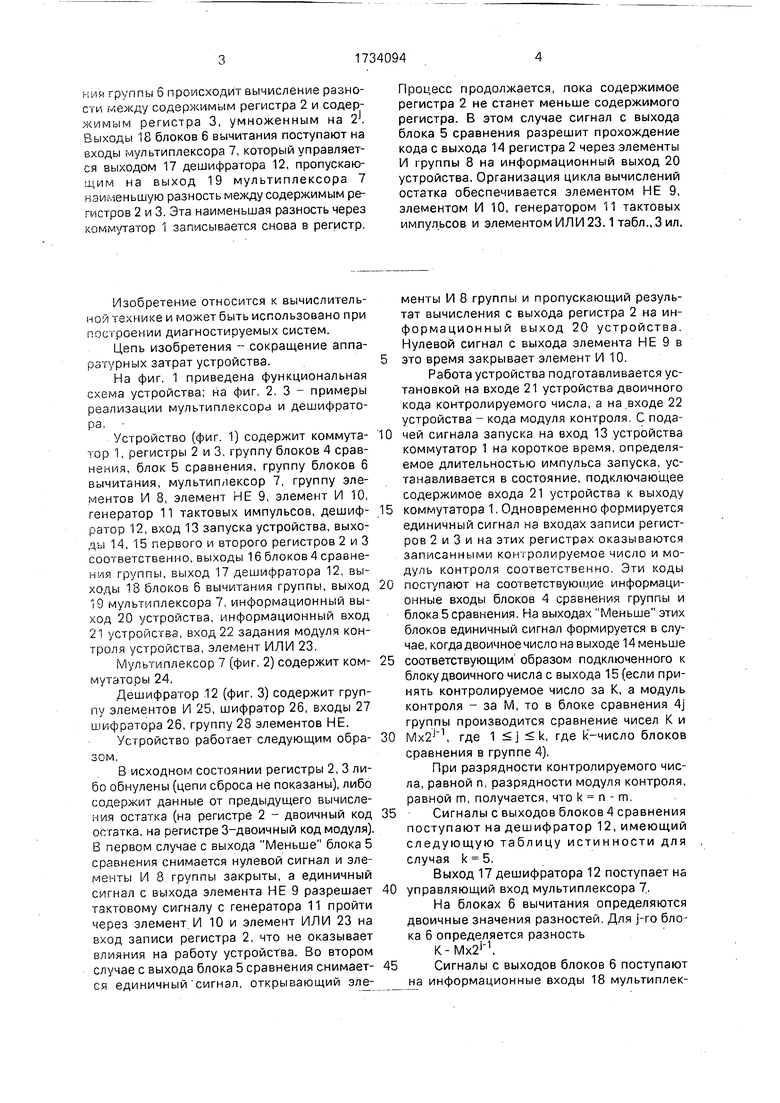

Мультиплексор 1 (фиг. 2) содержит ком- мутаторы 24.

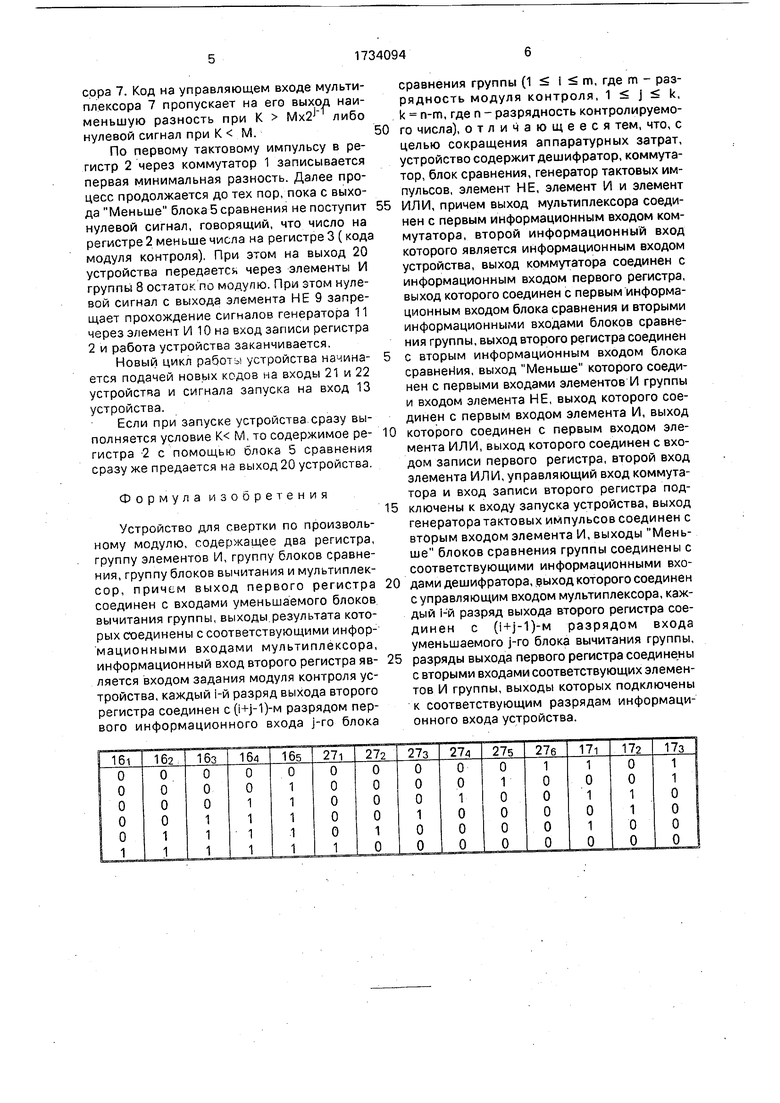

Дешифратор 12 (фиг, 3) содержит группу элементов И 25, шифратор 26, входы 27 шифратора 26, группу 28 элементов НЕ.

Устройство работает следующим обра-

3QM,

В исходном состоянии регистры 2, 3 либо обнулены (цепи сброса не показаны), либо содержит данные от предыдущего вычисления остатка (на регистре 2 - двоичный код остатка, на регистре 3-двоичный код модуля) В первом случае с выхода Меньше блока 5 сравнения снимается нулевой сигнал и элементы И 8 группы закрыты, а единичный сигнал с выхода элемента НЕ 9 разрешает тактовому сигналу с генератора 11 пройти через элемент И 10 и элемент ИЛИ 23 на вход записи регистра 2, что не оказывает влияния на работу устройства. Во втором случае с выхода блока 5 сравнения снимает- ся единичный сигнал, открывающий элеПроцесс продолжается, пока содержимое регистра 2 не станет меньше содержимого регистра. В этом случае сигнал с выхода блока 5 сравнения разрешит прохождение кода с выхода 14 регистра 2 через элементы И группы 8 на информационный выход 20 устройства. Организация цикла вычислений остатка обеспечивается элементом НЕ 9, элементом И 10, генератором 11 тактовых импульсов и элементом ИЛИ 23.1 табл., 3 ил.

менты И 8 группы и пропускающий результат вычисления с выхода регистра 2 на информационный выход 20 устройства. Нулевой сигнал с выхода элемента НЕ 9 в это время закрывает элемент И 10.

Работа устройства подготавливается установкой на входе 21 устройства двоичного кода контролируемого числа, а на входе 22 устройства - кода модуля контроля С подачей сигнала запуска на вход 13 устройства коммутатор 1 на короткое время, определяемое длительностью импульса запуска, устанавливается в состояние, подключающее содержимое входа 21 устройства к выходу коммутатора 1. Одновременно формируется единичный сигнал на входах записи регистров 2 и 3 и на этих регистрах оказываются записанными кожролируемое число и модуль контроля соответственно. Эти коды поступают на соответствующие информационные входы блоков 4 сравнения группы и блока 5 сравнения. На выходах Меньше этих блоков единичный сигнал формируется в случае, когда двоичное число на выходе 14 меньше соответствующим образом подключенного к блоку двоичного числа с выхода 15 (если принять контролируемое число за К, а модуль контроля - за М, то в блоке сравнения 4j группы производится сравнение чисел К и Mx2J, где 1 j k, где k-число блоков сравнения в группе 4),

При разрядности контролируемого числа, равной п, разрядности модуля контроля, равной т, получается, что k п - т.

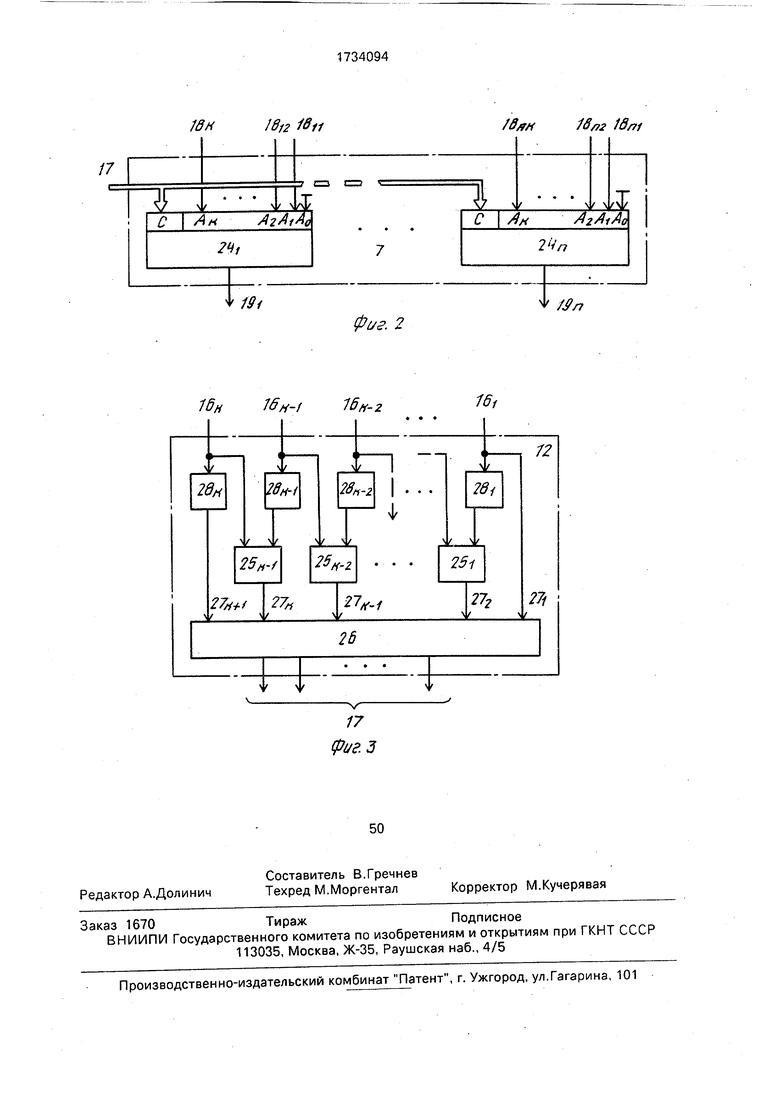

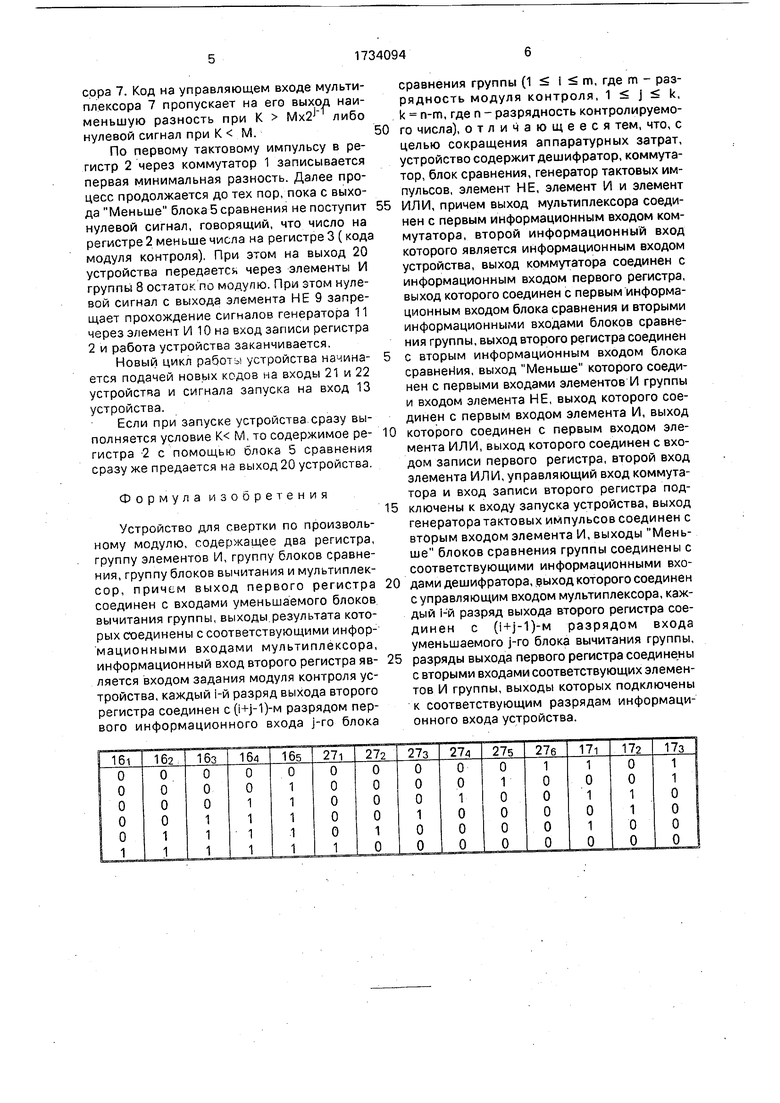

Сигналы с выходов блоков 4 сравнения поступают на дешифратор 12, имеющий следующую таблицу истинности для случая k 5.

Выход 17 дешифратора 12 поступает на управляющий вход мультиплексора 7.

На блоках 6 вычитания определяются двоичные значения разностей. Для j-ro блока 6 определяется разность

К-Мх2н.

Сигналы с выходов блоков 6 поступают на информационные входы 18 мультиплексора 7. Код на управляющем входе мультиплексора 7 пропускает на его выход наименьшую разность при К Мх2 либо нулевой сигнал при К М.

По первому тактовому импульсу в регистр 2 через коммутатор 1 записывается первая минимальная разность. Далее процесс продолжается до тех пор, пока с выхода Меньше блока 5 сравнения не поступит нулевой сигнал, говорящий, что число на регистре 2 меньше числа на регистре 3 (кода модуля контроля). При этом на выход 20 устройства передается через элементы И группы 8 остаток по модулю. При этом нулевой сигнал с выхода элемента НЕ 9 запрещает прохождение сигналов генератора 11 через элемент И 10 на вход записи регистра 2 и работа устройства заканчивается.

Новый цикл работ о1 устройства начинается подачей новых кодов на входы 21 и 22 устройства и сигнала запуска на вход 13 устройства.

Если при запуске устройства сразу выполняется условие К М, то содержимое регистра 2 с помощью блока 5 сравнения сразу же предается на выход 20 устройства.

Формула изобретения

Устройство для свертки по произвольному модулю, содержащее два регистра, группу элементов И, группу блоков сравнения, группу блоков вычитания и мультиплексор, причем выход первого регистра соединен с входами уменьшаемого блоков вычитания группы, выходы результата которых соединены с соответствующими информационными входами мультиплексора, информационный вход второго регистра является входом задания модуля контроля устройства, каждый i-й разряд выхода второго регистра соединен c(i+j-1)-M разрядом первого информационного входа j-ro блока

сравнения группы (1 i m, где m - разрядность модуля контроля, 1 j к, k n-m, где п - разрядность контролируемо0 го числа), отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит дешифратор, коммутатор, блок сравнения, генератор тактовых импульсов, элемент НЕ, элемент И и элемент

5 ИЛИ, причем выход мультиплексора соединен с первым информационным входом коммутатора, второй информационный вход которого является информационным входом устройства, выход коммутатора соединен с информационным входом первого регистра, выход которого соединен с первым информационным входом блока сравнения и вторыми информационными входами блоков сравнения группы, выход второго регистра соединен

с вторым информационным входом блока сравнения, выход Меньше которого соединен с первыми входами элементов И группы и входом элемента НЕ, выход которого соединен с первым входом элемента И, выход

0 которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом записи первого регистра, второй вход элемента ИЛИ, управляющий вход коммутатора и вход записи второго регистра под5 ключены к входу запуска устройства, выход генератора тактовых импульсов соединен с вторым входом элемента И, выходы Меньше блоков сравнения группы соединены с соответствующими информационными вхо0 дами дешифратора, выход которого соединен с управляющим входом мультиплексора, каждый i-й разряд выхода второго регистра соединен с (i+j-1)-M разрядом входа уменьшаемого j-ro блока вычитания группы,

5 разряды выхода первого регистра соединены с вторыми входами соответствующих элементов И группы, выходы которых подключены к соответствующим разрядам информационного входа устройства.

1вНJ6}2 18ц

16н1б#-116к-2

17

Фие.з

/8/гн 18л1

фиг. 2

16l

| Устройство для формирования остатка по произвольному модулю от числа | 1986 |

|

SU1401463A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для свертки по произвольному модулю | 1987 |

|

SU1509903A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-15—Публикация

1990-02-19—Подача