Изобретение относится к области вычислительной техники, в частности к устройствам умножения, и может быть использовано при построении ариф метических устройств электронных вычислительных машин.

(«

Цель изобретения - повышение быстродействия .

На фиг.1-4 изображена схема устройства; на фиг.5 - алгоритм получения частичных произведений, одинаковых по весу.,

Устройство для умножения содержит n-разрядный сдвиговый регистр 1 множителя, n-разрядный сдвиговый регистр

2 множимого, | -разрядный сдвиговый . управляющий регистр 3, Ј групп трех- входовых элементов И 4 из четырех,

двенадцати, соответственно, 4(п-1) элементов И 4, группу элементов ИЛИ 5

из четырех входовых, восьми (я- - 1)(«Ј-Ј

.

входовых, соответственно, восьми двух- входовых элементов ИЛИ, первый полусумматор 6,(2п-4) основных сумматоров. 7, второй полусумматор 8, элемент ИЛИ

9,(2п-4) дополнительных сумматоров

10,третий полусумматор 11, 2п-раз- рядный регистр 12 результата, информационные входы 13-16 устройства, установочный вход 17 устройства.

Устройство для умножения работает следующим обра зом.

В исходном состоянии регистры 1, 2,3 и 12 обнулены.

Множитель А аг,..,ап,

а«/гИ° ап} последовательно подается на первый и третий входы

со

СП

00 4ь N3

устройства, причем на первый вход,

п начиная с я-то разряда, а на третий

вход, начиная с (я- + 1)-го разряда,

Одновременное множимое В Ъ,, bac00 b,, , .„.bnj

bt- V

последовательно подается на второй и четвертый входы устройства, приче на второй вход, начиная с я--го разряда, а на четвертый вход, начиная

/п . „ с (г + 1)-то разряда,

В первом такте одновременно с мнжителями на установочный вход устройства поступает единичный сигнал, который записывается в первый разп

ряд г-разрядного сдвигового управляющего регистра.

В каждом такте одновременно с записью разрядов множимого и множител в n-разрядном сдвиговом регистре 1 множителя и n-разрядном сдвиговом регистре 2 множимого происходит сдвиг информации на один разряд,

причем в г старших разрядах происходит сдвиг информации в направлении от n-гго к ( + О-му разряду, а в

младших разрядах происходит сдвиг информации в направлении от первого

п к Я--МУ разряду.

Сигнал с выхода старшего разряда n-разрядного сдвигового,регистра 1 множителя поступает на входы перво-/ го и т/4 первых четных трехвходовых элементов И 4 первой 4.1, второй

4.2, соответственно, j-й 4„п/2 групп

а сигнал с выхода первого разряда этого регистра поступает на входы

m последнего и т последних нечетных

трехвходовых элементов И 4 первой 4.1, второй 4.2, соответственно,

п „ , п

г-и 4,г групп

Сигнал с выхода старшего разряда n-разрядного сдвигового регистра 2 множимого поступает на входы.

(г + 1) первых нечетных трехвходовых

На выходах элементов И 4 первой 55 группы 4.1.1, 4.1.2, 4.1.3, 4.1.4 сформируются компоненты первого ча

г . ем ты первого ча элементов И 4 первой 401, второй 4,2 тичного произведения а Ь а Ъ

« П ПТйг тг Z1

соответственно, г-й 4«г групп, а сига Ч

Ъ Ъ 2 Ј

гг. г

ап Ь„ „ На основных Ъ f

нал с выхода первого разряда этого регистра поступает на входы (т + О

, последних четных трехвходовых элементов И 4 первой 4„1, второй 4.2, соответственно, г-и 4.к- групп.

Сигнал с выхода первого разряда

tO --разрядного сдвигового управляющего регистра 3 поступает на входы трех- входовых элементов И 4 первой группы 40Ы, 4.1.2, 4.1,3, 40104, сиг,5 нал с выхода второго разряда этого регистра поступает на входы трехвходовых элементов 4 второй группы 4.2.1, 4.2.2...4.2,12, соответствен20

но, сигнал с выхода JTO разряда

п

-разрядного сдвигового управляющего регистра 3 поступает на входы трехвходовых элементов И 4 г-группы 25 4-jH, 4-Ј-2„о.4.2.(4п - 4).

В результате на выходах элементов И 4 первой, второй, соответственно, п „ .

г-и групп формируются в каждом такте- 30 2

компоненты частичных произведении, причем в одном такте формируются не более двух одинаковых по весу компонент.

В первом такте в первый разряд 35 n-разрядного сдвигового регистра 1 множителя будет записано значение (г + Ото разряда а п множитедя А,

а в n-й разряд - значение s-то раз- 0

ряда а„ множителя А. Одновременно

1

в первый разряд n-разрядного сдвигового регистра 2 множимого будет за- 5 писано значение (яг + 1)-го разряда

Ьп множимого В, а в n-й разряд п

значение Разряда bn множимого В„ При этом в первый разряд г-раз- 02

рядного сдвигового управляющего регистра будет записано единичное значение.

На выходах элементов И 4 первой 5 группы 4.1.1, 4.1.2, 4.1.3, 4.1.4 сформируются компоненты первого час г . ем ты первого ча тичного произведения а Ь а Ъ

г . ем ты тичного произведения а

Тйг

а Ч

Ъ

г

ап Ь„ „ На Ъ f

сумматорах 7 и дополнительных сумматорах 10 они просуммируются с промежуточным значением суммы частичных произведений (в первом такте ее значение нулевое), и результат в виде первой промежуточной суммы записывается в 2п-раэрядный регистр 12 результата.

Во втором такте одновременно со сдвигом информации в первый разряд п-разрядного сдвигового регистра 1 множителя будет записано значение

(я- + 2)-го разряда ая множителя А

п

а в n-й разряд - значение (г - 1)го

разряда а у, . множителя А. Одновре f. менно в первый разряд п-разрядного

сдвигового регистра 2 множимого будет записано значение (- + 2)-го

разряда Ъг, множимого В, а в п-й

а42- п разряд - значение (j - 1)-го разряда

Ъ„ множимого В. При во второй

разряд n-разрядного сдвигового управляющего регистра 3 будет записано единичное значение.

На выходах элементов И второй группы Jf.2.1, A,2..,,....12 сформируются компоненты второго частичноя

ного произведения а„( Чп,

22

Ьп

-1 ; J

а„ Ь,

,. - h . а п . 2 г.

Ј +

%-«

u+2 aU42Di-, °|

. г т г г. г

af., Ь

а|Ъ%+г ai+2b| + i af + i Ь|+г

а§+гЬй

На основных 7 и дополнительных 10 сумматорах эти компоненты суммируются вместе с первой промежуточной суммой частичных произведений, и результат в виде второй промежуточной суммы записывается в 2п-разряд- ный регистр 12 результата.

В i-м такте одновременно со сдви- гом информации, в первый разряд п40

45

На основных 7 и дополнительны 10 сумматорах, полусумматорах 6, и 11 и с помощью элемента ИЛИ 9 поненты 1-го частичного произвед суммируются со значениями (i-1)- 35 промежуточной суммы. В п-разряд регистра 12 результата записывае значение i-й промежуточной суммы

о П

В тактб одновременно со гом информации в первый разряд п рядного сдвигового регистра 1 мн жителя будет записано значение с шего разряда а.4 множителя А, в п разряд - значение младшего разря ап множителя А. Одновременно в п вый разряд n-разрядного сдвигово регистра 2 множимого будет записа значение старшего разряда Ь множ го Б, а в n-й разряд - значение м

разрядного сдвигового регистра 1 мно- 50 шего разряда Ъп множимого В. При жителя будет записано значение ( +

Ото разряда а„ . множителя А, в

Ъ п n-й разряд - значение ( - i + 1)-го

55

этом в r-и разряд г -разрядного с гового управляющего регистра 3 бу записано единичное значение. На выходах элементов И k г-и

разряда ай . множителя А. Одновременно в первый разряд п-разрядного сдвигового регистра 2 множимого будет

записано значение (г + i)-ro разряда i

Ь , множимого В, а в n-й разряд

значение (г - i + 1).-го разряда

Ь„ . множимого В„ При этом в 1-й

5-41 п

разряд г-разрядного сдвигового управляющего регистра 3 будет записано единичное значение.

На выходах элементов И k i-й группы 4.1.1, 4.1.2..,4.1 (8 (i-1) + 4) сформируются компоненты 1-го частичного произведения

5

,.

aa.u,

20

25

bn

3f-U3

bn

аЛ.-Ы0|-и5

-aH

|+;

Т.

Ъ

и-1

Ьп

-i4Z

i-Ui a§-i }- а b|4; . au + ;ba.; + 3

30

J

40

45

4+iH f :

На основных 7 и дополнительных 10 сумматорах, полусумматорах 6,8 и 11 и с помощью элемента ИЛИ 9 компоненты 1-го частичного произведения суммируются со значениями (i-1)-и 35 промежуточной суммы. В п-разрядный регистра 12 результата записывается значение i-й промежуточной суммы.

о П

В тактб одновременно со сдвигом информации в первый разряд п-разрядного сдвигового регистра 1 множителя будет записано значение старшего разряда а.4 множителя А, в п-й разряд - значение младшего разряда ап множителя А. Одновременно в первый разряд n-разрядного сдвигового регистра 2 множимого будет записано значение старшего разряда Ь множимого Б, а в n-й разряд - значение млад50 шего разряда Ъп множимого В. При

шего разряда Ъп множимого В. При

этом в r-и разряд г -разрядного сдвигового управляющего регистра 3 будет записано единичное значение. На выходах элементов И k г-и

группы .|-1, 4.S2... 4,|-(4п-4)

п

сформируются компоненты я--го частич15

ого произведения a«bt, а, агЪ4,разряда (1

,b,,a5b, . ...a,b.|t а„Ь,, а,Ь ,

л Ь ,. „.,,.,, , an,b,, a,bn anb,, , a2bn, anbs, a,bn.. .anbn. ,- 5

an Ьи с ,« anbfl 2, , апЬп„

На основных 7 дополнительных 10

сумматорах, полусумматорах 6,8 и 11 Ю и с помощью элемента ИЛИ 9 компоненты я--то частичного произведения суммируются вместе со значениями (г - 1)й промежуточной суммы частичных произведений, и значение результата записывается в 2п-разрядный регистр 12 результата, причем в младший его разряд записывается значение сигнала с выхода элемента И 4

--и групп (4п-4), сформировавшего компоненту частичного произведения ahbf,. В результате работы устройства на 2п-разрядном регистре 12 результата оудет находиться окончательное значение произведения.

В таблице даны номер разряда регистра результата и формируемые компоненты частичных произведений.

ход суммы д j-ro разряд с входом jрегистра ре

20

выход j-ro соответстве новного сум ход суммы в динен с вхо разрядного ды третьего разряда кот ственно с п сумматоров

(р - f 3

суммы основ

О-го разря дом дополн

25 п + 2

разрядов и регистров м единены соо вторым инфо ройства, о тем, что, с

30

.-

+ 1 ... 2п-2), выход суммы дополнительного сумматора j-ro разряда соединен соответственно с входом jro разряда 2п-разрядного

регистра результата (j

, п, 4...7),

выход j-ro разряда которого соединен соответственно с первым входом основного сумматора j-ro разряда, выход суммы второго полусумматора соединен с входом второго разряда 2п- разрядного регистра результата, выходы третьего разряда и каждого р-го разряда которого соединены соответственно с первыми входами основных сумматоров третьего и р-го разрядов

(р - f 3 .

п

n + S- 1),

(п + 22 - /, выход суммы основного сумматора

О-го разряда соединен с первым входом дополнительного сумматора

п + 2 го РазРяДа, входы п-х

разрядов и n-разрядных сдвиговых регистров множителя и множимого соединены соответственно с первым и вторым информационными входами устройства, отличающееся тем, что, с целью повышения быстро

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1444755A1 |

| Устройство для умножения | 1989 |

|

SU1654815A1 |

| Устройство для умножения | 1989 |

|

SU1658148A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для умножения последовательных двоичных кодов | 1987 |

|

SU1495786A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

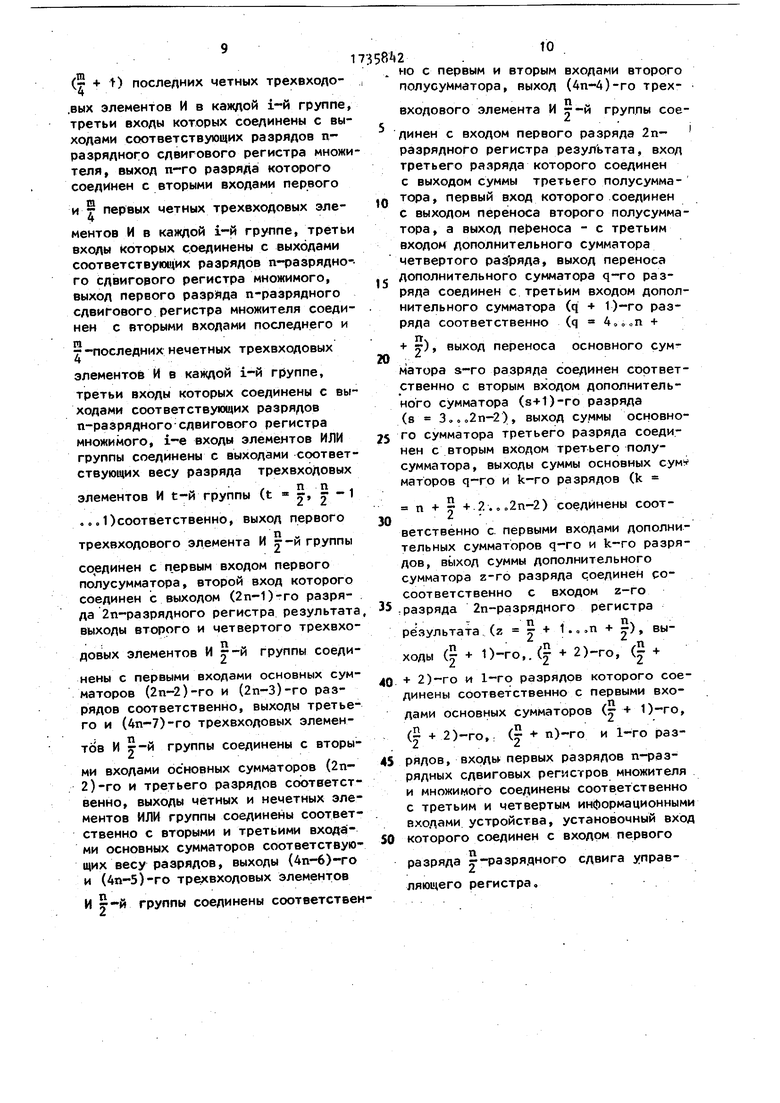

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств электронных вычислительных машин. Цель изобретения - повышение быстродействия о Новым в устройстве, содержащем n-разрядный сдвиговый регистр множителя, n-разрядный сдвиговый регистр 2 множимого, три полусумматора, элемент ИЛИ, (2п-4) основных сумматоров, (2п-4) дополнительных сумматоров, 2п-разрядный регистр результата, является введение п/2- разрядного сдвигового управляющего регистра, п/2 групп трехвходовых элементов И и группу элементов ИЛИ, что позволило формировать в каждом такте не более двух частичных произведений одного веса разрядов и уменьшить время суммирования частичных произведений. 1 табл., 5 ил

Формула изобретения

Устройство для умножения, содержащее n-разрядные сдвиговые регистры множимого и множителя (п - разрядность сомножителей, четное), элемент ИЛИ, три полусумматора (2п-4) основных сумматоров разрядов, (2п-4) дополнительных сумматоров разрядов и 2п-разрядный регистр результата, причем выходы переноса и суммы первого полусумматора соединены соответственно с первыми входами элемента ИЛИ и первого дополнительного сумматора , (2п-1)-го разряда, выход переноса которого соединен с вторым входом элемента ИЛИ, выход которого соединен с входом 2п-го разряда. 2п-разрядного регистра результата, вход R-ro разряда которого соединен соответственно с выходом суммы дополнительного сумматора R-го разряда

(R п + | + 1,.,2п - 1), выход пе-

реноса дополнительного сумматора 1-го разряда соединен с третьим входом дополнительного сумматора (1-1)

п

действия, в него введены г-разрядный

сдвиговый управлящий регистр, п/2 групп трехвходовых элементов И (из ,12.. ,Мп-1) элементов И, группа эле5

ментов ИЛИ (из четырех s -входовых, восьми

(2 D-входовых

восьми двухвхо0 довых элементов ИЛИ), причем первые входы трехвходовых элементов И в каждой i-й группе объединены и соединены соответственно с выходом 1-го разряда п/2-разрядного сдвигового управляа

ющего регистра,

1 2)

° «2 /

ВЫХОД

5

0

n-го разряда n-разрядного сдвигового регистра множимого соединен с вторы1)

ми входами

первых нечетных

трехвходовых элементов И в каждой i-й группе (т - число трехвходовых элементов И в соответствующей группе) третьи входы которых соединены с выходами соответствующих разрядов n-разрядного сдвигового регистра множителя, выход первого разряда п-раз- рядного сдвипового регистра множимого соединен с вторыми входами

ЛЧ

(- + t) последних четных трехвходо,вых элементов И в каждой i-й группе, третьи входы которых соединены с выходами соответствующих разрядов п- разрядного сдвигового регистра множителя, выход п-то разряда которого соединен с вторыми входами первого

и т первых четных трехвходовых элементов И в каждой i-й группе, третьи входы которых соединены с выходами соответствующих разрядов п-разрядно-- го сдвигового регистра множимого, выход первого разряда п-разрядного сдвигового регистра множителя соединен с вторыми входами последнего и

т -последних нечетных трехвходовых

элементов И в каждой i-й группе,

третьи входы которых соединены с выходами соответствующих разрядов n-разрядного сдвигового регистра множимого, 1-е входы элементов ИЛИ группы соединены с выходами соответствующих весу разряда трехвходовых

элементов И t-й группы (t

...1)соответственно, выход первого

трехвходового элемента И т-и группы

соединен с первым входом первого полусумматора, второй вход которого соединен с выходом (2п-1)-го разряда 2п-разрядного регистра результата выходы второго и четвертого трехвходовых элементов И г-и группы соединены с первыми входами основных сумматоров (2п-2)-го и (2п-3)-го разрядов соответственно, выходы третьего и (4п-7)-го трехвходовых элементов И г-и группы соединены с вторыми входами основных сумматоров (2п- 2)-го и третьего разрядов соответственно, выходы четных и нечетных элементов ИЛИ группы соединены соответственно с вторыми и третьими входами основных сумматоров соответствующих весу разрядов, выходы (4п-6)-го и (4п-5)-го трехвходовых элементов

И г-и группы соединены соответственп п 2 J -т

0

, но с первым и вторым входами второго полусумматора, выход (4п-4)-го трехвходового элемента И --и группы сое- с

динен с входом первого разряда 2п-

разрядного регистра результата, вход третьего разряда которого соединен с выходом суммы третьего полусумма0 тора, первый вход которого соединен с выходом переноса второго полусумматора , а выход переноса - с третьим входом дополнительного сумматора четвертого раз ряда, выход переноса

ц дополнительного сумматора q-го разряда соединен с третьим входом дополнительного сумматора (q + 1)-го разряда соответственно (q 4„0,п +

Пч

+ выход переноса основного сумматора s-ro разряда соединен соответственно с вторым входом дополнительного сумматора (з-И)-го разряда (s 3,„о2п-2), выход суммы основно- 5 го сумматора третьего разряда соединен с вторым входом третьего полусумматора, выходы суммы основных сум-г маторов q-ro и k-го разрядов (k

п + г + 2..о2п-2) соединены соответственно с первыми входами дополнительных сумматоров q-ro и k-ro разрядов, выход суммы дополнительного сумматора z-ro разряда соединен со- соответственно с входом z-ro разряда 2п-разрядного регистра

результата (z + 1.. п + -), выходы (| + О-го,. (j + 2)-го, (| +

+ 2)-го и 1-го разрядов которого соединены соответственно с первыми входами основных сумматоров (s- + 1)-го,

0

5

0

+ 2)-го,

/П

(j + П)-ГО

и 1-го раз

рядов, входы- первых разрядов п-раз- рядных сдвиговых регистров множителя и множимого соединены соответственно с третьим и четвертым информационными входами устройства, установочный вход которого соединен с входом первого

п

разряда -разрядного сдвига управляющего регистра.

Номер такта

2п

Номер) разряда регистра результата и формируемые компонента частичных произведений;

-Г | 2п-2 |2п-3 | 2п-4 | .- |л+ j +2 jn + | +1 j n + n + | +1 j.- n + 3 jn + 2 jn + 1 j n

п , 2

а,Ь,

п 2

a,b, afbs

-I -f1

2

Л an

а «-,

CO

vn

CO

J

a,bs-.

a bnan b an bn

5 §-. |« |

an .bn art b. an bn

a b ХЛ an Dn

п -1 Т уТ-уГГуТ-уГПТ-У 7 7 2 Т Т

anb4 anb, anbV. -ianVj anb -f anb +4 a,,aflbn.,

anbn

a2bn a,bnanbna bna b,a bft ,,an.,bn(

an-.N an-.N an-,bsV,,an-bnan-,b| an-, % a.b,,.,3

г tCO

а,Ьй., a4bn.t

25 Z2

i«b« .. „.

+4 f,2

a| ba.tai «4 -: -17-l

anbn

CM

4

I

Г

21

глазей

17358 2

Јt

-j . e-l T I I

Л Ж ДУЦ. i - - /$Goujab fs/jy/ /s0y

/f ffOU/fSJti Jl/C twufiffj

Авторы

Даты

1992-05-23—Публикация

1989-04-18—Подача