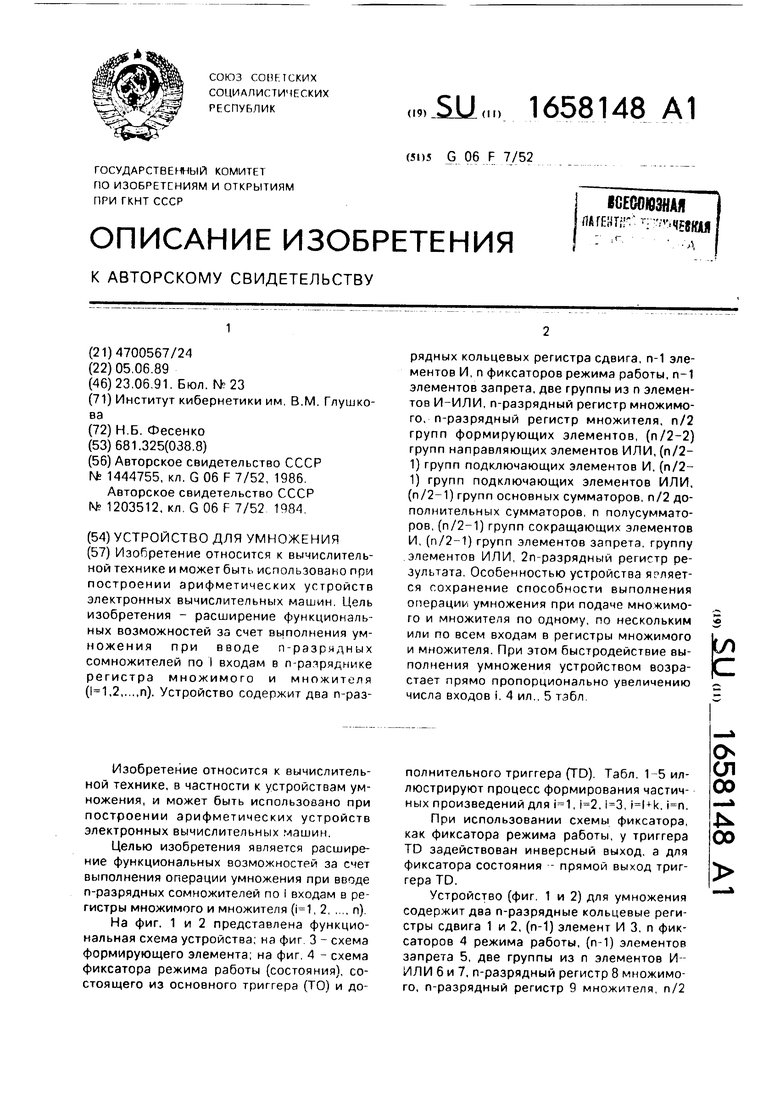

Изобретение относится к вычислительной технике, в частности к устройствам умножения, и может быть использовано при построении арифметических устройств электронных вычислительных машин.

Целью изобретения является расширение функциональных возможностей за счет выполнения операции умножения при вводе n-разрядных сомножителей по I входам в регистры множимого и множителя (, 2, . , п)

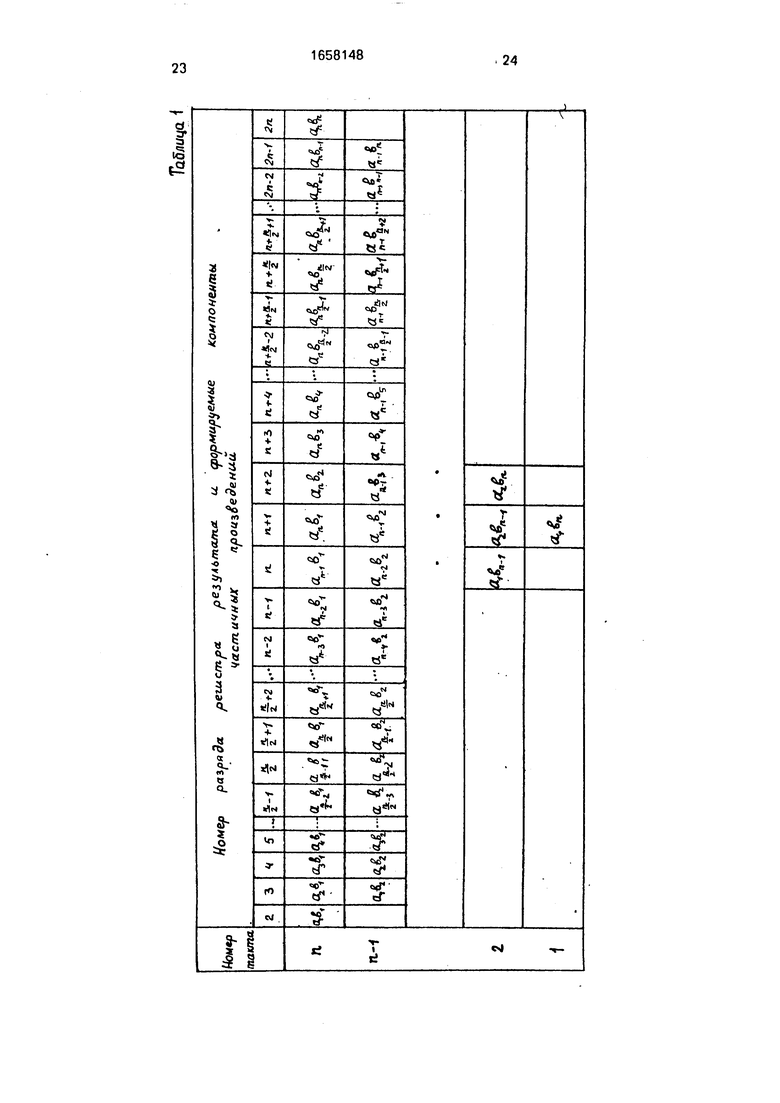

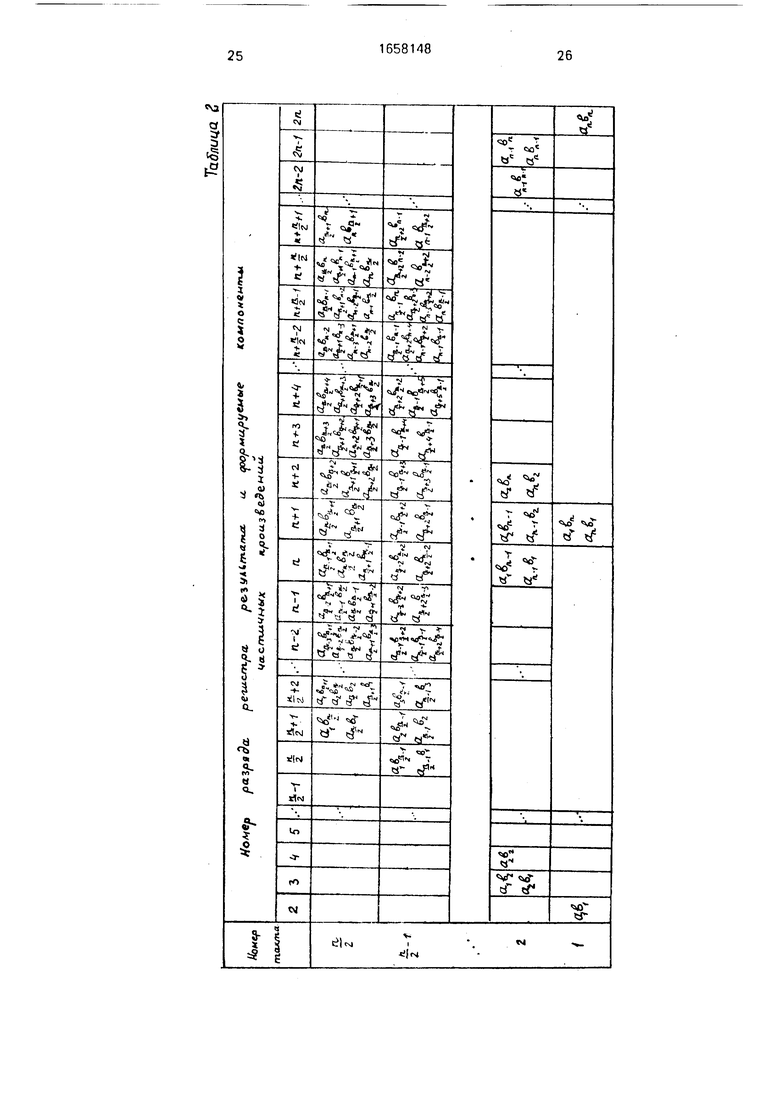

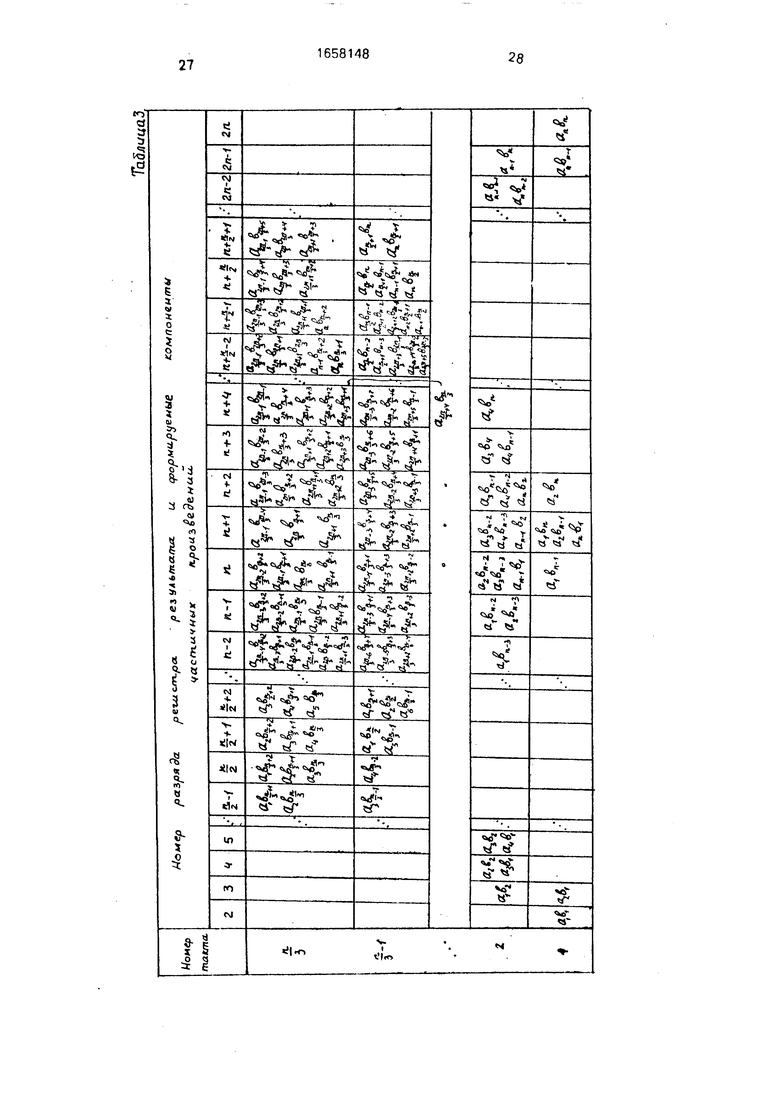

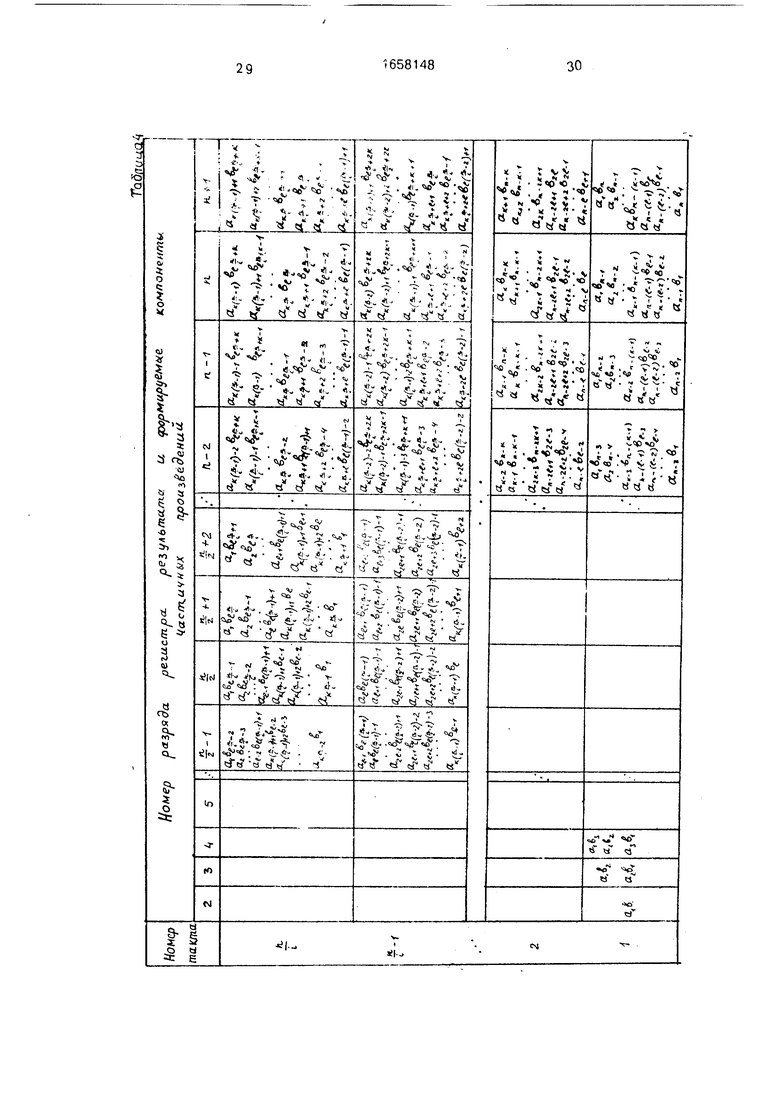

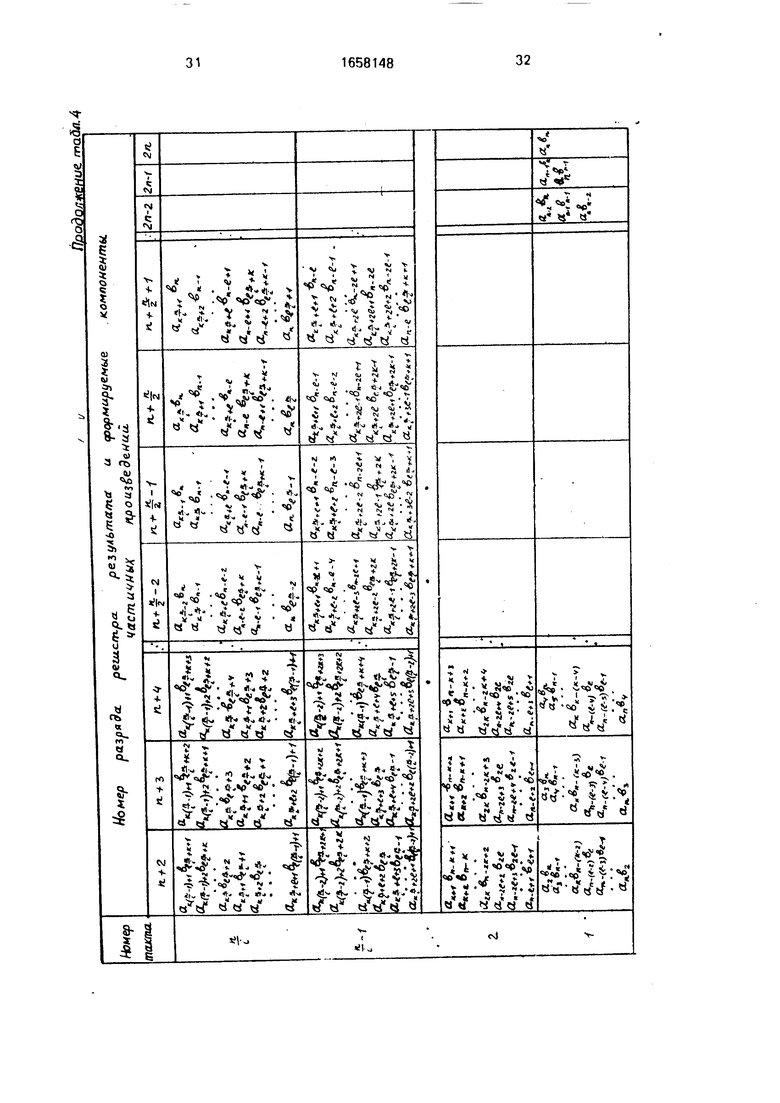

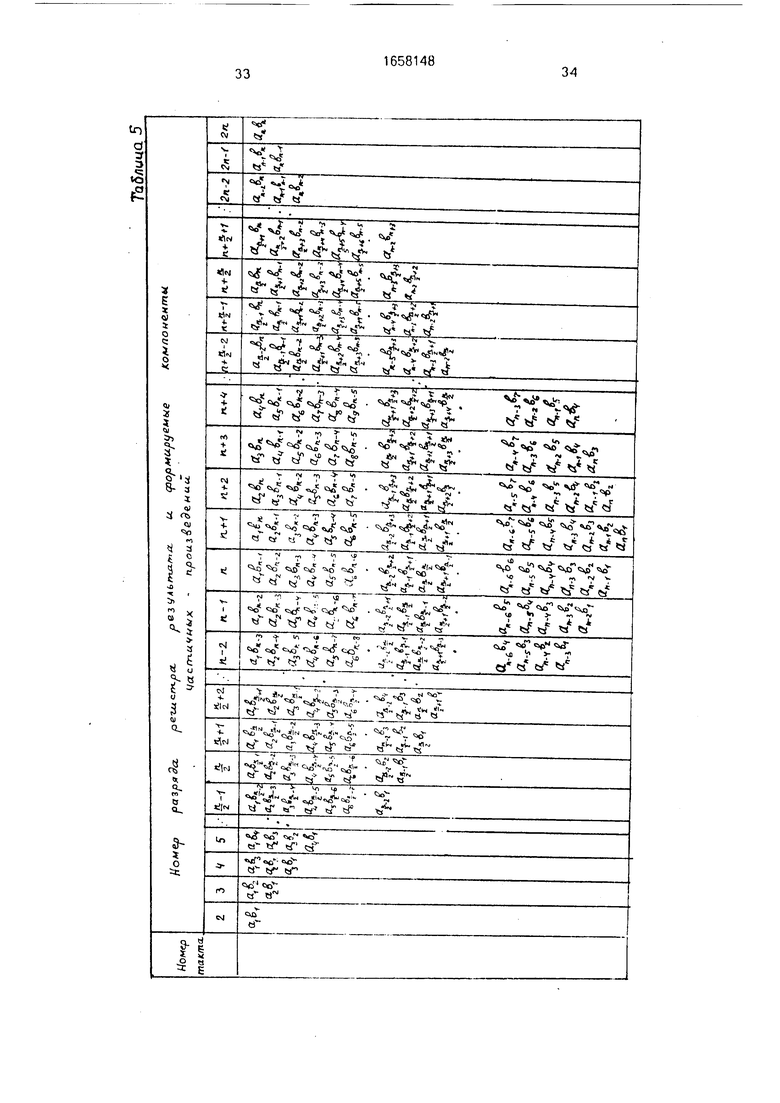

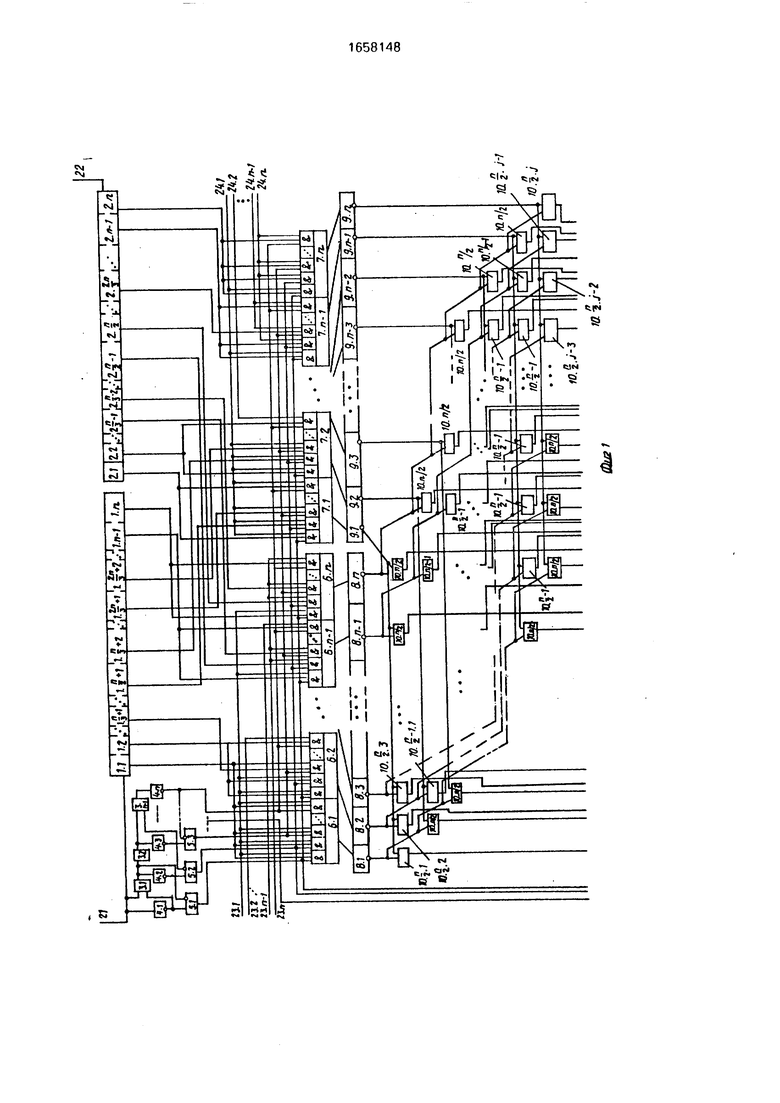

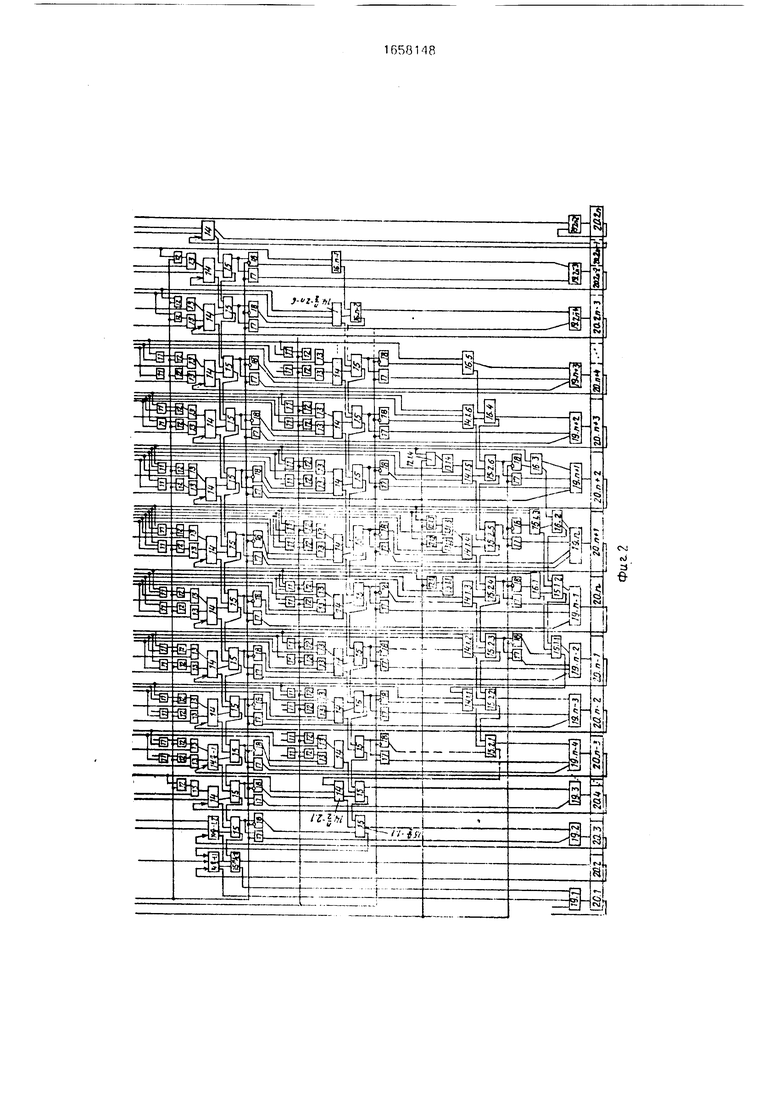

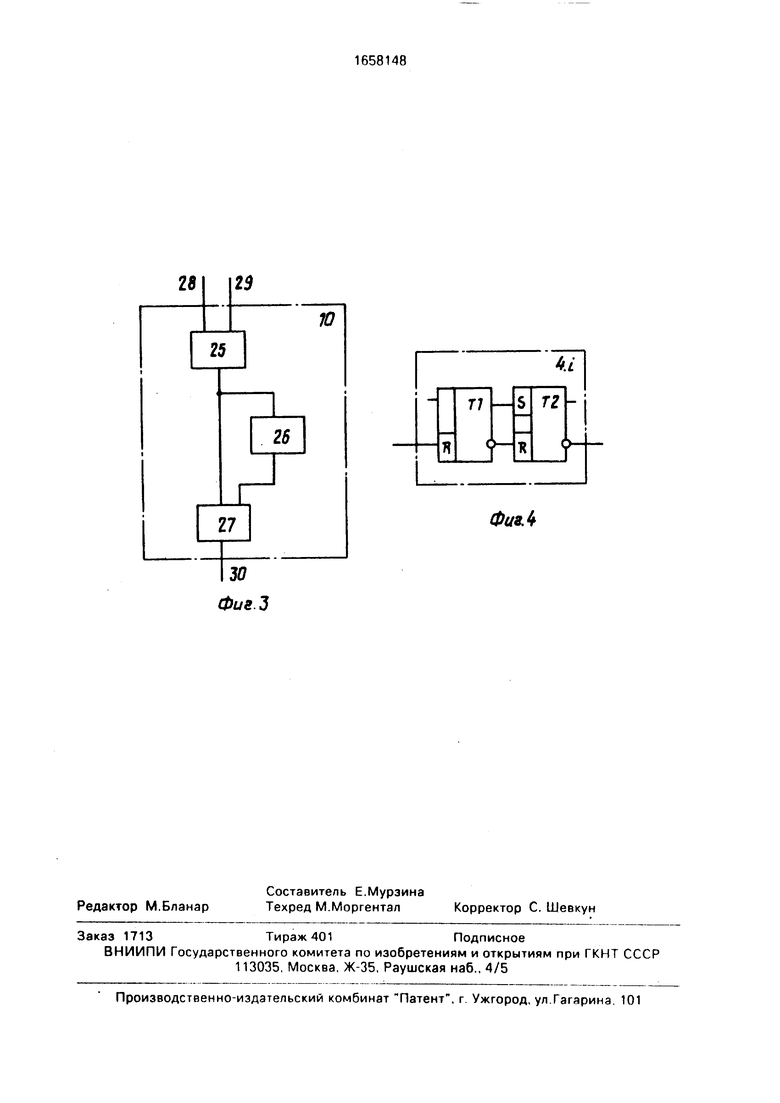

На фиг. 1 и 2 представлена функциональная схема устройства, на фиг 3 - схема формирующего элемента, на фиг. 4 - схема фиксатора режима работы (состояния), состоящего из основного триггера (ТО) и дополнительного триггера (TD) Табл. 1-5 иллюстрируют процесс формирования частичных произведений для , , , . .

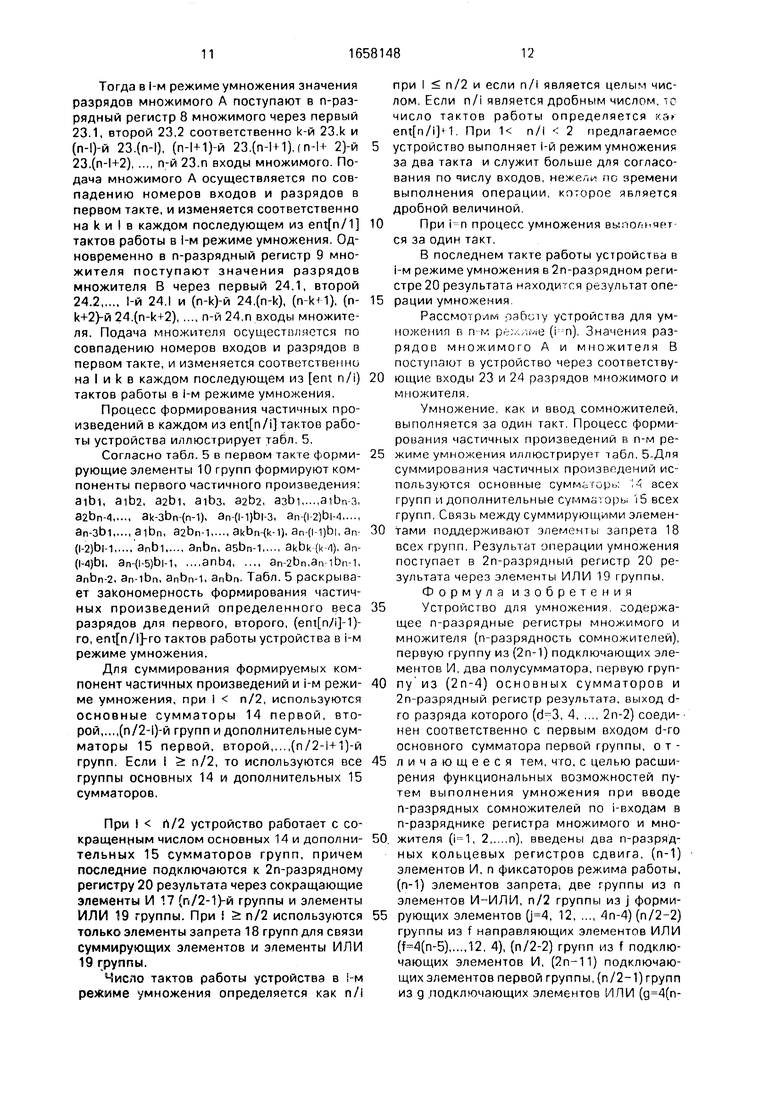

При использовании схемы фиксатора, как фиксатора режима работы, у триггера TD задействован инверсный выход, а для фиксатора состояния - прямой выход триггера TD.

Устройство (фиг. 1 и 2) для умножения содержит два n-разрядные кольцевые регистры сдвига 1 и 2, (п-1) элемент И 3, п фиксаторов 4 режима работы, (п-1) элементов запрета 5, две группы из п элементов И- ИЛИ 6 и 7, n-разрядный регистр 8 множимого, n-разрядный регистр 9 множителя, п/2

ON СЛ СО

Ј 00

групп из ) формирующих элементов 10 , 124п-4), (п/2-2) группы из f направляющих элементов ИЛИ 11, ((n-5)12, 4),

(п/2-1) группу из g подключающих элементов И 12((n-3)12п, 4), (п/2-1) групп из

g подключающих элементов ИЛИ 13, (п/2-1) групп из основных сумматоров 14, (, 2п-614, 10, 6), три дополнительных сумматора 15 первой группы, п/2 групп из К дополнительных сумматоров 15(, 2п6, 2п-2 10, 6, 3), п полусумматоров 16,

(п/2-1) групп из m сокращающих элементов

И 17 (m 2n-48, 4), (п/2-1) групп из m

элементов запрета 18, группу из (2п-2) элементов ИЛИ 19, 2п-разрядный регистр 20 результата, управляющие входы 21 и 22 устройства, входы множимого 23 и множителя 24 устройства.

Формирующий элемент 10 (фиг, 3) содержит первый элемент И 25, фиксатор 26 состояния, второй элемент И 27, входы 28 и 29 и выход 30 формирующего элемента.

Подготовка предлагаемого устройства к работе.

В исходном состоянии п-разрядные кольцевые регистры 1 и 2 сдвига и 2п-раз- рядный регистр 20 результата обнулены.

Основные триггеры фиксаторов 4 режима работы, n-разрядного регистра 8 множимого, n-разрядного регистра 9, множителя, фиксатора 26 состояния формирующего элемента 10 устанавливаются в единичное состояние.

Допустим, что множимое А и множитель В соответственно равны А {3132333435. ..aiai+i.,.an-ian}.B {610203

b4D5...bibl+1...Dn-lbn}.

Для управления записью необходимой информации в разряды регистров 8 и 9 множимого и множителя устройство используют два n-разрядных кольцевых регистра 1 и 2 сдвига, п-1 элемент запрета 5.

Устройство может работать в нескольких режимах при подаче множимого и множителя в соответствующие регистры: по одному разряду, по нескольким разрядам и по всем п разрядам.

Запись информации с входов 23.i разрядов множимого и входов 24.1 разрядов множителя в соответствующие разряды регистров 8 и 9 множимого и множителя производится через первую и вторую группы элементов И-ИЛИ 6 и 7, Каждый элемент И-ИЛИ 6 и 7 группы имеет no n групп входов, по три входа в каждой группе.

При этом 1-я группа входов элементов И-ИЛИ 6 и 7 группы соответствует i-му режиму работы предлагаемого устройства.

Коммутация выходов разрядов п-раз- рядных кольцевых регистров 1 и 2 сдвига с

вторыми входами i-x групп входов элементов И-ИЛИ 6 и 7 группы основана на соот- .ветствии выхода разряда п-разрядных кольцевых регистров 1 и 2 сдвига с единичным значением разряду регистра множимого 8 или множителя 9 для данного i-ro режима работы и такта работы устройства. Число тактов работы устройства в i-м режиме определяется отношением , где

0 ent -целая часть числа.

Первоначальная запись 1-го кода в п- разрядные кольцевые регистры 1 и 2 сдвига в исходном состоянии соответствует первому такту работы устройства в i-м режиме

5 умножения. Для работы в каждом последующем такте производится сдвиг первоначального 1-го кода на один разряд в сторону n-го разряда для первого n-разрядного кольцевого регистра 1 сдвига, и в сторону перво0 го разряда для второго п-разрядного кольцевого регистра 2 сдвига

Для работы устройства в первом режиме умножения в первый n-разрядный кольцевой регистр 1 сдвига записывается код

5 100...00, во второй n-разрядный кольцевой регистр 2 сдвига записывается код 000...01. В каждом из п тактов работы перемещаемые в n-разрядных кольцевых регистрах 1 и 2 сдвига единичные значения подключают

0 соответствующие разряды n-разрядных регистров 8 и 9 множимого и множителя.

Для работы устройства в втором режиме умножения в первый n-разрядный кольцевой регистр 1 сдвига записывается код с

5 единичными значениями в первом и ()-м разрядах, во второй и п-раз- рядный кольцевой регистр 2 сдвига записывается код с единичными значениями в en. и n-м разрядах, где ent - целая

0 часть числа. В каждом из тактах работы перемещаемые единичные значения с первого разряда в первом п-разряд- ном кольцевом регистре 1 сдвига и с во втором кольцевом регистре 2

5 сдвига управляют поступлением информации в разряды n-разрядного регистра 8 множимого, а поступлением информации в разряды n-разрядного регистра 9 множителя управляют перемещаемые единичные

0 значения с n-го разряда в втором п-разряд- ном кольцевом регистре 2 сдвига и с (ent()-ro разряда в первом п-разряд- ном кольцевом регистре 1 сдвига.

Для работы устройства в третьем режи5 ме умножения в первый n-разрядный кольцевой регистр 1 сдвига записывается код с единичными значениями в первом, (ent n/3 +1}-M и ()-M разрядах, во второй n-разрядный кольцевой регистр 2 сдвига записывается код с единичными значениями в entfn/3 -M, и n-м разрядах.

В каждом из тактах работы перемещаемые единичные значения с первого и ()-ro разрядов в первом л-раз- рядном кольцевом регистре 1 сдвига и с во втором n-разрядном кольцевом регистре 2 сдвига управляют поступлением информации в разряды п-разрядного регистра 8 множимого, а поступлением информации в разряды n-разрядного регистра 9 множителя управляют перемещаемые единичные значения )-ro разряда первого n-разрядного кольцевого регистра

1сдвига и с и n-го разрядов второго n-разрядного кольцевого регистра

2сдвига.

Для работы устройства в i-м режиме умножения в первый n-разрядный кольцевой регистр 1 сдвига записывается код с еди ничными значениями в разрядах первом , , , ,,ent(l- 2), ent(M), во второй п-разряд- ный кольцевой регистр 2 сдвига записывается код с единичными значениями в разрядах: n-ent(i 1)n/i, n-ent(i 2)n/iJ

n-ent(l-3)n/ln-ent 1n/i n . nent n/i, n

В каждом из raKijH рлгюты ПР- ремещаемые единичные значения г дов n-ртзрядного кольцевого регистра 1 сдвига управляют поступлением инфоома- ции в n-разрядные регистры 8 и 9 мноч имо- го и множителя, при(ем при гмещ(, информации от первых разрядов н сторону n-го разряда, а перемещаемые единичные значения с разрядов п-рэзрядного кельи з- вого регистра 2 сдвига управпяют пог.туппением информации в n-разрядные регистры 9 и 8 множителя и множимого, поиче при смещении информации от n-х разрядов в сторону первого разряда

Для работы устройства в л-м режиме умножения в n-разрядные кольцевые регистры 1 и.2 сдвига записываются коды III., II. При этом операция умножения выполняется за один такт работы устройства, выходы разрядов первого n-разрядного кольцевого регистра 1 сдвига управляют подачей информации в соответствующие разояды п- разрядного регистра 8 множимого выходы разрядов второго п-разрядного кольцевого регистра 2 сдвига управляют подачей информации в соответствующие разряды п- разрядного регистра 9 множителя

Код каждого из I режимов работы умножителя имеет свою особенность - в нем число разрядов с единичным состоянием равно I. Этз особенность кода режима работы умножителя использует я для фиксирования режима работы фиксаторами 4 i режима работы. Перед установкой режима основные триггеры фиксаторов 4 i режима работы установлены в единичное состояние, инверсный сигнал с выхода дополнительного триггера i-ro фиксатора 4.I режима работы блокирует прохождение единичного сигнала через 1-й элемент И 3.1 и разрешает прохождение единичного сигнала через (I0 )-й элемент запрета 5.(i-l). При поступлении единичного сигнала на вход установки в нуль основного триггера 1-го фиксатора 4.1 режима работы, происходит сброс в нуль этого фиксатора 4.1 режима работы, блоки5 руется (1-)-й элемент запрета 5(i-1) и разрешается прохождение следующего единичного сигнала через 1-й элемент И 3.1. После записи 1-го кода режима умножения в п-разрядные кольцевые регистры 1 и

0 2 сдвига, на выходе 1-го элемента запрета 5.1 имеется единичное значение, которое поддерживается фиксаторами 4 I режима работы на протяжении работы предлагаемого устройства в i-м режиме умножения. При

5 п-м режиме умножения единичный сигнал снимается с инверсного выхода n-го фиксатора 4 л режима работы

В исходном состоянии все разряды п- оазрядных регистров 8 и 9 множимого и

0 множителч установлены в единичное госто- я.чие (входи установки в единичное состояние на схеме устройства не показаны).

Запись единичной информации в разряд п-рэзрядиого регис гра 8 множимого или

5 в пазряд n-разряднигр регистра 9 множите- i° производится через вход установки в гуль данного разряда В результате запи санная информация фиксируется в данном разряде и снимается с инверсного выхода

0 разряда поддерживаясь на протяжении всего времени выполнения операции умножения над данной парой множимого А и множителя В

Работа формирующего элемента 10

5 (фиг. 3) заключается в одноразовом формировании и последующем отключении соответствующего данному формирующему элементу 10 частичного произведения. Такой режим работы формирующих элементов

0 10 искгючает наложение информации с одинаковым весом разрядов и не требует, чтобы 2п-разрядный регистр 20 результата был сдвиговым. Перед началом работы фиксатор 26 состояния каждого формирующего элеЬ мента 10 установлен в единичное состояние. При появлении на выходе первого элемента И 25 единичного частичного произведения фиксатор 26 состояния формирующего элемента сбрасывается в нуль Так фиксатор 26 состояния построен на двух

триггерах, то в данном такте работы устройства единичный сигнал с выхода первого элемента И 25 проходит через второй элемент И 27, а в следующем такте работы устройства второй элемент И 27 уже заблокирован нулевым сигналом с выхода допол- нительного триггера фиксатора 26 состояния.

Суммирование частичных произведений выполняется суммирующими группами, состоящими из основных 14 и дополнительных 15 сумматоров и п полусумматоров 16. Особенностью работы суммирующей части схемы предлагаемого устройства является наличие групп сокращающих элементов 17 и групп элементов запрета 18, обеспечивающих сокращение числа суммирующих групп основных 14 и дополнительных 15 сумматоров, если при i-м режиме умножения можно обойтись меньшим количеством основных 14 и дополнительных 15 сумматоров.

Этой цели служит группа элементов ИЛИ 19, связывающая суммирующие труп пы с входами разрядов 2п-разрядного реги стра 20 результата.

Для подключения формирующих элементов 10 к сокращенному количеству суммирующих групп основных 14 и дополнительных 15 сумматоров служат группы направляющих элементов ИЛИ 11, группы подключающих элементов И 12, группы подключающих элементов ИЛИ 13.

При умножении следующей пары множимого А и множителя В в этом режиме работы устройства производится установка в единичное состояние разрядов п-разряд- ного регистра 8 множимого, п-разрядного регистра 9 множителя, фиксаторов 26 состояния формирующих элементов 10 и обнуление разрядов 2п-разрядного регистра 20 результата.

Если умножение следующей пары множимого А и множителя В необходимо выполнить в другом режиме работы устройства, то дополнительно производится обнуление п- разрядных кольцевых регистров 1 и 2 сдвига, установка в единичное состояние фиксаторов 4 режима работы и производится подготовка устройства к работе в требуемом режиме умножения.

-

Рассмотрим работу устройства для умножения в первом режиме (). Через первый вход 23.1 множимого в течение п тактов в устройство поступают значения разрядов множимого А, начиная со значения старшего разряда ai. Одновременна через первый вход 24.1 множителя поступают значения

5

разрядов множителя В, начиная со значения младшего разряда bn.

Процесс формирования частичных произведений в каждом из п тактов работы устройства иллюстрирует табл. 1. Компонента aibn первого частичного произведения формируется1 в первом такте работы устройства (30 + 4)/4-3)-м формирующим элементом 10-n/2-(3Q + 4 )/4 - 3), п/2гй группы. Компоненты aibn-i, a2bn-i, 32bn второго частичного произведения формируются во втором такте работы устройства

10.n.3(Lt4)4)i10.()x

х

(M«l-3).io-n-(liL±«l-2)

20

25

формирующими элементами (п/2-1)-й и n/2-й групп. Согласно табл. 1 компоненты aibi, 32bi, ..., anbi. anb2, ..., anbn n-го частичного произведения формируются в n-м такте работы устройства формирующими элементами

П

2 п

10

Д. ч 2

10

210

10

2(Н4+1)1°1

(j±4) I 4 J(- - п

п

о

.

10

п 2

n/2-й группы.

Для суммирования частичных произведений используются первые группы основных сумматоров 14 и дополнительных сумматоров 15, выходы которых подключаются через сокращающие элементы И 17

первой группы и элементы ИЛИ 19 группы к входам соответствующих разрядов 2п-раз- рядного регистра 20 результата, в котором после n-го такта работы устройства находится результат операции умножений.

Рассмотрим работу устройства для умножения в втором режиме работы (). Через первый вход 23.1 множимого в течение п/2 тактов в устройство поступают значения разрядов множимого А, начиная со значения старшего разряда ai, через n-й вход 23.п множимого - начиная с младшего разряда ап. Одновременно через первый вход 24.1 множителя поступают значения разрядов множителя В, начиная со значения старшего разряда bi, а через n-й вход 24.п множителя - начиная с младшего разряда Ьп.

Процесс формирования частичных произведений в каждом из ri/2 тактов работы

устройства иллюстрирует табл. 2. В первом такте формирующими элементами

10 П/2 1, 10 п/2

LL 4

10 П/2

3, 10 n/2 j

(n/2 - 1)-й группы формируются компоненты aibi, anbi, aibn. anbn первого частичного произведения. Во втором такте формирующими элементами

10 -п/2 -()

ю п/2 :

10 (п/2- 1)

1, 10-п/2. (),

10 -п/2 ( Нр 1) 10 К2- ) x(3Q+4)-3)l1Q-(n/2-1)-(J+4).

10 -П/2 ), 10

v 4

n/2 x

х(Ц4 + 1),10-(п/2-1)

10 n, 2-I 1,

10

П/2 (L+ - 2)

n/2-й и (п/2 -1)-й группы формируются компоненты второго частичного произведе ния: aib2, 32bi, aibi. aibn 1, an-ibi, 32bn 1, an-ib2, 32bn, anb2. an-ibn-i, aa ibn anbn 1 Co- гЛасно табл. 2 в формировании компонент n-го частичного произведения-а1Ьп/2, ап/2

bl,aibn/2+1, 32bn/2. ar/2b2, 3n/2+lbl an/2bn/2+1. an/2+lbn/2, Эп/2Ь../2 a /2. bn/ .--H an/2+2bn/2an/2Hbn anbn/2H.

участвует центральная часть формис/о- щих элементов 10.

Для суммирования чтлмчных произг - дений используются перзая и вторая груг пы основных 14 и дополнительных 15 сумматоров. Связь суммирующих тов выполняется с помощью эп ментов за прета 18 первой группы дополнительных сумматоров 15 первой группы подключаются 2п-разряднрму регистру 20 результата через сокращающие элементы И 17 второй группы и элементы ИЛИ 19 группы. Результат операции умножения после entf находится в 2п-разрядном регистре 20 ррзупьтата

Рассмотрим работу устройства для умножения в третьем режиме (ИЗ) Значения разрядов множимого А поступают р п-раз- рядный регистр 8 множимого через первый 23.1, второй 23 и п-й 23 п входы множимого, начиная, соответственна с передо, второго и n-го разрядов. Значения г зрядов множителя В поступают в n-разрядный регистр 9 множителя через первый 24.1, второй 24.2 и п-й 24 п входы множителя, начиная, соответственно, с первого, (п-1}то и n-го разрядов.

Процесс Формирования частичных произведений в каждом из /31 тактов pafio- ты устройства иллюстрирует габл, 3.

Согласно табл. 3, компоненты aibi 32bi. aibn-i, aibn, 32bt- 1, anbi, a2bn, anbn-i, anbn первого частичного произведения формируют формирующие элементы

10 п/2 -1,10- п/2 2, (4 -4), 10 п/2 (1ILL4) - 3). 10 (П/2 - 1)х

0

х( 10

5

0

5

5

0

5

0

5

30+4)

3), 10-п/2

-1-4 , iu-п// ,

П/2 () 2). 10 n/2 x

x(), 10 -n/2 -J

n/2-й (п/2-1)-й групп Во втором такте формируются компоненты aib2, а2Ьз. азЬ1, азЬ2, a-ibi, a-ib2. aibn з. aibn 2, aibn 2. ззЬп-2, азЬп-з, an-ibi, азЬп 2, з, an ib2, азЬп-1, 34bn-2, anb2 азЬ a4bn i, , an-ibn з чпЬп-з. anbn з. an ibn 2, anbn 2. an ibn-2. an-ibn i, an ibn второго частичного произведения с помощью формирующих элементов n/2-й, (п/2-1)-й, (п/2-2)-й, (п/2-3)-й групп В формировании компонент entfn/3 -ro частичного произведенияaibn/3+1 32bn/3. aibn/3 2. a2bn/3 i, азЬп/з

a2n/lb2n/3-4, 32n/3bn/3-H 32n/lJlbn/3

lb2n/345. Э2п/зЬ2п/ 4, а2(к lb2n/3+3.

участвуют формирующие эпементы 10, не } срмировпои ие единичных значен чэс- ti чны ||роизведенин в предыдущие актах устройства

Ллч суммироолния частичных произведении используются первая, вторая, третья группы основных 14 и ,спполнитемьных 15 сумматоров Связь суммирующих злемен- тое выполняют элементы запрета 18.

Выходы дополнительных сумматоров 15 второй группы подключаются к 2п-разряд- ному регистр/ 20 результатя через сокращающие элементы И 17 третий группы и элементы ИЛИ 19 группы После ent n/3}-ro такта работы устройства в 2п-разрядном регистре 20 результата находится результат операции умножения

Рассмотрим работу предлагаемого устройства в i-м режиме умножения

Лопустим, что i i t-k ГДР числа Обозначим через I число младших разрядов множимого А которые поступают в -спеем такте 1-го режима умножения, а через к - число старших разрядов множимого V которые поступают в перром такте 1-го режима умножения. Для разрядов множителя В обозначение обратное1 k - число младших оазрядов множителя В. которые поступают в первом такте 1-го режима умножений а I- число старших разрядов множителя В , поступающих в этом же такте.

Тогда в i-м режиме умножения значения разрядов множимого А поступают в п-раз- рядный регистр 8 множимого через первый 23.1, второй 23,2 соответственно k-й 23.k и (п-)-й 23.(n-l). (п-1+1)-й 23.(п-1+1)лп-1+ 2)-й 23.(n-l+2)п-й 23.п входы множимого. Подача множимого А осуществляется по совпадению номеров входов и разрядов в первом такте, и изменяется соответственно на k и I в каждом последующем из тактов работы в 1-м режиме умножения. Одновременно в n-разрядный регистр 9 множителя поступают значения разрядов множителя В через первый 24.1, второй

24.2 1-й 24.1 и (п-к)-й 24.(n-k), (n-kn 1), (nк+2)-й 24.(n-k+2), ..., n-й 24.п входы множителя. Подача множителя осуществляется по совпадению номеров входов и разрядов в первом такте, и изменяется соответственно на I и k в каждом последующем из ent n/i) тактов работы в i-м режиме умножения.

Процесс формирования частичных произведений в каждом из тактов работы устройства иллюстрирует табл. 5.

Согласно табл. 5 в первом такте формирующие элементы 10 групп формируют компоненты первого частичного произведения:

aibi, aib2, 3201, 3103, 32b2, азотaibn-з,

32bn-4 ak-3bn-(n-i), an-(i-i)bi-3, an-(i-2)bi-4

an-3biaibn, 32bn-iakbn-(k-i), an-(i-i)bi, an(i-2)bi-ianbianbn, asbn-1akbk (k-i), an(M)bi, an-(i-5)bi-iапЬз an-2bn,an-ibn-i,

anbn-2, an-ibn, anbn-1, anbn. Табл. 5 раскрывает закономерность формирования частичных произведений определенного веса разрядов для первого, второго, ()- го, тактов работы устройства в i-м режиме умножения.

Для суммирования формируемых компонент частичных произведений и i-м режиме умножения, при i n/2, используются основные сумматоры 14 первой, второй,..,,(п/2-)-й групп и дополнительные сумматоры 15 первой, второй,.,.,(п/2-1+1)-й групп. Если i n/2, то используются все группы основных 14 и дополнительных 15 сумматоров.

При п/2 устройство работает с сокращенным числом основных 14 и дополнительных 15 сумматоров групп, причем последние подключаются к 2п-разрядному регистру 20 результата через сокращающие элементы И 17 {п/2-1)-й группы и элементы ИЛИ 19 группы. При i n/2 используются только элементы запрета 18 групп для связи суммирующих элементов и элементы ИЛИ 19 группы.

Число тактов работы устройства в i-м режиме умножения определяется как n/l

при I п/2 и если n/i является целым числом. Если n/i является дробным числом,тс число тактов работы определяется к;о . При 1 n/l 1 предлагаемое1

устройство выполняет 1-й режим умножения за два такта и служит больше для согласования по числу входов, нежели по зремени выполнения операции, которое является дробной величиной.

0При процесс умножения выполняется за один такт.

В последнем такте работы устройства в i-м режиме умножения в 2п-разрядном регистре 20 результата находится результат опе5 рации умножения

Рассмотрим рабслу устройства для умножения в п м pe.v/. (). Значения разрядов множимого А и множителя В поступают в устройство через соответству0 ющие входы 23 и 24 разрядов множимого и множителя.

Умножение, как и ввод сомножителей, выполняется за один такт, Процесс формирования частичных произведений в n-м ре5 жиме умножения иллюстрирует табл. 5-Для суммирования частичных произведений используются основные сумма горь: всех групп и дополнительные сумматоры 15 всех групп. Связь между суммирующими элемен0 тами поддерживают элементы запрета 18 всех групп. Результат операции умножения поступает в 2п-разрядный регистр 20 результата через элементы ИЛИ 19 группы. Формула изобретения

5Устройство для умножения, содержащее n-разрядные регистры множимого и множителя (n-разрядность сомножителей), первую группу из (2п-1) подключающих элементов И, два полусумматора, первую груп0 пу из (2п-4) основных сумматоров и 2п-разрядный регистр результата, выход dго разряда которого (, 42п-2) соеди-

нен соответственно с первым входом d-ro основного сумматора первой группы, о т 5 ли чающееся тем, что, с целью расширения функциональных возможностей путем выполнения умножения при вводе n-разрядных сомножителей по i-входам в n-разряднике регистра множимого и мно0. жителя (, 2п), введены два п-разрядных кольцевых регистров сдвига, (п-1) элементов И, п фиксаторов режима работы, (п-1) элементов запрета, две группы из п элементов И-ИЛИ, п/2 группы из j форми5 рующих элементов (, 124п-4) (п/2-2)

группы из f направляющих элементов ИЛИ ((n-5)12, 4), (п/2-2) групп из f подключающих элементов И, (2п-11) подключающих элементов первой труппы,(п/2-1) групп из g .подключающих элементов ИЛИ ((n3), 12,4) два основных сумматора первой группы (п/2-2) групп из h основных сумматоров ( ,14 10 6) (п/2) групп из К дополнительных сумматоров (К 2п 4 2п 6 2п-2, , 10.6,3) (п-2) полусумматора (п/2 1) групп из m сокращающих элементов И (m-2n-4, , 8 4), (п/2-1) групп из m элемен тов запрета и группу из (2п-2) элементов ИЛИ, причем первый управляющий вход ус тройства соединен с входом первого разря да первого n-разрядного кольцевого регистра сдвига и первыми входами первого элемента И и первого фиксатора режима работы, первый вход р-го элемента И кроме первого элемента И соединен соответственно с выходом (р-1) го элемента И инвер сный выход р-го фиюаторс) режима онЕнлн (, 2, , п-1) соединеч соответственно ( вторым входом р-го )леменга И и прямым входом р-го элемента запрет инверсный вход которого соединен coi ret гственно с инверсным выходом (р41) го фикст ра ре жима работы вход когоро. о соединен сиот ветственно с выходом р го -пеменм И первые входы рх ipynn элементог И-ИЛИ первии и второй i ругы объединены и соединены соотв тствеино с еыхо,щ мр to элемента запрет т ip m входов элементов И и Ь . i 01 (i

tf/ynn объединены 1 i u ны инн ным выходом n-го (рик пом i с Г j

ты, вторые входы i . f и f / дс t u | t i эпемента И ИЛИ IKVPь L - , ,

с выходом первого рсЛ и п р )г , кольцевого per ист РП слвиг a разряда которого оедпнен t л.и г и ми вторыми входами %ГР)Г ( - ос входов третьей и -штрертои if/ипi ь

второго элемента И Ил / ч ич i уш i вторыми входами rpei 11 и и ( р j i и/1 i входов третьего зпемеии И ЛЛ11 гкрг группы выход ( 1) i о pd рчда i р рядного кольцевою ma crei id f i,r entfn/4 - целая чяст i чи. л 0 соединеч ntjr ветственно с вторим аховом МЕ°ГГО.Л группы входов второю элемент l/l i/ И первой группн и вторыми входами юрчои i- n-й rpvnn входов (enifn М 1У гя эг vf нта 1Л ИЛИ первой группы рторои РЛ ;д тг i i

ГРУППЫ ВХОДОП ВТОРОГО Э/Н Т Jv 1 |И

первой группы и втор е п пм г,о ,/ i групп входов ( 1) о jn м( нт 1 ИЛИ первой группы oDbt-Д ii с г ел f ны соответственно f выходом i г i/Sl4 i разряда первого n-разрядного 1ольцетс.о регистра сдвига РЫХОД (е Iri/2j Я io f з ряда которого соединен с BTOPL n . первой и n-iT rp/np evoj.oe (en r г элемент И-ИЛИ тгрвой гр/пп / рторикВХОДОМ ВТОрОИ ГруППЬ j/ V Г U O Т f

мента И ИЛИ второй группы второй вход второй группы входов второго элемента И ИЛИ второй группы объединен с вторыми входами первой и n-й групп входов

()-ro элемента И И ПИ первой группы и соединен с выходом )- го разряда первого п разрядного кольцевого регистра сдвига выход ()-ro разряда которого соединен с вторыми вхо

0 дами первой и n-й групп входов () го элемента И ИЛИ первой группы и вторым входом третьей группы входов первого элемента И ИЛИ второй группы второй вход третьей группы входов

5 второго элемента И ИЛИ второй группы объединен с вторыми входами петвой и п-й групп входов () го элемента И ИЛИ первой группы и соединен с выходом () to разряда первого п-разряд

0 ного кольцевого регистра сдвига соответст пенно выход (п 1) го разряда первого п разрядною кольцевого регистра сдвига ч.и динен с вторыми входами первой и п и ipynn Влодоп (п 1) to элемента И ИЛИ пер

5 вой группы и вторым входом (п 1) и группы входов ( 1) го элемента И ИЛИ вто рои групп1 оы,| л п о разряда первого п pj3p оного ко bij ьо о реп тра сдитгг -о /и1 он в орыми ходами морво.1 и п и 1 | i i t i д f i о iet |t3HT() 1 ИЛУ пг г в 1

) v 1П И а Г)Ь t „ ., МП v Г рI 3X0

i г j го п м нти J И ПИ юро.

1 , iс ( ( В с i i , f if i 0 Го i Ы ilрп рЧ,П )ГО - 1 ИРНОГО ° 1СГ, 3 .Д 05,1м С Р Т (ус Мi. /., J I I I 1 . i )Г Ы

L n ion f ,/ rjo icr лн,т1 Ил/пер и v п и i | г -п иходаг и пер о/ / п и . i вхонгв перьиго л MI Hrd I/ ИЛ в о

1 OH rp,l1HLI В v.)pLie ОХОГ,Ы Г6, Li П И

n г п/одов вгоро1 о и jll I7i 1И вто- зе ггумы объединены с «чторым входом m ij и гpyiiiti eiitfn/ 1 2j го элсме i i i/l /nl первой группы и соединены с зькодом второго второго п разрядb iu o голоцевс о рьгистра гдчщ выход

( 1) го разряда которп - соед жен с

вгоонм 1 вводами тервои и п и групп вводов

(гшГ i jj 1) го элементе. И 1Л 1-чорои груп, F торым вхо,гк 1 т те t v гр , ип i входов

0 n i) j -ктементй I/ ИЛИ пер1 он группы rTopt г/ оды первой и г и rpvnn входов nL 31 го элементе. И ИПИ второй группы obi ri пены ( вторым в кодом третьей г одов п го элемент И ИЛИ первой

S rrr iriui и соединены с вь ходом pa ( |Д торого п разрядного кольцевого Г- j ЕЬ чод ( 1j о разря ч i ю эр г о диньн с вторыми Олегами n L. юи и - групг вхоцов(с 1 -го эле

ч ( И-ИПИ Рторти ру ппь и вторым BvO

дом второй группы входов (п-1)-го элемента И-ИЛИ первой группы, вторые входы первой и n-й групп входов ent n/2}-ro элемента И-ИЛИ второй группы объединены с вторым входом второй группы входов n-го элемента И-ИЛИ первой группы и соединены с выходом разряда второго п-раз- рядного кольцевого регистра сдвига, выход ent 2n/3}-ro разряда которого соединен с вторыми входами первой и n-й групп входов элемента И-ИЛИ второй группы и вторым входом третьей группы входов (л-1)-го элемента И-ИЛИ второй группы, второй вход четвертой группы входов (п-1)- го элемента И-ИЛИ второй группы объединен с вторыми входами первой и n-й групп входов ()-ro элемента И ИЛИ второй группы и соединен с выходом ()-ro разряда второго п-разрядно- го кольцевого регистра сдвига соответственно, выход (п-1)-го разряда второго n-разрядного кольцевого регистра сдвига соединен с вторыми входами i-x групп входов, кроме входов третьей и четвертой групп входов, (п-1)-го элемента И-ИЛИ второй группы и вторыми входами третьей и четвертой групп входов (п-2)-го элемента И-ИЛИ второй группы, вторые входы i-x групп сходов n-го элемента И-ИЛИ второй группы соединены с выходом n-го разряда второго n-разрядного кольцевого регистра сдвига, третьи входы первых групп входов элементов И-ИЛИ первой группы, третьи входы вторых групп входов первых элементов И-ИЛИ первой группы, третьи входы третьих групп входов первого, третьего, соответственно, ()-ro элементов И-ИЛИ первой группы, третьи входы четвертых групп входов первого, третьего, соответственно, ()-ro элементов И-ИЛИ первой группы, третьи входы пятых групп входов первого, четвертого, соответственно ()-ro элементов И-ИЛИ первой группы, соответственно, третий вход n-группы входов первого элемента И-ИЛИ первой группы объединены и соединены с входом первого разряда множимого устройства, третьи входы третьих групп входов второго, четвертого, соответственно элементов И-ИЛИ первой группы, третьи входы четвертых групп входов второго, четвертого, соответственно элементов И-ИЛИ первой группы, соответственно, третий вход n-й группы входов второго элемента Vl-ИЛИ первой группы объединены и соединены с входом второго разряда множимого, третьи входы четвертых групп входов (eru 2n/4j+1)-ro, ent()-ro, соответственно, (п-1)-го элементов Й-ЙЛИ первой группы, третьи входы пятых групп входов ( 1)-ro, (ent 4п/5 + 3)-го, соответственно, (п-1) го элементов И-ИЛИ первой группы соответственно, третий вход (п-1)-й группы входов (п-1)-го элемента И-ИЛИ первой группы объединены и соединены с входом (п-1)-го разряда множимого, третьи входы вторых групп входов последних элементов И-ИЛИ первой группы, третьи входы треть- 0 их групп входов последних элементов И-ИЛИ первой группы, третьи входы четвертых групп входов ( 2)-ro ( + 4)-го, соответственно, n-го элементов И-ИЛИ первой группы, третий вход 5 n-й группы входов n-го элемента И-ИЛИ первой группы объединены и соединены с входом n-го разряда множимого третьи входы первых групп входов элементов И-ИЛИ второй группы, третьи входы вторых групп 0 входов первых элементов И-ИЛИ второй группы, третьи входы третьих групп входов первых элементов И-ИЛИ второй группы, третьи входы четвертых групп входов первого третьего, соответст- 5 венно, ()-ro элементов И-ИЛИ второй группы, третьи входы пятых групп входов первого, третьего, соответственно ()-ro элементов И-ИЛИ второй, группы, третий вход n-й группы вхо- 0 дов первого элемента И-ИЛИ второй группы объединены и соединены с входом первого разряда множителя, ,третьи входы четвертых групп входов второго, четвертого, соответственно, 5 го элементов И-ИЛИ второй группы, третьи входы пятых групп входов второго четвертого, соответственно, элементов И-ИЛИ второй группы, третий вход п-й группы входов второго элемента И-ИЛИ 0 второй группы объединены и соединены с входом второго разряда множителя, третьи входы третьих групп входов ()-ro )-ro, второго элементов И-ИЛИ второй группы, третьи входы четвертых 5 групп входов ()-ro, ()- го второго элементов И-ИЛИ второй группы, третьи входы пятых групп входов ()-ro, )-ro второго элементов И-ИЛИ второй группы, третий вход 0 n-й группы входов1 (п-1)-го элемента И-ИЛИ второй группы объединены и соединены с входом (п-1)-го разряда множителя, третьи входы вторых групп входов последних элементов И-ИЛИ второй группы, 5 третьи входы третьих групп входов ()-ro, ()-ro соответственно, n-ro элементов И-ИЛИ второй группы, третьи входы четвертых групп входов ()-ro. ()-ro, соответственно, n-ro элементов И-ИЛИ второй труппы, третьи входы пятых групп входов ()-ro, ()-ro, соответственно, n-го элементов И-ИЛИ второй группы, третий вход n-й группы входов п-го элемента И-ИЛИ второй группы объединены и соединены с входом n-го разряда множителя, выходы 1-х элементов И-ИЛИ первой группы соединены соответственно с входами установки в О 1-х разрядов п-раз- рядного регистра множимого, выходы 1-х элементов И-ИЛИ второй группы соединены соответственно с входами установки в О 1-х разрядов n-разрядного регистра множителя, первые входы 1-х формирующих эле- ментов каждой группы соединены с инверсным выходом 1-го разряда п-разряд- ного регистра множимого, инверсный выход (n/2-R + 1)-ro разряда п-разрядного регистра множителя (, 2 п/2) соединен соответственно с вторыми входами R1-x формирующих элементов R-й группы, инверсный выход (n/2+R)-ro разряда п-разрядi н о г о регистра множителя соединен

{соответственно с вторыми входами Р4-х формирующих элементов R-й группы, (Р4

-3 0 + 4)/4-3,,3 0 + 4)/2 - 2j), вторые

входы РЗ-х формирующих элементов R-й

труппы соединены с инверсными пыхоца- ми соответствующих разрядов п рдзртд ного регистра множителя (РЗ -/j 1У2 1,

(j-i 4)/2, .. , 3Q -М)/4 -4 , вторые входы Р-2 формирующих элементов R-й ГРУГ пы соединены с инверсными ВЫУОДЯ- ми соответствующих разрядов п разпяд- ного регистра множителя (Р2 j j - /i|; 4

fj 4- 4|/4 + 2(j f 4/2 - 2), выход первого

формирующего элемента первой группы соединен с первыми входами первого псп- усумматора, первого подключающего элемента И (п/2-1)-й группы и первыми входами (f/2-1)-x направляющих элементов ИЛИ каждой группы, выход третьего борми- рующего элемента первой группы соединен с первыми входами третьего дополнительного сумматора первой группы, второго подключающего элемента И (п/2-1)-й группы и f/2-x направляющих элементов ИЛИ каждой группы, выход второго формирующего элемента первой группы соединен с вторым входом третьего дополни. ельного сумматора первой группы, пергшг/и входами третьего подключающего элемента И (п/2-1)-й группы (f/2+1)-x направляющих элементов ИЛИ каждой группы, выход четвертого формирующего элемента первой группы соединен с первыми входами третьего полусумматора, четвертого подключающего элемента И (п/2-1)-й группы и входами (f/2+2)-x направляющих элементов ИЛИ

0

0

5

0

5

0

5

0

5

каждой группы, выход первого формирующего элемента s-й группы, (, 3 п/2)

соединен соответственно с первым входом первого основного сумматора q-й группы

(q n/2-1, n/2-2 2, 1) с первым входом

первого подключающего элемента И v группы (v n/2-2, n/2-32, 1) с первым входом

tl-го направляющего элемента ИЛИ v-й

группы, (t1 1. 5, 92п-11), выход (J+4J/21)-го формирующего элемента S-й группы соединен соответственно с первым входом второго основного сумматора q-й группы, с первым входом второго подключающего элемента И v-й группы, с первым входом т2-го направляющего элемента

ИЛИ v-й группы (t2 2, 6, 102п-10),

выход второго формирующего элемента s-й группы соединен соответственно с вторым входом второго основного сумматора q-й группы, с первым входом третьего подключающего элемента И v-группы, с первым входом t3-ro направляющего элемента ИЛИ v-й группы. (, 7, 112п-9).

выходу+4j/2-ro формирующего элемента Ј-й группы соединен соответственно с входом третьего основного сумматора q-й группы, с первым входом четвертого подключающего элемента И v-й группы, с первым входом направляющего элемента ИЛИ v-й

группы (т.Ф-4, 8. 122п-8), выход третьего

формирующего элемента s-й группы соеди- S-PH с первым входом первого под ,ючаю- ш-;го элемента МЛ И q-й группы, с в.;одсм t5-ro направляющего элемента ИЛИ /-и группа (. 9, 1Г-1. . . 2п-7). выход (3(г4)- 4- 3) го формирующего элемента s-й группы соединен соответственно с первым входом f/2-го подключающего элемента ИЛИ q-й группы и первым еходом f/2-ro направляющего элемента ИЛИ v-й 10уппы, выход Ij- lM-ro формирующего элемента s-й группы соединен соответственно с первым входом (f/2i-1)-ro подключающего элемента ИЛИ q-й группы ч входом (f/24 1)-го направляющего элемента ИЛИ v-й группы, выход (3(j-4)/2-2)-го формирующего элемента s-й группы соединен соответственно с первым входом (f/2-i2)-ro подключающего элемента ИЛИ q-й группы и первым входом (f/2 + 2)-ro направляющего элемента ИЛИ v-й группы, выход (j -U 4+1 j-ro формирующего элемента s-й группы соединен соответственно с первым входом ()-го подключающего элемента ИЛИ q-й группы и, первым входом (f/2+3)-ro направляющего элемента ИЛИ v-й группы, выход (j+4j/2)-3)-ro формирующего элемента s-й группы соединен соответственно с первые входом f-ro подключающего элемента

ИЛИ q-й группы, с первым входом (f-3)-ro направляющего элемента ИЛИ v-й группы. выход Q-2)-ro формирующего элемента s-й группы соединен соответственно с первым входом (h-1)-ro основного сумматора q-й группы, первым входом (f-4)-ro направляющего элемента ИЛИ (п/2-2)-й и (п/3-3)-й групп, выход (J-2)-ro формирующего элемента (п/2-1)-й группы соединен с первым входом (f-S)-ro подключающего элемента И первой группы, выход )-ro формирующего элемента s-й группы соединен с первым входом h-ro основного сумматора q-й группы и, первым входом (f-1)-ro направляющего элемента ИЛИ (п/2-2}-й и (п/2-3)-й групп, выход Q+4)/.2-2)-ro формирующего элемента (п/2-1)-й группы соединен с первым входом (М)-го подключающего элемента И первой группы, выход (|-1)-го формирующего элемента s-й группы соединен с вторым входом h-ro основного сумматора q-й группы и первым входом (f-2)-ro направляющего элемента ИЛИ (п/2-2)-й и (п/2-3)-й групп, выход Q-1)-ro формирующего элемента (п/2-1)-й группы соединен с первым входом (f-2)-ro подключающего элемента И первой группы, выход j-ro формирующего элемента s-й группы, кроме j-ro формирующего элемента n/2-й группы, соединен с первым входом w-ro полусумматора (, 7п-1) и первым входом f-ro направляющего элемента ИЛИ (п/2-2)-й и (п/2-3)-й групп, выход J-ro формирующего элемента (п/2-1)-й группы соединен с первым входом f-ro подключающего элемента И первой группы, выход j-ro формирующего элемента n/2-й группы соединен с первым входом (2п-2)-го элемента ИЛИ группы, вторые входы подключающих элементов И q-й группы объединены с первыми входами сокращающих элементов И q-й группы и инверсными входами элементов запрета q-й гркппы и соединены с выходом q-ro элемента запрета, вторые входы сокращающих гл-х элементов И q-й группы и т-х элементов запрета q-й группы соединены с вы ходами суммы соответствующих дополнительных сумматоров q-й группы, выходы т-х сокращающих элементов И q-й группы соединены с входами соответствующих элементов q1-x ИЛИ группы (q1 22n-3), вход

(f1+4)-ro подключающего элемента И v-й группы соединен соответственно с выходом f1-ro направляющего элемента ИЛИ v-rpyn- пы (f 1-1, 2f), выход каждого из подключающих элементов И q-й группы соединен с первым входом соответствующего подключающего элемента ИЛИ q-й группы, выход

0

5

0

5

0

5

0

5

0

5

которого соединен с входами соответст вую- щих основного сумматора q-й группы, выход первого элемента запрета q группы соединен с первым входом первого дополнительного сумматора q-й группы, выход суммы которого соединен с соответствующим входом (vH)-ro четного элемента ИЛИ группы, выход суммы второго дополнительного сумматора q-й группы соединен с соответствующим входом (v+2)-ro нечетного элемента ИЛИ группы, второй вход каждого основного сумматора q-й группы, кроме основных сумматоров первой группы, соединен с выходом соответствующего элемента запрета этой же группы, выход h-ro элемента запрета q-й группы, кроме h-ro элемента запрета (п/2-1)-й группы, соединен с вторым входом соответствующего полусумматора, выход переноса w-ro полусумматора соединен с вторым входом (w-1)-ro полусумматора, выход второго элемента запрета (п/2-1)-й группы соединен с вторым входом п-го полусумматора, выход переноса которого соединен с вторым входом первого дополнительного сумматора (п/2-1)-й группы , выход третьего элемента запрета (п/2-1)-й группы соединен с первым входом третьего дополнительного сумматора (п/2-1)-й группы, выход переноса которого соединен с вторым входом второго дополнительного сумматора (п/2-1)-й группы, выход четвертого элемента запрета (п/2-1)-й группы соединен с первым входом третьего полусумматора, выход переноса которого соединен с вторым входом второго полусумматора, выход переноса второго полусумматора соединен с вторым входом второго дополнительного сумматора (п/2-1)-й группы выход переноса которого соединен с третьим входом первого дополнительного сумматора (п/2-1)-й группы, выход суммы первого полусумматора соединен с третьим входом второго дополнительного сумматора (п/2-1)-й группы, выход суммы третьего дополнительного сумматора (п/2-1)-й группы соединен с первым входом второго полусумматора, выход суммы которого соединен с соответствующим входом п-го элемента ИЛИ группы, выход суммы третьего полусумматора соединен с соответствующим входом (п + 1)-го элемента ИЛИ группы, выход переноса (2п-2)-го основного сумматора первой группы соединен с вторым входом п-го полусумматора, выход суммы которого соединен с вторыми входами (2п-4)-го сокращающего элемента И и (2п-4)- го элемента запрета первой группы, выход переноса первого основного сумматора первой группы соединен с первым входом первого элемента ИЛИ группы выход которого соединен с входом первого разряда 2п-разрядного регистра результата, выход (d-1)-ro элемента ИЛИ группы соединен с входом d-ro разряда 2п-разрядного регистра результата, d(32п-3), выход первого

разряда которого соединен с вторым входом первого элемента ИЛИ группы, третий вход первого элемента ИЛИ группы соединен с выходом переноса первого дополнительного сумматора первой группы, выход суммы которого соединен с входом второго разряда 2п-разрядного регистра результата, выход второго разряда которого соединен с вторым входом первого основного сумматора первой группы, выход переноса первого дополнительного сумматора q-й группы соединен соответственно с третьим входом первого основного сумматора q-й группы, выход суммы (2п-2}-го основного сумматора первой группы соединен с входом (2п-1)-го разряда 2п-разрядного регистра результата, выход которого соединен с третьим входом (2п-2)-го основного сумматора первой группы, выход переноса каждого основного сумматора q-й группы, кроме первого и (2п-2)-го основных сумматоров первой группы, соединен с вторым входом соответствующего дополнительнот сумматора q-й группы, выход переноса w1-ro полусумматора ( n) соединен

5

соответственно с третьим входом h-ro дополнительного сумматора s-й группы, выход переноса Ы-го дополнительного сумматора s-й группы, кроме первых дополнительных сумматоров каждой s-й группы, соединен соответственно с третьим входом (h1-1)-ro дополнительного сумматора s-й группы (М 1, 2h), выход суммы Ы-го основного

0 сумматора q-й группы, кроме основных сумматоров первой группы и h-x основных сумматоров каждой q-й группы, соединен соответственно с первым входом (М + 1)-го дополнительного сумматора (q+1)-u группы, выход суммы h-ro основного сумматора q-й группы, кроме (2п-2)-го основного сумматора первой группы, соединен с первым входом (w-1)-ro полусумматора, выход суммы которого соединен с соответствующим вхо0 дом (n+w+1)-ro четного элемента ИЛИ группы, выход суммы w-ro полусумматора соединен с соответствующим входом (n+w+2)-ro нечетного элемента ИЛИ группы, выход(2п-2)-го элемента ИЛИ группы соединен с входом 2п-го разряда 2п-разрядного регистра результата, выход которого соединен с вторым входом (2п-2)-го элемента ИЛИ группы, вход n-го разряда второго п-разряд- ного кольцевого pernci pa сдвига соединен с вторым управляющим входом устройства.

5

/-Г1В

ОО Т

со

1Г

to

.. 1 Г f 6 it /я | и-в I | ...

МЪ1 -

гг

. I SWfWZ n

1гпф

W ij rg|

со т

со LH

СС

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1654815A1 |

| Устройство для умножения | 1989 |

|

SU1735842A1 |

| Устройство для умножения | 1987 |

|

SU1444755A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для умножения | 1982 |

|

SU1123031A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств электронных вычислительных машин. Цель изобретения - расширение функциональных возможностей зз счет выполнения умножения при вводе л-разрядных сомножителей по I входам в п-ра ряднике регистра множимого и множителя (.2,. ,,п). Устройство содержит два п-разрядных кольцевых регистра сдвига, п-1 элементов И, п фиксаторов режима работы, п-1 элементов запрета, две группы из п элементов И-ИЛИ, n-разрядный регистр множимого, n-разрядный регистр множителя, п/2 групп формирующих элементов, (п/2-2) групп направляющих элементов ИЛИ, (п/2- 1) групп подключающих элементов И. (п/2- 1) групп подключающих элементов ИЛИ, (п/2-1) групп основных сумматоров, п/2 дополнительных сумматоров, п полусумматоров, (п/2-1) групп сокращающих элементов И, (п/2-1) групп элементов запрета, группу элементов ИЛИ, 2п-разрядный регистр результата. Особенностью устройства является сохранение способности выполнения операции умножения при подаче множимого и множителя по одному, по нескольким или по всем входам в регистры множимого и множителя. При этом быстродействие выполнения умножения устройством возрастает прямо пропорционально увеличению числа входов i. 4 ил.. 5 тзбл Ё

| Устройство для умножения | 1987 |

|

SU1444755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-23—Публикация

1989-06-05—Подача