4 4i 4i

сл

О1

Изобретение относится к вычислительной технике, в частности к устройствам умножения, и может быть использовано при построении арифмети ческих устройств электронных вычислительных машин.

Цель изобретения - повьшение быстродействия устройства.

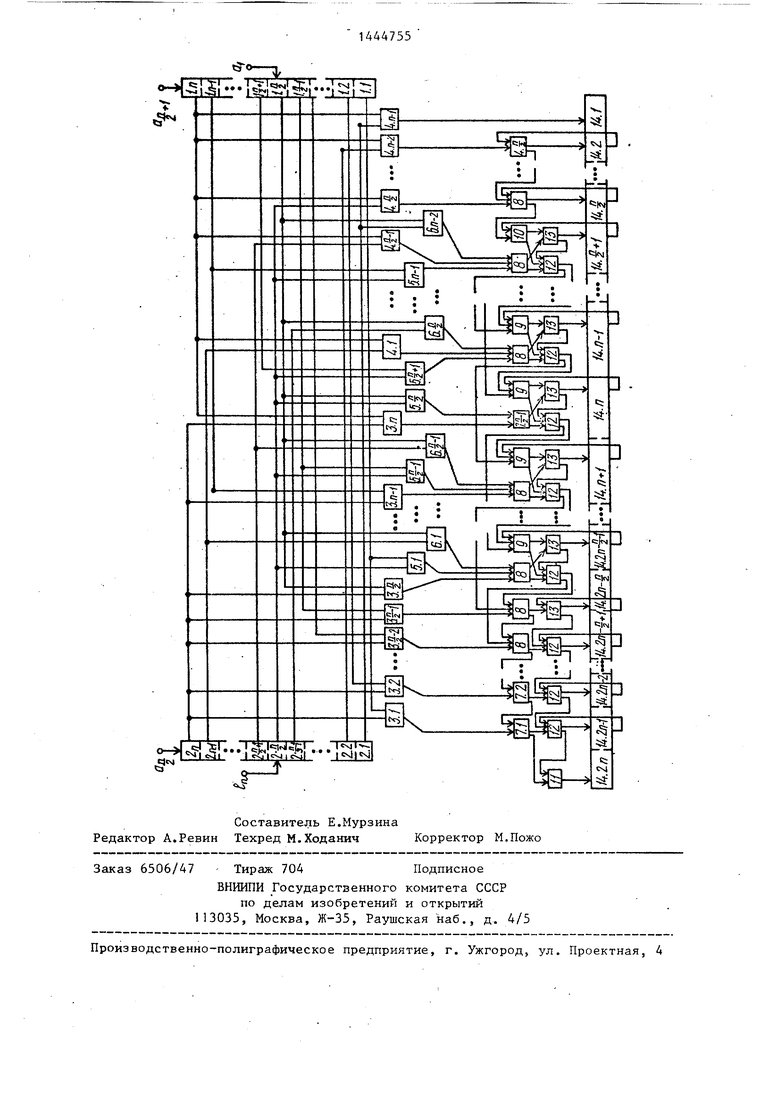

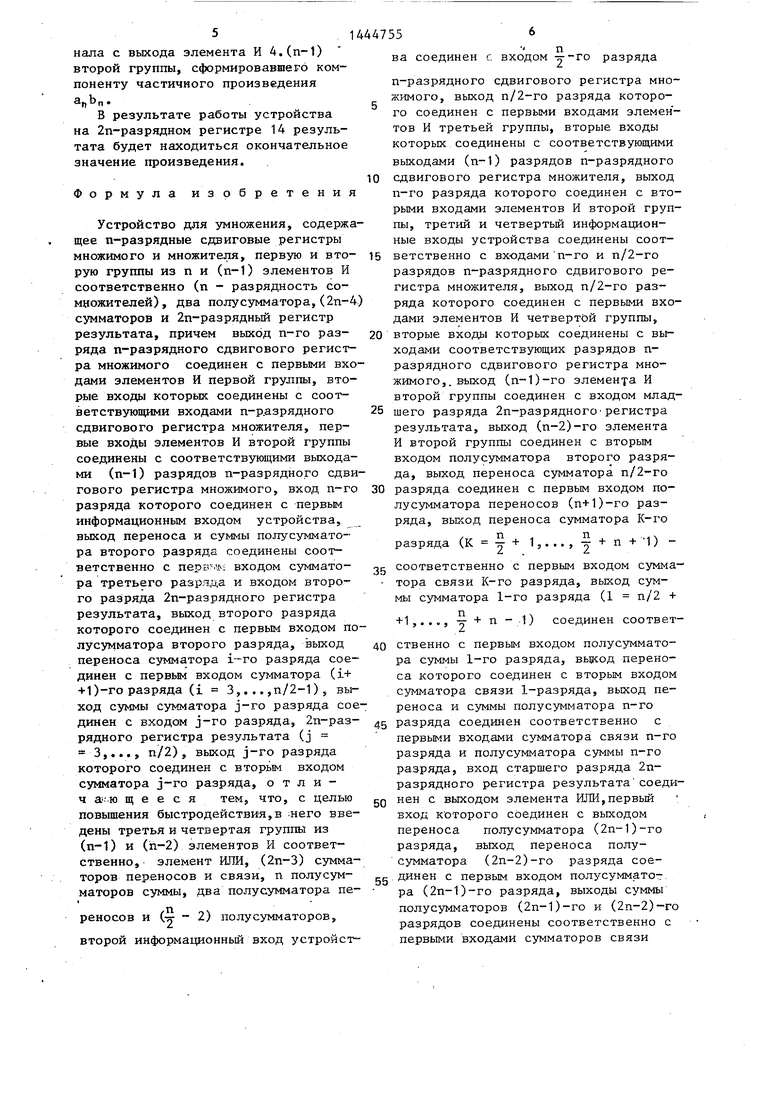

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит п-разрядный сдвиговьй регистр 1 множителя, п-разрядный сдвиговьй регистр 2 множимого, четыре группы 3-6 из п, (п-1), (п-1) и (п-2) элементов И соответственно, где п - разрядность сомножителей, у полусумматоров 7, (п + --2)

сумматоров 8, (п-3) сумматоров 9 пе- реносов, два полусумматора 10 переносов, элемент ИЛИ 11, (п + у - 2)

сумматоров 12 связи, п полусумматоров 13 суммы и 2п-разрядньй регистр 14 результата.

Устройство работает следующим образом.

В исходном состоянии регистры ус г- ройства обнулены.

---.

Множитель А 1 i a2,...,aaj., , ..., а„ последовательно подается на третий и четвертый вхо;з 1 устройства, причем на четвертьпй вход, начиная со старшего разряда, а на третий вход,

начиная с (у + 1)-го разряда.

Одновременно множимое В Ь, , b ,..., b п Ь ) последовательно

подается на первый и второй входы

устройства, причем на первьй вход, начиная с младшего разряда, а на втоn

рой вход, начиная с (у + 1)-го разряда.

В каждом такте (одновременно с записью разряда сомножителей) в п-раз- рядном сдвиговом регистре 1 множителя и п-разрядном сдвиговом регистре 2 множимого происходит сдвиг информации на один разряд в сторону младших разрядов.

Сигнал с выхода старшего разряда п-разрядного сдвигового регистра 1 множителя поступает на в горые .входы элементов И З.п, 4.1, 4.2,...,4.п,

а сигнал с выхода у -го разряда это

го регистра поступает на входы элементов И 3 Y 6.1, 6.2,..., 6(п-2).

Сигнал с выхода старшего разряда п-разрядного сдвигового регистра 2 множимого поступает на входы элементов И 3.1, 3.2,..., З.п, а сигнал с

п выхода у-го разряда этого регистра

поступает на входы элементов И 5.1, 5.2,..., 5(п-1), 4j.

В результате на выходах элементов И первой, второй, третьей и четвертой групп формируются в каждом такте компоненты частичных произведений, причем в,одном такте формируются не более трех одинаковых по весу компонент.

т,п „

В первом такте в у-и разряд празрядного сдвигового регистра 1 множителя будет записано значение старшего разряда а сомножителя А, а в

п-й разряд - значение (у + 1)-го разряда а сомножителя .А. Одновре.1 менно в старший разряд п-разрядного

сдвигового регистра 2 множимого будет записано значение среднего разряда b „ сомножителя В, а в

п „

у-и- разряд - значение младшего разряда Ъ„ сомножителя В.

На выходах элементов И 3sy, 5«у,

, 5ё(п-1) формируются компоненты первого частичного произведения

,, ,

а ib«, an b . а b

1г - i г

45

,„

55

1 п U 4.1 п

г - 1 На сумматорах 8 и полусумматорах 7

они просуммируются с промежуточным значением суммы частичных произведений (в первом такте ее значение нулевое) и результат в виде первой промежуточной суммы записьгоается в 2п-разрядный регистр 14 результата. Во втором такте (одновременно

со сдвигом информации) в у -и разряд

п-разрядного сдвигового регистра 1 множителя будет записано значение разряда а сомножителя А, в п-й разрдд - значение (у + 2)-го разряда а„ сомножителя А, а в старший разряд п-разрядного сдвигового регист , 14А4755

pa 2 множимого будет записано значе-at, .Ьц, .; , а „.,., ;...,

ние ( - 1)-го разряда Ьп сомножи-...., an .Ьг,, , an а,Ь„. , .,

теля В, в средний разряд - значение .. а,-., Ь.,- ; .-, , an,bn.i , (n-l)-ro разряда b h., сомножителя В. ,, а ь

2.4.1° ч +,--, П-; -i +1

На вькодах элементов И З.(у - 1),. . , ,,, а-Ъп, а.Ь,.,., , ...-,

3.f, 6.1, 3.(п-1), 5.(-1),з.п,5., аь аЬ

пп п ь-1 1

4.1, 6.-J, 5.(п-1), A.-J и 4.(+ 1) сумматорах 8, полусумматорах 7,

формируются компоненты второго час-сумматорах 9 переносов, полусумматотичного произведения: .., ;рах 10 переносов, сумматорах 12 связи

ajbn , ; а Ьц., ,Ьь., ;и полусумматорах 13 суммы с помощью

1 г -г 15элемента ИЛИ 11 компоненты i-ro 2., uj.1 2°п тичного произведения суммируются со

f- л-л.., W

а

п b , а„ Ь., , а„ Ъп. На сум- значениями (i-l)-ft промежуточной

г 2 суммы. В 2п-разрядный регистр 14 рематорах 8, полусумматорах 7 разря-зультата записьшается значение i-й

дов и полусумматорах 13 сумм эти промежуточной суммы.

поненты суммируются вместе с первой

промежуточной суммой частичных про-В такте (одновременно со

изведений и р-езультат в виде второйсдвигом информации) в -й разряд

промежуточной суммы записывается в

2п-разрядный регистр 14 результата.25 Разрядного сдвигового регистра 1

В i-oM такте (одновременно сомножителя будет записано значение

сдвигом информации) в разряд разряда а „ сомножителя А, в

i . разрядного сдвигового регистра 1 мно- п-й разряд - значение п-го разряда

жителя будет записано значение i-ro30 сомножителя А, а в п-й разряд празряда а - сомножителя А, в п-й раз-разрядного сдвигового регистра 2

.п .множимого будет записано значение

ряд - значение ( + 1 + i)-ro разря-старшего разряда Ь, сомножителя В,

да а , ; сомножителя А, а в п-йв |-й разряд - значение Н-го раз- разряд п-разрядного сдвигового реги-35 ряда Ь„ сомножителя, стра 2 множимого будет записано зна-i

-п ..На выходах элементов И первой,

чение ( - ibro разряда Ь„. сомно-второй, третьей и четвертой групп

жителя В, в -й разряд - значениеформируются компоненты -го частичf г.40 .2

° с-1) сомножите-„ произведения: а,Ь/, ,...,

. , ,... , На выходах элементов И 3.( + 1), ,..., а.Ь,,, , а„Ь,

3.(-i +2),..., 3.(n-i+1), 3.(n-i+..., а,Ь.

. . I i

+2),..., З.п, 4.1, 4.2,...,4.(i-1),цд сумматорах 8, полусумматорах

4.(2.- 1); 4.; 4. (2-+ i - 1), 5. (2.- 7, сумматорах 9 переносов, полусум п . п, f .маторах 10 переносов, сумматорах 12

-1+1), S.CY - 1 + 2),..., 5.-, 5.(п-связи и полусумматорах 13 суммы с

-i+1), 5.(n-i+2),..., 5.(n-1); 6.1;5° помощью элемента ИЛИ 11 компоненты

6.2;..., 6.1, 6.(у- 1), б.у,..., частичного произведения сум... 6.(j- + 1 - 1), формируются ком-мируются вместе с (у - 1)-й промепоненты i-ro частичного произведения:gg жуточной суммой частичных произвеа .Ь . ; аг, . b „.,..., а(,.,Ь„ .;Дений и значение результата запи1 г г ,1 сывается в 2п разрядный регистр 14

Ич. |-,- 1-1 -i результата, причем в младший его

разряд записывается значение сиг

.;; а,Ь,.; ап,;Ь„,. ; а„.Ь.;

нала с выхода элемента И 4.(п-1) второй группы, сформировавшего компоненту частичного произведения а„Ьп.

В результате работы устройства на 2п-разрядном регистре 14 результата будет находиться окончательное значение произведения.

Формула изобретения

Устройство для умножения, содержащее п-разрядные сдвиговые регистры множимого и множителя, первую и вто- рую группы из п и (п-1) элементов И соответственно (п - разрядность сомножителей), два полусумматора,(2п-4 сумматоров и 2п-разрядньй регистр результата, причем выход п-го раз- ряда п-разрядного сдвигового регистра множимого соединен с первыми входами элементов И первой грулпы, вторые входы которых соединены с соот- ветствуюпщми входами п-р.азрядного сдвигового регистра множителя, первые входы элементов И второй группы соединены с соответствующими выходами (п-1) разрядов п-разрядного сдвигового регистра множимого, вход п-го разряда которого соединен с первым информационным входом устройства, выход переноса и суммы полусумматора второго разряда соединены соответственно с первмл; входом суммато- ра третьего разряда и входом второго разряда 2п-разрядного регистра результата, выход второго разряда которого соединен с первым входом полусумматора второго разряда, выход переноса сумматора i-ro разряда соединен с первым входом сумматора (1+ + 1)-го разряда (i 3,, .. ,п/2-1) , выход суммы сумматора j-ro разряда соединен с входом j-ro разряда, 2п-раз- рядного регистра результата (j 3,..., п/2), выход j-ro разряда которого соединен с вторьм входом сумматора разряда, о т л и - ч а -ю щ е е с я тем, что, с целью повышения быстродействия,в ;него введены третья и четвертая группы из (п-1) и (г1-2) элементов И соответственно, элемент ИЛИ, (2п-3) сумматоров переносов и связи, п полусум- маторов суммы, два полусумматора пе-

реносов и (-у - 2) полусумматоров, второй информационный вход устройст

ва соединен с: входом у-го разряда

п-разрядного сдвигового регистра множимого, выход П/2-ГО разряда которого соединен с первыми входами элемен - тов И третьей группы, вторые входы которых соединены с соответствующими выходами (п-1) разрядов п-разрядного сдвигового регистра множителя, выход п-го разряда которого соединен с вторыми входами элементов И второй группы, третий и четвертый информационные входы устройства соединены соответственно с входами п-го и п/2-го разрядов п-разрядного сдвигового регистра множителя, выход п/2-го разряда которого соединен с первыми входами элементов И четвертой группы, вторые входы которых соединены с выходами соответствующих разрядов п- разрядного сдвигового регистра множимого,, выход (n-l)-ro элемента И второй группы соединен с входом младшего разряда 2п-разрядного регистра результата, выход (п-2)-го элемента И второй группы соединен с вторым входом полусумматора второго разряда, выход переноса сумматора п/2-го разряда соединен с первым входом полусумматора переносов (п+1)-го разряда, выход переноса сумматора К-го

разряда (К + 1.,. .. , + п + 1) соответственно с первым входом сумматора связи К-го разряда, выход суммы сумматора 1-го разряда (1 п/2 + п

+1,,.., + п -,1)

соединен соответственно с первым входом полусумматора суммы 1-го разряда, вь1гсод переноса которого соединен с вторьм входом сумматора связи 1-разряда, выход переноса и суммы полусумматора п-го разряда соединен соответственно с первыми входами сумматора связи п-го разряда и полусумматора суммы п-го разряда, вход старшего разряда 2п- разрядного регистра результата соединен с выходом элемента ИЛИ,первый вход к оторого соединен с выходом переноса полусумматора (2п-1)-го разряда, выход переноса полусумматора (2п-2)-го разряда соединен с первым входом полусуммато-г. ра (2п-1)-го разряда, выходы суммы полусумматоров (2п-1)-го и (2п-2)-го разрядов соединены соответственно с первыми входами сумматоров связи

714447558

(2п-1)-го и (2п-2)-го разрядов, вы- выход переноса сумматора связи (2п - ход переноса сумматора связи (2п-1)-го п разряда соединен с пер- разряда соединен с вторым, входом эле- i мента ИЛИ, выходы переноса полусум- g вым входом сумматора (2п-у+ 1)-го

маторов переноса . (у + 1)-го и (-у + разряда, а выход его суммы соединен +2)-го разрядов соединены соответст- х°Д°м сумматора (2п - венно с третьими входами сумматоров - у)-го разряда, выход переноса сумсвязи (у + 1)-го и .(у + 2)-го разря- ° матора связи t-ro разряда (t 2п - ДОН, выходы суммы полусумматоров пе- 2п- 2) соединен соотреноса (у + 1)-го и (-у + 2)-го раз- ветственно с вторым входом сумматора

связи (t+1)-ro разряда, выход суммы

рядов соединены соответственно с IK,,/свторыми входами полусумматоров суммы полусумматора суммы S-ro разряда (S (f + 1)-го и q 2)-го разрядов, - 1,..., 2п - ) соединен соответственно с входом S-ro разряда 2п- выход переноса сумматора переносовi- .к «

разрядного сдвигового регистра ре-

пг-го разряда (т - + 3,..., 2п - 0 i п

зультата, выходы (у + 1)-го и (у +

- - 1) соединен соответственно с

+ 2)-г6 разрядов которого соединены

третьим входом сумматора связи т-госоответственно с вторыми входами по- разряда, выход суммы сумматора переноса га-го разряда соединен соответстразряда, выход суммы сумматора пере-д

25 лусумматоров переносов (- + 1)-го и

венно с вторым входом полусумматора ( + 2)-го разрядов, выход R-ro раз- суммы т-го разряда, выход переносацп

,п чРЯДЗ (R у + 3,..., 2п - у - 1) 2псумматора связи ( +1)-го разряда

разрядного сдвигового регистра ре- соединен с первым входом сумматора зультата соединен соответственно с

переносов (-| + 2)-го разряда, выход третьим входом сумматора переносов

П

переноса сумматора связи р-го разря- разряда, выход (2п - 2-)-го разда (р 2. + 3, ..., 2п-у - 3) сое- 2п-разрядного сдвигового реги стра соединен с вторым входом Полудинен соответственно с первым входом л

сумматора переносов (р+2)-го разря- сумматора суммы (2п - -2 )-го разряда,.

да, выход суммы сумматоров связи р-говыход суммы сумматора связи Ь-го раз- разряда соединен соответственно сряда соединен соответственно с входом вторым входом сумматора переносов . п (р+1)-го разряда, выход переноса ° разряда ( у + 1,..., 2п-1),

сумматора связи (2п - у - 2)-го раз- 2п-разрядного сдвигового регистра результата, выход Ь-го разряда которо- ряда соединен с первым входом сумма- соединен с третьим входом сумматотора (2п - у)-го разряда, а выход его ра связи Ь-го разряда, выходы элементов И каждой группы соединены с вхо- суммы - с вторым входом сумматора соответствующих по весу разрядов

переносов (2п - у 1)-го разряда, . сумматоров и полусумматоров.

IiiE

с

., I . , , .

|5 |сулД| 1 1| м1

.

Щ-nS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1735842A1 |

| Устройство для умножения | 1989 |

|

SU1654815A1 |

| Устройство для умножения | 1989 |

|

SU1658148A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для умножения | 1987 |

|

SU1481744A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам умножения, и может быть использовано при построении ари4 1етических устройств ЭВМ. Цель изобретения - повьшение -быстродействия. Устройство содержит п-разрядные сдвиговые регистры множителя и множимого, четыре группы из п, п-1, п-1 и п-2 элементов И, h + - полусумматоров, элемент ИЛИ, 4п-7 сумматоров, 2п-разрядный сдвиговый ре гистр результата. Новым в устройстве является введение каждого сомножителя по двум входам в регистр, отсутствие связей между (у + 1)-м и -у разрядами регистров сомножителей, что дает возможность в два раза уменьшить общее число тактов работы. 1 ил. i СЛ

| Самофалов К.Г. | |||

| и др | |||

| ЦЭВМ, Киев, 1983, с | |||

| Способ получения древесного угля | 1921 |

|

SU313A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для умножения | 1984 |

|

SU1203512A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-15—Подача