Изобретение относится к вычислительной и информационной технике и предназначено для обмена информацией между ЭВМ и внешней памятью.

Известно устройство для управления обмена процессора с памятью, содержащее два счетчика адреса, триггер, генератор импульсов, два блока элементов И, четыре элемента И, два блока элементов ИЛИ, три элемента задержки, распределитель импульсов и два блока памяти.

Наиболее близким техническим решением к предлагаемому является устройство сопряжения ЭВМ с внешней памятью, содержащее устройство согласования, устройство управления магистралью, схему опознания, устройство управления, регистр адреса, мультиплексор данных, формирователь ректирующих разрядов, дешифратор, корректор и формирователь временных

стробов. Это устройство позволяет записывать и кодировать информацию по коду Хэмминга 21-16-5, передаваемую во внешнюю память из ЭВМ с шиной МПИ, а также считывать и декодировать информацию, принимаемую из внешней памяти в канал ЭВМ. Устройство сопряжения является портом связи ЭВМ с внешней памятью и занимает в адресном пространстве ЭВМ область памяти в 4К (4096) 16-разрядных слов.

Недостатком известного устройства является большая часть памяти, отводимая в адресном пространстве ЭВМ для связи с внешней памятью.

Цель изобретения - расширение ад- ресного пространства ЭВМ при работе с внешней памятью.

Устройство для сопряжения ЭВМ с внешней памятью содержит регистр адреса, усилитель корректирующих кодов, дешифратор сигналов управления, форvj,

00

ел

00 3

мирователь временных стробов и мультиплексор данных. Благодаря совмест- - ной работе устройства сопряжения с параллельным 16-разрядным интерфейсом в составе ЭВМ адресное пространство, отводимое под порт связи в ЭВМ с внешней памятью, сокращается с 09б до 3 16-разрядных слов,

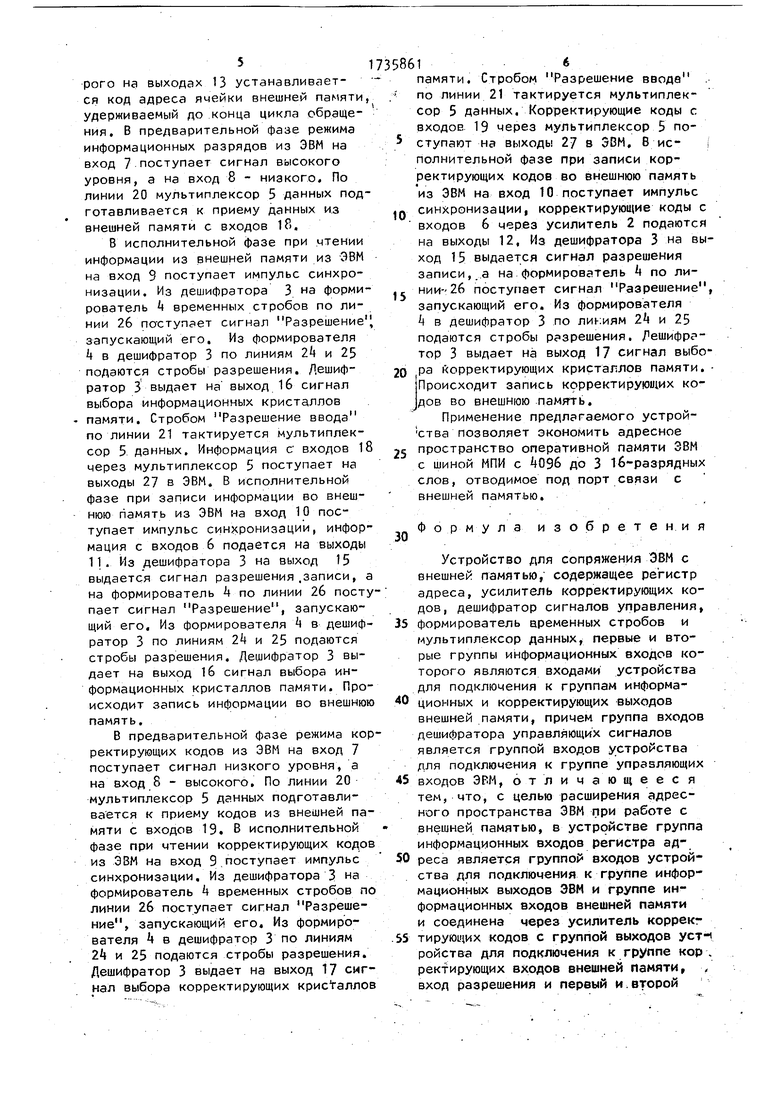

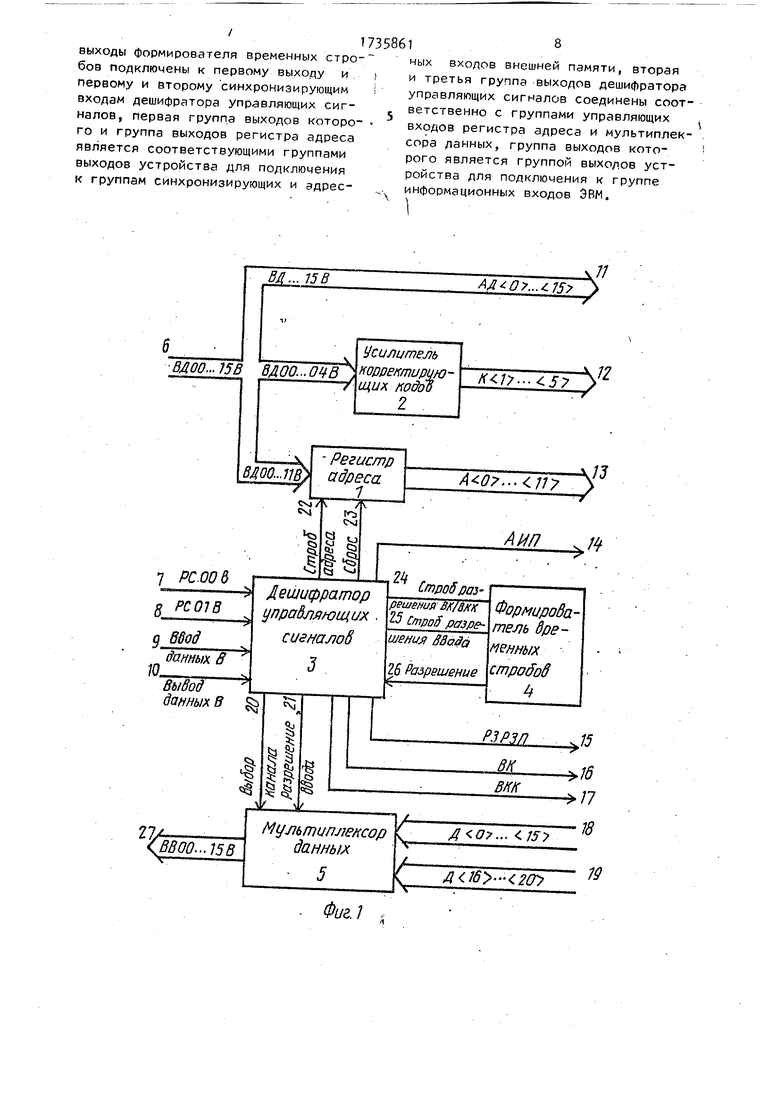

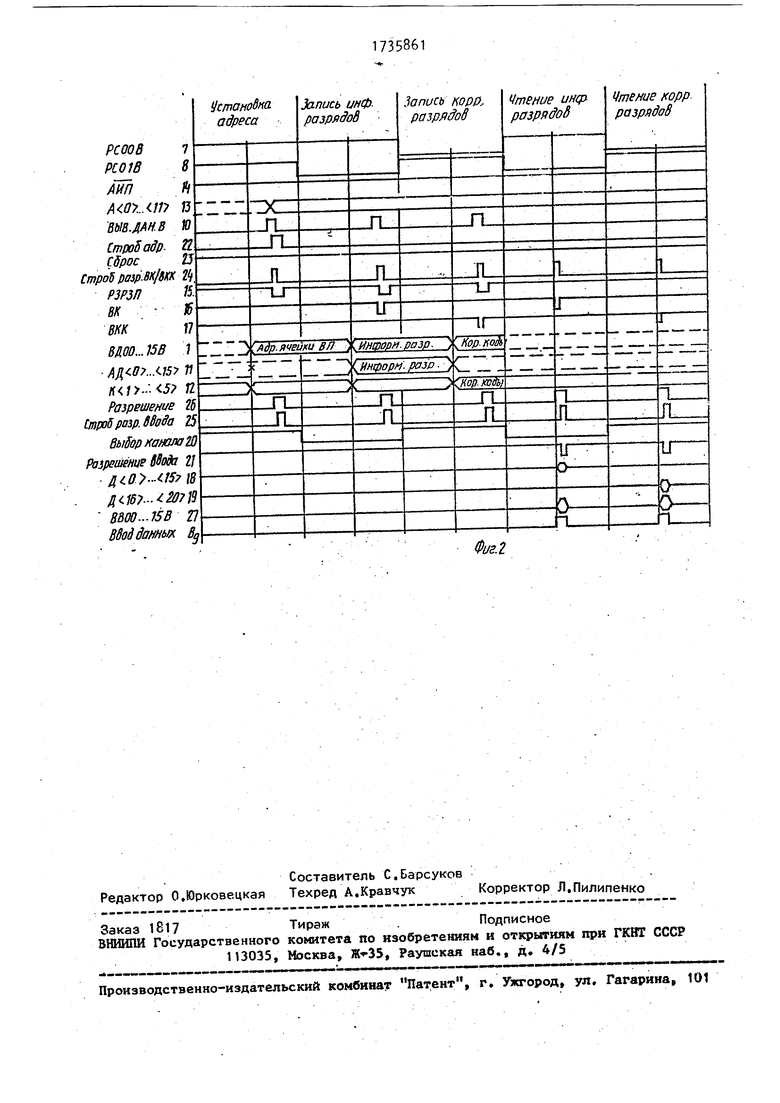

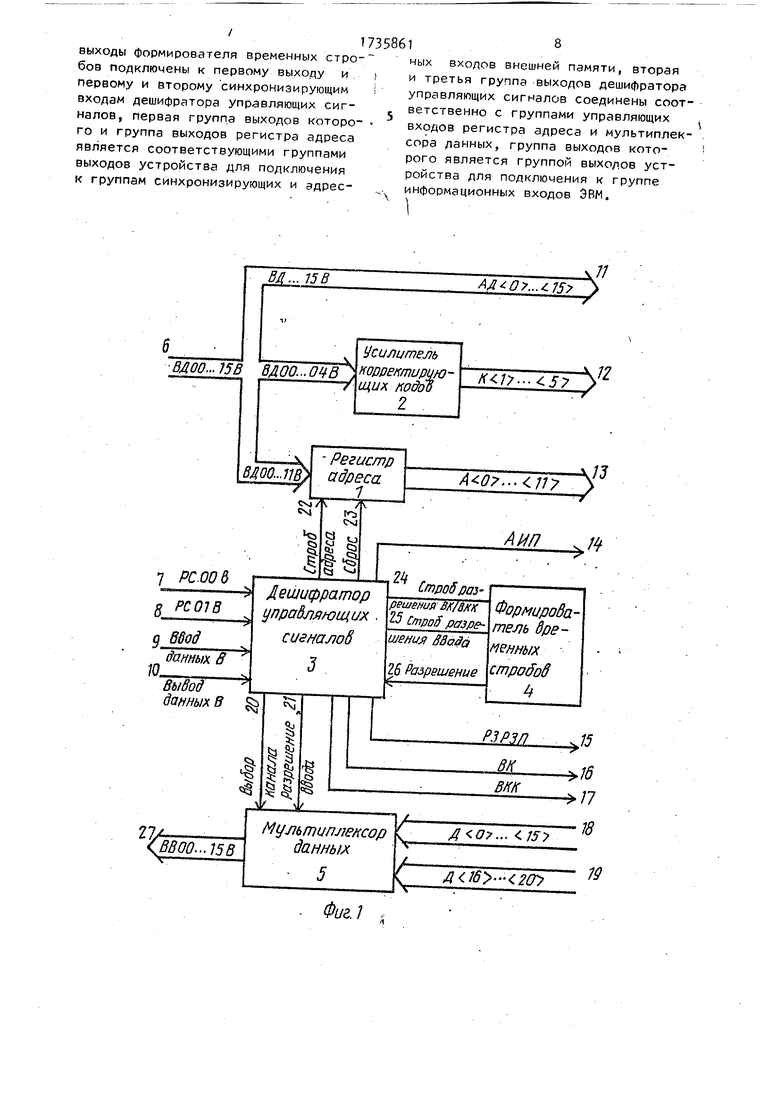

На фиг.1 приведена функциональная схема устройства для сопряжения ЭВМ с внешней памятью; на фиг.2 - цикл обращения к внешней памяти.

Устройство для сопряжения ЭВМ с внешней памятью содержит регистр 1 адреса усилитель 2 корректирующих кодов, дешифратор 3 управляющих сигналов, формирователь k временных стробов, мультиплексор 5 данных, 16-разрядную шину 6 входов от ЭВМ (ВДОО ... 15В), вход 7 от нулевого разряда регистра состояния ЭВМ (РСООВ), вход 8 от первого разряда регистра состояния ЭВМ (РС01В), вход 9 от ЭВМ Ввод данных В 9, вход 10 от ЭВМ Вывод данных В, 16-разрядную шину 11 выходов информационных сигналов данных на внешнюю память (АД 00 ... 15), пятиразрядную шину 12 выходов корректирующих кодов на внешнюю память (l« 1 ... 5), двенадцатиразрядную шину 13 адресных выходов на внешнюю память ( ... ... :11), выход 1 на внешнюю память - авария источника питания (АИП), выход 15 на внешнюю память, разрешаю- щий запись информации (РЗРЗП), выход 16 на внешнюю память- выбор информационных .кристаллов (ВК), выход 17 на внешнюю память - выбор корректирующих кристаллов (ВКК), 16-разрядную шину 18 информационных входов с внешней памяти (Л 0 ... 15), пятиразрядную шину 19 входов корректирующих кодов с внешней памяти (Л«Ј1б ,,, ... :20), линию Выбор канала 20 чтения, линию Разрешение ввода 21, линию Строб адреса 22, линию Сброс 23, линию Строб разрешения ВК/ВКК 2k, линию Строб разрешения ввода 25, линию Разрешение 26, 16-разрядную шину 27 выходов на ЭВМ (ВВОО ... 15В).

16 разрядов данных при записи в память передаются непосредственно

10

15

20

25

наются в регистре 1 адреса и удер живаются на выходах 13 на время в цикла обращения к памяти.

Чтение данных из памяти осущес вляется с входов 18 и 19. Через м типлексор 5 данные поступают на в ды 27 в ЭВМ. Управление установко адреса, записью и чтением информа осуществляется дешифратором 3 упр ляющих сигналов, на который с вхо 7 - 10 от ЭВМ подаются управляющи сигналы. Синхронизацию работы деш ратора 3 управляющих сигналов ос ствляет формирователь k временных стробов по линиям 2 - 26. Управл ние регистром 1 адреса дешифратор управляющих сигналов производит п линиям 22 и 23, а мультиплексором 5 данных - по линиям 20 и 21. Управление внешней памятью дешифрат ром 3 управляющих сигналов осущес вляется с выходов 1 - 17.

Работа устройства характеризуе ся двумя циклами: циклом хранения информации и циклом обращения к я ке внешней памяти. В цикле хранен на входы 7 и 8 устройства из ЭВМ подаются сигналы низкого уровня. шифратор 3 управляющих сигналов п линии 23 производит начальную установку регистра 1 адреса и по вы ходу запрещает обращение к вне ней памяти. Цикл обращения к внеш памяти подразделяется на три режи режим установки адреса, режим инф мационных разрядов и режим коррек тирующих кодов. Каждый из режимов разделяется на две фазы: предвари ную и исполнительную. В режиме ус новки адреса наличие двух фаз обя тельно они следуют одна за друг В двух других режимах предварител ная фаза необязательна, если она

45 ла установлена и не было перехода другой режим работы. Исполнительн фаза в этих режимах возможна в дв видах - записи и чтения. Первым в цикле обращения к внешней памяти

50 является режим адреса. В предвари тельной фазе режима адреса на вхо 7 и 8 из ЭВМ поступают сигналы вы сокого уровня, В исполнительной ф на входы 6 из ЭВМ поступает код а

30

35

40

входов 6 на выходы 11, 5 младших раз- 55 реса ячейки внешней памяти, а на

рядов через усилитель 2 корректирующих кодов передаются с входов 6 на выходы 12 для записи в память. 12 младших разрядов с входов 6 запомивход 10 - импульс синхронизации. дешифратора 3 управляющих сигнало регистр 1 адреса по линии 22 пода ся строб адреса , по приходу кот

5

0

наются в регистре 1 адреса и удер- живаются на выходах 13 на время всего цикла обращения к памяти.

Чтение данных из памяти осуществляется с входов 18 и 19. Через мультиплексор 5 данные поступают на выходы 27 в ЭВМ. Управление установкой адреса, записью и чтением информации осуществляется дешифратором 3 управляющих сигналов, на который с входов 7 - 10 от ЭВМ подаются управляющие сигналы. Синхронизацию работы дешифратора 3 управляющих сигналов осуществляет формирователь k временных стробов по линиям 2 - 26. Управление регистром 1 адреса дешифратор 3 управляющих сигналов производит по линиям 22 и 23, а мультиплексором 5 данных - по линиям 20 и 21. Управление внешней памятью дешифратором 3 управляющих сигналов осуществляется с выходов 1 - 17.

5

Работа устройства характеризуется двумя циклами: циклом хранения информации и циклом обращения к ячейке внешней памяти. В цикле хранения на входы 7 и 8 устройства из ЭВМ подаются сигналы низкого уровня. Дешифратор 3 управляющих сигналов по линии 23 производит начальную установку регистра 1 адреса и по выходу запрещает обращение к внешней памяти. Цикл обращения к внешней памяти подразделяется на три режима: режим установки адреса, режим информационных разрядов и режим корректирующих кодов. Каждый из режимов разделяется на две фазы: предварительную и исполнительную. В режиме установки адреса наличие двух фаз обязательно они следуют одна за другой. В двух других режимах предварительная фаза необязательна, если она бы5 ла установлена и не было перехода на другой режим работы. Исполнительная фаза в этих режимах возможна в двух видах - записи и чтения. Первым в цикле обращения к внешней памяти

0 является режим адреса. В предварительной фазе режима адреса на входы 7 и 8 из ЭВМ поступают сигналы высокого уровня, В исполнительной фазе на входы 6 из ЭВМ поступает код ад0

5

0

вход 10 - импульс синхронизации. Из дешифратора 3 управляющих сигналов в регистр 1 адреса по линии 22 подается строб адреса , по приходу кото5

рого на выходах 13 устанавливается код адреса ячейки внешней памяти, удерживаемый до конца цикла обращения. В предварительной фазе режима информационных разрядов из ЭВМ на вход 7 поступает сигнал высокого уровня, а на вход 8 - низкого. По линии 20 мультиплексор 5 данных подготавливается к приему данных из внешней памяти с входов 18,

В исполнительной фазе при чтении информации из внешней памяти из ЭВМ на вход 9 поступает импульс синхронизации. Из дешифратора 3 на формирователь Ц временных стробов по линии 26 наступает сигнал Разрешение запускающий его. Из формирователя k в дешифратор 3 по линиям 2k и 25 подаются стробы разрешения. Дешифратор 3 выдает на выход 16 сигнал выбора информационных кристаллов памяти. Стробом Разрешение ввода по линии 21 тактируется мультиплексор 5 данных. Информация с входов 18 через мультиплексор 5 поступает на выходы 27 в ЭВМ. В исполнительной фазе при записи информации во внешнюю память из ЭВМ на вход 10 поступает импульс синхронизации, информация с входов 6 подается на выходы 11. Из дешифратора 3 на выход 15 выдается сигнал разрешения .записи, а на формирователь k по линии 26 поступает сигнал Разрешение, запускающий его. Из формирователя k в дешифратор 3 по линиям 2k и 25 подаются стробы разрешения. Дешифратор 3 выдает на выход 16 сигнал выбора информационных кристаллов памяти. Происходит запись информации во внешнюю память.

В предварительной фазе режима корректирующих кодов из ЭВМ на вход 7 поступает сигнал низкого уровня, а на вход 8 - высокого. По линии 20 мультиплексор 5 данных подготавливается к приему кодов из внешней памяти с входов 19. В исполнительной фазе при чтении корректирующих кодов из ЭВМ на вход 9 поступает импульс синхронизации. Из дешифратора 3 на формирователь k временных стробов по линии 26 поступает сигнал Разрешение, запускающий его. Из формирователя k в дешифратор 3 по линиям 2k и 25 подаются стробы разрешения. Дешифратор 3 выдает на выход 17 сигнал выбора корректирующих кристаллов

358616

памяти. Стробом Разрешение ввода по линии 21 тактируется мультиплексор 5 данных. Корректирующие коды с входов 19 через мультиплексор 5 по- 5 ступают на выходы 27 в ЗВМ, В исполнительной фазе при записи корректирующих кодов во внешнюю память из ЭВМ на вход 10 поступает импульс JQ синхронизации, корректирующие коды с входов 6 через усилитель 2 подаются на выходы 12, Из дешифратора 3 на выход 15 выдается сигнал разрешения записи, а на формирователь k по ли- ., ним-26 поступает сигнал Разрешение, запускающий его. Из формирователя k в дешифратор 3 по ликиям 2k и 25 подаются стробы разрешения. Дешифратор 3 выдает на выход 17 сигнал выбо- 2о ра корректирующих кристаллов памяти. {Происходит запись корректирующих ко- дов во внешнюю память.

Применение предлагаемого устрой- ства позволяет экономить адресное 25 пространство оперативной памяти ЗВМ с шиной МПИ с 4096 до 3 16-разрядных слов, отводимое под порт связи с внешней памятью.

30

Формула изобретения

Устройство для сопряжения ЭВМ с внешней памятью, содержащее регистр адреса, усилитель корректирующих кодов, дешифратор сигналов управления,

формирователь временных стробов и мультиплексор данных, первые и вторые группы информационных входов которого являются входами устройства для подключения к группам информационных и корректирующих выходов внешней памяти, причем группа входов дешифратора управляющих сигналов является группой входов устройства для подключения к группе управляющих

входов ЭВМ, отличающееся тем, что, с целью расширения адресного пространства ЭВМ при работе с внешней памятью, в устройстве группа информационных входов регистра адреса является группой входов устройства для подключения к группе информационных выходов ЭВМ и группе информационных входов внешней памяти и соединена через усилитель коррекг

тирующих кодов с группой выходов уст-1 ройства для подключения к группе кор . ректирующих входов внешней памяти, вход разрешения и первый и.второй

выходы формирователя временных стробов подключены к первому выходу и первому и второму синхронизирующим входам дешифратора управляющих CHI налов, первая группа выходов которого и группа выходов регистра адреса является соответствующими группами выходов устройства для подключения к группам синхронизирующих и адресных входов внешней памяти, вторая и третья группа выходов дешифратора управляющих сигналов соединены соответственно с группами управляющих входов регистра адреса и мультиплексора данных, группа выходов которого является группой выходов устройства для подключения к группе информационных входов ЭВМ.

рсоов

PC018 АЙП

...Ш

ВЫВ.ДАН8

CmpoSaffff. Сдрос Строб разр.ВК/т 2$ РЗРЗП ВК ВКК

ВДОВ... 15В ...15 Я .5 П Разрешение 26 Строб рюр. 88offa 25

Выбор канатМ

Разрешение Mote 21

Д.0.М&18

JUm-.tttift

BBOO...J5B

Вводимых 83

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

Изобретение относится к вычислительной, и информационной технике и предназначено для обмена информацией между ЭВМ и внешней памятью. изобретения - расширение адресного пространства ЭВМ при работе с внешней памятью. Устройство для сопряжения ЭВМ с внешней памятью содержит регистр адреса, усилитель корректирующих кодов, дешифратор сигналов управления, формирователь временных стробов и мультиплексор данных. Благодаря использованию устройства адресное пространство, отводимое под порт связи ЭВМ с внешней памятью, сокращается с 4096 до трех шестнадцатиразрядных слов. 2 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1992-05-23—Публикация

1989-07-31—Подача