Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностики логических блоков.

Цель изобретения - повышение достоверности контроля.

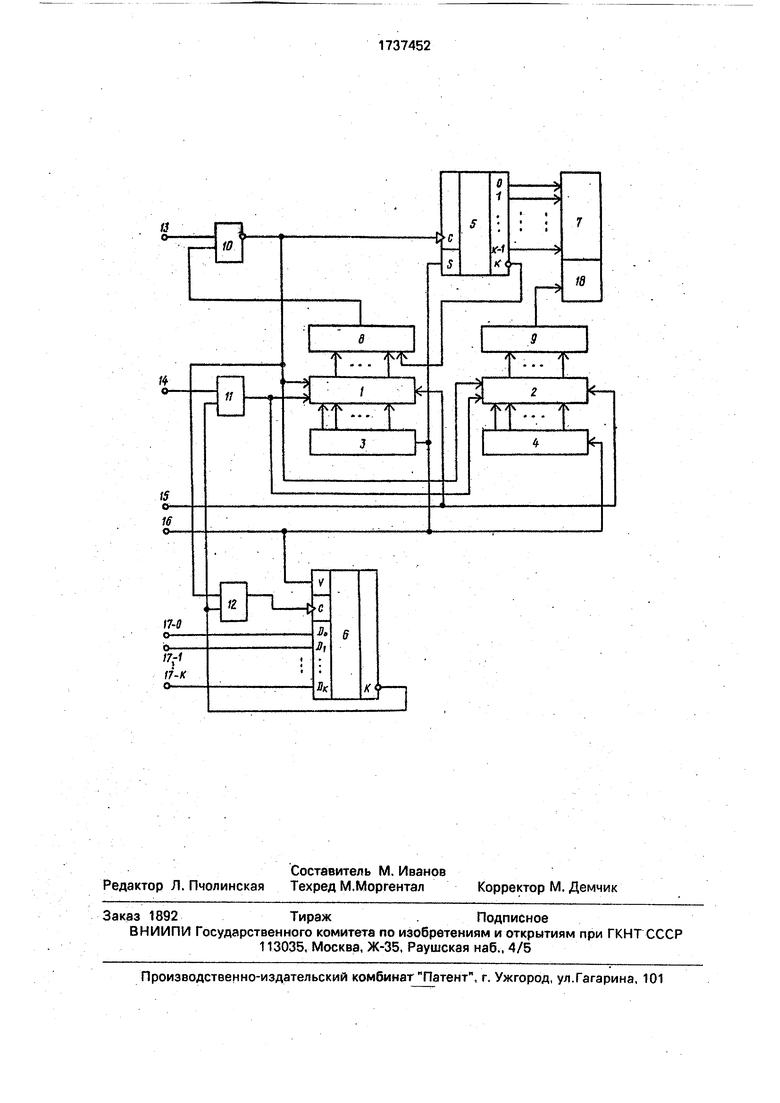

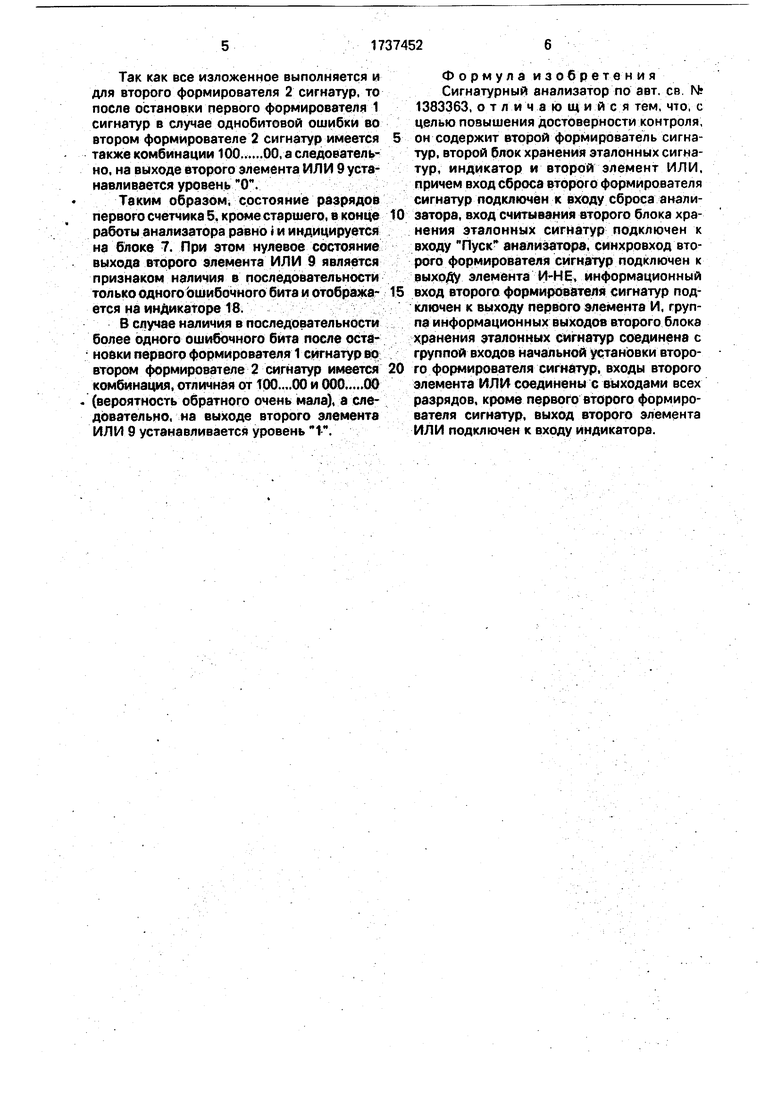

На чертеже представлена структурная схема сигнатурного анализатора.

Анализатор содержит первый 1 и второй 2 формирователи сигнатур, первый 3 и второй 4 блоки хранения эталонных сигнатур, первый 5 и второй 6 счетчики, блок 7 индикации, первый 8 и второй 9 элементы ИЛИ, элемент И-НЕ 10, первый 11 и второй 12 элементы И, синхровход 13, информационный вход 14, вход 15 сброса, вход 16 Пуск, входы 17-0,...,17-k начальной установки и индикатор 18.

Анализатор работает следующим образом.

По внешнему управляющему сигналу Сброс все разряды первого 1 и второго 2 формирователей сигнатур устанавливаются в О. По внешнему управляющему сигналу

Пуск первый счетчик 5 устанавливается в

состояние 0001, т.е. младший разряд

первого счетчика 5 устанавливается в 1, остальные разряды - в О, эталонная сигнатура с выходом первого блока 3 хранения эталонных сигнатур заносится в первый формирователь 1 сигнатур, эталонная сигнатура с выходов второго блока 4 хранения эталонных сигнатур заносится во второй формирователь 2 сигнатур и с входов начальной установки анализатора 17-017-k

во второй счетчик 6 заносится двоичный код числа N - 1, где N - длина исследуемой последовательности.

Первый и второй формирователи сигнатур представляют собой регистры сдвига с линейными обратными связями. Обратные связи должны соответствовать ненулевым коэффициентам образующих полиномов. Оба образующих полинома должны быть примитивными, кроме того, они должны быть отличными друг от друга. Например, если для первого формирователя сигнатур выбран примитивный образующий полfe

VI СО xj

.N СЛ ГО

ю

ином, то для второго формирователя сигнатур может быть принят режущий полином, двойственный (обратный) выбранному. Эталонные сигнатуры для обоих формирователей сигнатур должны быть рассчитаны для длины 2-1, независимо от длины N (k - разрядность формирователей сигнатур).

По сигналу Пуск на инверсном выходе старшего разряда второго счетчика б появляется 1 (это следует из того, что N 2 - 1), которая позволяет пропускать синхроимпульсы с выхода элемента И-НЕ 10 через элемент И 12 на вычитающий вход второго счетчика 6, а также разрешает прохождение исследуемой последовательности с информационного входа 14 анализатора через первый элемент И 11 на информационные входы первого 1 и второго 2 формирователей сигнатур. Кроме того, так как первый

счетчик 5 установлен в состояние 0001,

на инверсном выходе его старшего разряда, который соединен с одним из входов первого элемента ИЛИ 8, появляется 1. Следовательно, на выходе первого элемента ИЛИ 8 также устанавливается Г, которая пропускает через элемент И-НЕ 10 синхроимпульсы с синхровхода 13 анализатора на счетный вход первого счетчика 5 и синхровходы первого 1 и второго 2 формирователей сигнатур и первый вход элемента И 12. Таким образом, исследуемая последовательность сворачивается в первую сигнатуру на первом 1 формирователе сигнатур и во вторую сигнатуру на втором 2 формирователе сигнатур. Количество разрядов формирователей сигнатур k выбирается таким, чтобы выполнялось условие N 2k -1, где N - длина исследуемой последовательности, поступающей на информационный вход 14 сигнатурного анализатора. Первый счетчик 5 - суммирующий (k + 1)-разрядный, второй счетчик 6 - вычитающий (k + 1)-разрядный. Первый 1 и второй 2 формирователи сигнатур, первый 5 и второй б счетчики срабатывают по спаду синхроимпульсов, поступающих на синх- ровход 13 анализатора.

Через N тактов согласно принципу суперпозиции в первом 1 и втором 2 формирователях сигнатур получается первая и вторая сигнатуры ошибок. При этом на инверсном выходе старшего разряда второго счетчика 6 появляется О, который прекращает прохождение синхроимпульсов на вычитающий вход второго счетчика 6, а также запрещает поступление исследуемой последовательности на информационные входы первого 1 и второго 2 формирователей сигнатур. Однако на синхровходы первого 1 и второго 2 формирователей сигнатур продолжают поступать синхроимпульсы и первый счетчик 5 продолжает считать синхроимпульсы до тех пор, пока во всех

разрядах, кроме первого, первого формирователя 1 сигнатур и на инверсном выходе старшего разряда первого счетчика 5 не появятся О. В этом случае на выходе первого элемента ИЛИ 8 имеется О, который

0 прекращает прохождение через элемент И- НЕ 10 синхроимпульсов с синхровхода 13 анализатора.

В случае отсутствия ошибки (вектор ошибки равен нулю) первый счетчик 5 пре5 кращает изменять свое состояние тогда, когда на инверсном выходе старшего разряда первого счетчика 5 появляется О. При этом в остальных разрядах первого счетчика 5 находятся нули. Кроме того, на выходе

0 второго элемента ИЛИ 9 также имеется 0й. Таким образом, индикация всех нулей в блоках 7 и 18 означает отсутствие ошибок.

В случае одиночной ошибки вектор ошибки не равен нулю.

5 Так как образующие полиномы выбираются примитивными, то оба сигнатурных регистра в режиме генерации формируют предельное число комбинаций М 2 - 1. Дальнейшие рассуждения верны для обоих

0 формирователей сигнатур, поэтому в описании рассмотрен только один из них. Используя принцип суперпозиции, формирование сигнатуры ошибки можно рассматривать независимо от входной последовательно5 сти (ее правильных битов). Если ошибка была на 1-м такте последовательности, то при формировании сигнатуры ошибки (N тактов) и дальнейшем генерировании сигнатур (от N-ro такта до такта с номером 2k)

0 сигнатурный регистр последовательно принимает 2 - состояний, отличных друг от друга. При этом комбинация 1000 не учитывается, так как она будет учтена на последнем такте работы анализатора. Эти

5 комбинации имеют период М 2 -1 и начинают повторяться в определенной последовательности друг за другом. Учитывая, что сигнатура ошибки на t-м такте имеет вид 10000, генерация сигнатур продол жает0 ся далее до такта, на котором первый формирователь 1 сигнатур устанавливается в состояние 10000 и одновременно производится подсчет тактов, количество которых равно количеству оставшихся из предельно5 го числа отличных друг от друга комбинаций:

M-(2k-f)-(2k-1)-{2k-l)l-1. Учитывая это обстоятельство, первый счетчик 5 перед запуском анализатора устанавливается в начальное состояние 0001.

Так как все изложенное выполняется и для второго формирователя 2 сигнатур, то после остановки первого формирователя 1 сигнатур в случае однобитовой ошибки во втором формирователе 2 сигнатур имеется 5 также комбинации 10000, а следовательно, на выходе второго элемента ИЛИ 9 устанавливается уровень О.

Таким образом, состояние разрядов первого счетчика 5, кроме старшего, в конце 10 работы анализатора равно и индицируется на блоке 7. При этом нулевое состояние выхода второго элемента ИЛИ 9 является признаком наличия в последовательности тол ько одного ошибочного бита и отобража- 15 ется на индикаторе 18.

В случае наличия в последовательности более одного ошибочного бита после оста- новки первого формирователя 1 сигнатур во втором формирователе 2 сигнатур имеется 20

комбинация, отличная от 100....00 и 00000

(вероятность обратного очень мала), а следовательно, на выходе второго элемента ИЛИ 9 устанавливается уровень 1.

Формула изобретения Сигнатурный анализатор по авт. ев N 1383363, отличающийся тем, что, с целью повышения достоверности контроля, он содержит второй формирователь сигнатур, второй блок хранения эталонных сигнатур, индикатор и второй элемент ИЛИ, причем вход сброса второго формирователя сигнатур подключен к входу сброса анализатора, вход считывания второго блока хранения эталонных сигнатур подключен к входу Пуск анализатора, синхровход второго формирователя сигнатур подключен к выходу элемента И-НЕ, информационный вход второго формирователя сигнатур подключен к выходу первого элемента И, группа информационных выходов второго блока хранения эталонных сигнатур соединена с группой входов начальной установки второго формирователя сигнатур, входы второго элемента ИЛИ соединены с выходами всех разрядов, кроме первого второго формирователя сигнатур, выход второго элемента ИЛИ подключен к входу индикатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1383363A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор | 1984 |

|

SU1171797A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностики логических блоков. Цель изобретения - повышение достоверности контроля. Анализатор содержит два формирователя сигнатур, два блока хранения эталонных сигнатур, два счетчика, блок индикации, два элемента И, элемент И-НЕ, индикатор. Анализатор позволяет обнаружить номер ошибочного бита в контролируемой последовательности либо выявить факт наличия кратных ошибок. 1 ил.

| Сигнатурный анализатор | 1986 |

|

SU1383363A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-30—Публикация

1989-10-02—Подача